RECEPTION AND DECODING

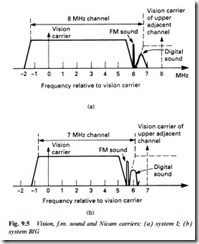

The processes at the receiving end are the inverse of those carried out by the Nicam encoder, applied in reverse order to recreate the L and R baseband audio signals which were present at the studio microphones. The take-off point for the Nicam carrier is at the output of the tuner of the TV set or videorecorder, where it appears as an i.f., typically at 32.95 MHz. This frequency is beat against the vision i.f. to produce an intercarrier frequency at Nicam carrier rate:

6.552 MHz for system I, 5.85 MHz for system B/G.

DQPSK demodulation

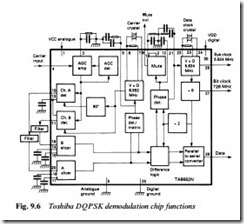

Fig. 9.6 shows an internal block diagram for a commercial DQPSK demodulator IC as used in domestic receivers. The Nicam carrier enters at pin 4 at a level of about 60 mV r.m.s. It passes through an a.g.c. control stage to maintain a reasonably constant input level to

a pair of detectors, A and B. They are arranged as synchronous demodulators working in quadrature, rather like the U and V detectors of the PAL decoder described in Chapter 7. Emerging from these are in-phase (cosine) and quadrature (sine) components of the phase- modulated carrier signal. They leave the IC on pins 10 and 11 for passage through separate but identical shaping filters whose characteristic is the same as those used at the DQPSK modulator at the transmitter. They remove harmonics and optimise the noise performance of the decoder.

The filtered quadrature signal components re-enter the chip on pins 19 and 20 for application to a pair of adaptive data slicers, A and B, whose operating points are held symmetrically about the signal’s mid- point. The data outputs from the slicers are applied to a matrix and

phase-locked-loop, PLL, to generate a synchronous c.w. feed for the detectors already described. The main path for the data signals is to a differential decoder, which uses a second PLL for sampling. It is here that 0 or 1 decisions are taken. The decoder output contains the bit pairs into which the data was grouped at the transmitter’s modulator. After passage through a 2-bit parallel to serial converter, the demodulated datastream emerges on IC pin 29 for application to the Nicam decoder proper.

The crystal oscillator in the second PLL in this IC runs at 5.824 MHz, eight times the bit rate of 728 kHz. Its output is divided by eight to provide: a bit clock drive for the following demultiplexer chip via pin 27; an internal drive for the P-S converter stage; and via a ÷2 stage a drive at 364 kHz for the differential decoder and the phase detector which steers the PLL. If the loop comes out of lock no coherent data can be detected and the mute output goes low on IC pin 18.

Demultiplex

The second main IC in this Nicam decoder is called a demultiplexer; it descrambles, de-interleaves and reformats the sound data to present

an output suitable for application to a conventional D-A converter system, along with the necessary clock and ident outputs. A typical demultiplexer IC is shown in block diagram form in Fig. 9.7. It has provision for fall-back switching to f.m., language selection, and control by direct line or serial data bus.

Data enters the IC on pin 23 wherefrom it takes two routes, one for signal and one for control. The latter starts with the FAW detector, consisting of an 8-bit serial register and comparator. Once the 01001110 FAW sequence is detected the PRSG generator is reset and started. Its synchronised output is added to the datastream to descramble all the bits which follow the FAW. The control bits are now routed to their own decoders to provide audio route switching and status indications for the user. The data proper passes outside the chip (pins 7/15) for interception if required, then to a serial to parallel converter whose 64 outputs consist of all the bits in two blocks of data. They are loaded into 64 × 11-bit memories in order to carry out the de-interleaving process, which consists of reading out from memory in the required order, controlled by an address sequencer governed in turn by the ROM-based interleaving code. Two memory banks are used, one being written as the other is read to render alternate A and B samples for stereo use. A third memory is incorporated for use with M1 and M2 (two mono, bi-lingual) transmissions where both are present in alternate blocks as shown in Fig. 9.3.

The 11-bit protected words, now descrambled and de-interleaved (but not yet error-corrected) must now be expanded back to 14-bit form. The scale factor information held in the parity bits is extracted, assembled and interrogated to control the data-expand stage, from which emerge 14-bit data words ready for error-correction and repair. This is carried out in the error-check block with reference to the parity bits for simple correction; and to the protection range data (conveyed by the range code) for more sophisticated error- concealment using interpolation, a process of replacing suspect data with locally generated samples derived by ‘averaging’ adjacent known- good samples.

Data leaves the IC on pin 3. It consists of alternate bursts of A and B (stereo L/R) information, defined by an ident (flip-flop) signal at pin 33, and a clock drive at pin 4. These three feeds go to the D−A converter stage from which the baseband signals will be reconstituted. The bit clock signal from the demodulator chip enters at pin 22 for use in the FAW detector. The main clock within the demux IC runs at 5.824 MHz and is also derived from the demodulator chip via pin 28: it is used throughout the Nicam decoding sections. A third clock signal, derived from the crystal at IC pins 11 and 12, provides a 16.384 MHz drive to the D−A converter.

Early designs of demultiplexer IC used external RAM for data interleaving, but all current types have on-board memories for this purpose, and work in broadly similar fashion to that described here.

D−A conversion

Conversion of the data back into analogue form is the final process in the Nicam decoder. The circuits and principles used are the same as those in audio CD players. In both cases the L and R audio information is contained in the same datastream, which alternates between the two.

Generally an integrating type of D−A converter is used. Its principle of operation is to charge a precision capacitor from a constant- current source for a period set by the data in each 14-bit word. A hold circuit is used to maintain the charge level between samples. Separate integrating capacitors are used for L and R channels, selected in turn by the L/R switching feed from the demultiplex chip. The outputs from the D−A converter now undergo filtering to remove sampling components and smooth the ‘stepped’ output waveform. In simple decoders the filters cut off sharply above 15 kHz; more sophisticated designs use oversampling with a smoother roll-off in the analogue filter, another technique widely used in CD players. This prevents distortion and coloration of audio signal components between 12 kHz and 15 kHz.

At the outset the L and R signals underwent pre-emphasis and now the complementary de-emphasis is applied to restore correct balance throughout the frequency spectrum and reduce noise. The L and R signals are now ready for audio amplification and application to loudspeakers in the case of a TV set, or processing for Hi-Fi recording in a VCR. All Nicam-fitted equipment has audio output sockets to facilitate connection to other units, most commonly a separate Hi-Fi system with good performance and high-class loudspeakers.

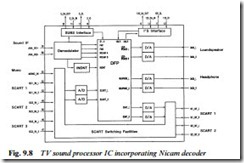

Fully integrated sound processor

Although the Nicam decoder system illustrated in Figs 9.6 and 9.7 is a good model for a functional description and understanding of the demodulation and decoding functions, it has been overtaken by various types of one-chip processors. That illustrated in Fig. 9.8 (MPS3410) provides a complete sound ‘package’, taking a sound i.f. input and producing stereo outputs for direct application to head- phone and loudspeaker amplifiers. Demodulation and filtering is performed in-chip and is programmable; the stereo outputs can be

controlled in terms of volume, balance, loudness, bass, treble and stereo ‘width’ enlargement, and can be made to produce pseudo stereo from a mono source, all governed from the control system via an I2C bus. F.m.-mono and f.m.-stereo (e.g. zweiton) transmissions are also catered for in this IC, and automatically selected in the absence of a Nicam signal.

There are two i.f. input pins (58 and 60), typically connected to terrestrial and satellite receiver sections respectively. Initially the input signals are A−D converted and a.g.c.-controlled before demodula- tion and application to the DFP (Digital Field Processing) block which contains demodulator and Nicam decoder; this performs all the functions described earlier in this chapter, including on-board D−A conversion.

Once the Nicam or f.m. signals have been restored to baseband form, their characteristics of volume, tone, balance etc. are control- led by I2C data. An important feature of this chip is its ability to select and control auxiliary audio inputs entering the set via SCART and phono sockets and hence the IC via its pins 46–55. Selection and control is again governed by the I2C bus; the selected input signals are A−D converted within the chip so that they can be manipulated and processed in the same way as the broadcast signals produced within the demodulator/decoder section of the device. In TV-standby mode the chip automatically defaults to ‘SCART- through’ mode to permit copying.