LINE TIMEBASE

As for the field section, the function of the line time base is to deflect the scanning spot of the picture-tube, and it has the same three basic building blocks of synchronised oscillator as timing source, shaping/ driver stage and power output amplifier. Line time base circuit designs are quite different to field ones, however, due to the much higher frequencies involved.

All line time bases which rely on CVBS-borne syncs incorporate flywheel synchronisation. Instead of using individual sync pulses to trigger each line scan, the frequency and phase of the locally generated line drive pulses are compared with those of the incoming sync pulses in a phase detector. Its error signal acts on the local oscillator to pull the two streams of pulses into phase-coincidence. This is another example of a phase-locked-loop, and here the time constant is chosen to be long compared with the period of one line; by this means the effect of interference or noise on incoming sync is minimised, since the triggering of any one scanning line is determined by the mean timing of many preceding line sync pulses.

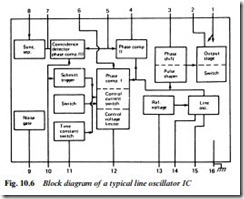

The arrangement of a representative IC containing sync separator, flywheel sync, line oscillator and noise suppression gate is shown in Fig. 10.6. The sync separator section contains a ‘slicing’ stage to strip away the video signal component of the CVBS waveform applied to pin 8. Pure sync signals emerge on pin 7, whence the field components

(long-duration pulses) are separated out by an integrator for application to the field oscillator. The short-duration line sync pulses alone are picked out by a differentiator feeding IC pin 6, where begins the business of line synchronisation. The IC has three control loops, each containing a phase comparator; the first is part of a PLL providing flywheel sync by comparing timings of line oscillator pulses and incoming sync pulses from pin 6. The error-output voltage from this first comparator (pin 12) passes through an external low-pass (flywheel) RC filter to re-enter the chip on pin 15 where it finely controls the oscillator frequency. Free-running oscillator frequency is governed by a close-tolerance capacitor at pin 14 and a potentiom- eter network (line hold control) at pin 15.

The second comparator examines the timing difference between flyback pulses from the line output transformer (applied at pin 5) and oscillator pulses. Its error output represents unwanted phase shift in the driver and output stage, which may vary with picture bright- ness etc., and is externally low-pass filtered between IC pins 4 and 3. At IC pin 3 this second control voltage operates on a phase shift/ pulse shaper section which corrects the phase of the oscillator output pulses. Phase-locked drive pulses emanate from pin 2 for onward pas- sage to the line driver stage, to be examined shortly. At this point the waveform is square, switching cleanly between two voltage levels and completing one cycle every 64 μs. Sawtooth waveshaping for the line scan coils is carried out further downstream – the function of this waveform is purely a switching one.

Mention must be made of the third comparator within the IC. This simply changes the characteristic time constant of the flywheel loop duration – which gives best noise-immunity in situations of high interference or weak received signal strength – to short duration, to facilitate rapid lock-in from the unsynchronised condition, as when changing r.f. channel. Provision is made for connection of an ‘AV’ switch to pin 10 to hold on the short time-constant mode for use with local signal sources whose CVBS signals contain timing jitter. This arises mainly in mechanically driven replay systems like video- cassette machines and disc players; a short time-constant in the line PLL enables the line oscillator to follow instantaneous variations in signal timing, and maintains correct positioning of the simultaneously jittering picture elements along each scanning line. The AV switch is electrically linked to an ‘AV-dedicated’ channel selector for automatic switchover. Many sets have a ‘standard’ flywheel time- constant short enough to permit good tape/disc reproduction without the necessity for switching.

Multifunction IC

The functions of time base generation, as well as many of the other sections examined in this and previous chapters, are embodied in the diagram of Fig. 7.7, reproduced here as Fig. 10.7 for convenience. The baseband video signal entering the chip on pin 13 or 17 is selected under I2C control by the switch near bottom centre of the diagram and passed up to the sync separator and first PLL, whose flywheel characteristic is given by the RC network at IC pin 43. It governs the frequency of the VCO in conjunction with a REF input; the oscillator output passes next through a second phase-control loop which advances or retards pulse timing (relative to sync) to compensate for picture-dependent delays in the line driver and output stages, working on a feedback pulse entering the chip on dual-purpose pin 41 – it also passes a sandcastle pulse out of the chip. The capacitor at pin 42 sets the time-constant for this second phase-lock-loop. The ‘hor out’ stage consists of a buffer to provide a low-impedance square- wave feed for the line driver transistor to which its output is routed, while the input at pin 50, coming from the ‘bottom-end’ of the EHT generator, has two functions: to provide breathing compensation for both line and field scans; and to shut down the line scan stage in the event of excessive e.h.t. voltage, sometimes known as X-ray protection. It is invoked when pin 50 rises above 3.9 V.

While in this chip it is instructive to look at the field scan sync and driver arrangements. The H/V divider near top right of the diagram counts line pulses to produce the vertical flyback trigger – one of the latter every 612.5 of the former, checked, timing-wise, by pulses com- ing from the vertical sync separator. Its output is processed in the vertical geometry correction block, where picture-height and linear- ity control, also S-correction, are applied according to I2C data entering the IC on pins 7 and 8. These values are preset and held in EEPROM memory: more details in Chapter 22. Pin 51 of the chip couples the sawtooth-charging capacitor whose value is typically 100 nF. Emerging on pins 46 and 47 are positive and negative saw- tooth field drive waveforms for passage to a yoke-drive IC like that illustrated in Fig. 10.4.