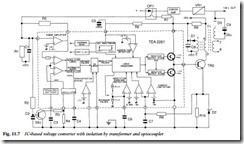

BURST-MODE PSU CHIP

An alternative and later type of PSU regulator IC (TEA2261) is illustrated in Fig. 11.7, with its external circuit drawn around it in skeleton form. When mains voltage is applied a full-wave bridge rectifier and reservoir capacitor provide a 320 V supply at the right-hand side of R9: it affords a +8 V supply to IC pins 15 and 16, sufficient to get the chip started. The oscillator at IC pins 10 and 11 begins to run at about 10 kHz, timed by R4 and C4, and so drive pulses appear at pin 14 – they are very narrow initially. On each pulse, chopper transistor TR2 pulls current through T1 primary winding 3–4 and the reservoir capacitors at its secondary windings begin to charge. As C3 at IC pin 9 charges up, the duty-cycle of TR2’s drive pulse train increases: a ‘soft-start’ effect. The voltage developed at T1 winding 1–2 charges C8 to about 12 V, whereupon this supply supersedes that coming via R9 to power the chip. Meanwhile C2 is being charged via R7, OP1 and R2, and when it attains about 600 mV TR1 switches on to put R3 in parallel with R4, resulting in a rise in oscillator frequency to about 40 kHz, its normal running frequency.

Now the pulse levels on the secondary windings of T1 (here represented by coil 7–8) rise to about their normal levels and the regulation circuit comes into operation, based on the feedback to chip pin 6 from D1 and C8 via R7 and OP1. If this voltage rises, the width of the pulses fed to TR2 becomes narrower to compensate, and thus regulation is achieved in a coarse way. To achieve fine regula- tion of the voltage to the line output stage (developed at C9) a second feedback circuit is provided to give ‘tighter’ control. The 130 V line is ‘potted down’ in a network incorporating preset VR1 and passed into an error-amplifier transistor (top RHS of Figure 11.6) whose collector current flows through the LED in optocoupler OP1. A rise in 130 V line voltage increases conduction in the error amplifier and the LED, resulting in a fall in resistance of the phototransistor in OP1. The effect of this is to increase the voltage at IC pin 6, thus turning down the wick, as it were, and restoring the 130 V line to its correct level. If the 130 V line potential should fall – typically when the picture brightens – the control loop works to pull it back up to normal.

Fault protection

Protection from excessive current (in the loads and in the PSU itself) is based on the action of low-value sampling resistor R10 in the emitter lead of chopper transistor TR2. In normal operation the voltage developed across R10, and applied through R8 to pin 3 of the control IC, has no effect on the running of the latter. An increased chopper current produces sufficient voltage at IC pin 3 to trigger the first threshold detector (0.6 V) within the IC, resulting in a narrowing of the output pulse width at drive pin 14 and a corresponding reduction in voltage – hence current – in all the secondary loads. This over- rides the voltage-regulator system to hold the set in a limited current mode which is maintained for as long as the overload is present. A very heavy current overload, such as may result from a short-circuit line output transistor, forces up the voltage across R10 to the point where a second threshold detector within the IC (0.9 V) is triggered. Now more drastic action is taken: the base drive to TR2 is deleted, shutting down the PSU, and C6 on IC pin 8 acquires a charge. Conditions are sampled again by restarting the drive to TR2, and if the overload is still present the drive stops again and C6 charge is increased. This cycle takes place a few times more, giving a characteristic ‘pumping’ effect, until a certain level of charge on C6

is reached, when the IC shuts down completely. At this point the only way to restart the system is to switch the set off, leave time for C6 to fully discharge, then switch on again. Zener diode D2 is there to protect R10, R8 and the IC from the effect of a dead-short in chop- per transistor TR2: if that should happen, the heavy current and high voltage would break down the 3 V device to a short circuit, completing a low-resistance path across the mains bridge rectifier and blowing the mains fuse.

Excessive voltage output from the PSU section must also be anticipated and protected against to maintain safety standards. In the circuit of Fig. 11.7 the overvoltage protection operates via IC pin 6, already used for voltage stabilisation, whereby a rising voltage here narrows the chopper drive pulses. If, in spite of this, the potential of the 130 V line at C9 continues to rise, its reflection at IC pin 6 removes the chopper drive momentarily, resulting in a collapse of voltage at C9 and a consequent fall of IC pin 6 voltage. This, via the chip, restores chopper drive, and if the overvoltage is still present the trip action is repeated, continuing indefinitely while conditions remain abnormal. A further artifice is built into the IC to guard against an open-circuit in the regulator feedback loop to IC pin 6. Contained in the overvoltage op-amp near top centre of the diagram, it monitors the voltage at IC pin 16. Normally running at about 12 V, a rise to 16 V here indicates loss of control, whereupon the chip charges C6 to shutdown level and cuts off at once, without the pump-cycling effect of a current overload. Again it is necessary to switch off the set and wait for C6 to discharge before trying again.

Burst mode

When the TV set is switched to stand-by the line drive is deleted so that the line output stage goes dormant. Sound and vision go off, and relieved of its load, the PSU output voltage rises to the point where the excess-voltage protection is invoked within the chip as described above. The result is a continual tripping of the PSU, with the secondary voltages cycling up and down at about 100 Hz rate. This goes on all the time the set is in stand-by: it is called burst mode, and provides sufficient power to maintain the supply to the control microprocessor (now looking for an ‘on’ command from the remote control) and the EEPROM memory chip.