Synchronous Serial Interfaces (SPI, I2C, Microwire)

There are two very common synchronous data protocols, Microwire and SPI, from which a variety of standard devices (memory and peripheral functions) have been designed around, including serial EEPROMs, sensors and other I/O functions. I consider these protocols to be methods of transferring synchronous serial data rather than intelligent network protocols because each device is individually addressed (even though the clock/data lines can be common between multiple devices). If the chip select for the device is not asserted, the device ignores the clock and data lines. With these protocols, only a single ‘‘Master’’ can be on the bus. Normally, just eight bits of data are sent out at a time. For protocols like Microwire where a ‘‘Start bit’’ is initially sent, the ‘‘Start bit’’ is sent using direct reads and writes to the I/O pins. To receive data, a similar circuit would be used, but data would be shifted into the shift register and then read by the microcontroller.

The Microwire protocol is capable of transferring data at up to one megabit per second. Sixteen bits are only transferred at a time. After selecting a chip and sending a start bit, the clock strobes out an eight bit command byte, followed by (optionally) a 16 bit address word transmitted and then another 16 bit word either written or read by the microcontroller.

With a one megabit per second maximum speed, the clock is both high and low for 500 ns. Transmitted bits should be sent 100 ns before the rising edge of the clock. When reading a bit, it should be checked 100 ns before the falling edge of the clock. While these timings will work for most devices, you should make sure you understand the requirements of the device being interfaced to.

The SPI protocol is similar to Microwire, but with a few differences:

1. SPI is capable of up to 3 megabits per second data transfer rate.

2. The SPI data ‘‘word’’ size is eight bits.

3. SPI has a ‘‘Hold’’ which allows the transmitter to suspend data transfer.

4. Data in SPI can be transferred as multiple bytes known as ‘‘Blocks’’ or ‘‘Pages’’.

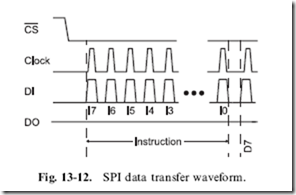

Like Microwire, SPI first sends a byte instruction to the receiving device. After the byte is sent, a 16 bit address is optionally sent followed by eight bits of I/O. As noted above, SPI does allow for multiple byte transfers. An SPI data transfer is shown in Fig. 13-12. The SPI clock is symmetrical (an equal low and high time). Output data should be available at least 30 ns before the clock line goes high and read 30 ns before the falling edge of the clock.

When wiring up a Microwire or SPI device, one trick that you can do to simplify the microcontroller connection is to combine the ‘‘DI’’ and ‘‘DO’’ lines into one pin, as was shown earlier in the book.

The most popular form of microcontroller network is ‘‘I2C’’, which stands for ‘‘Inter-Intercomputer Communications’’. This standard was originally developed by Philips in the late 1970s as a method to provide an interface between microprocessors and peripheral devices without wiring full address, data and control busses between devices. I2C also allows sharing of network resources between processors (which is known as ‘‘Multi-Mastering’’). Your PC probably has several I2C busses built into it for controlling system control and monitoring functions.

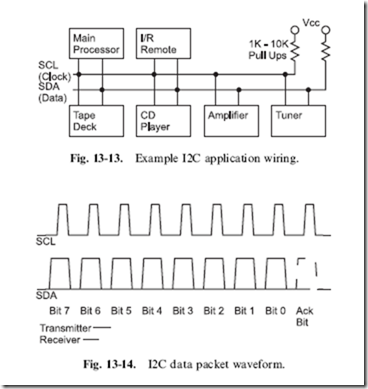

The I2C bus consists of two lines: a clock line (‘‘SCL’’) which is used to strobe data (from the ‘‘SDA’’ line) from or to the master that currently has control over the bus. Both these bus lines are pulled up (to allow multiple devices to drive them). A I2C controlled stereo system might be wired as shown in Fig. 13-13.

The two bus lines are used to indicate that a data transmission is about to begin as well as pass the data on the bus. To begin a data transfer, a ‘‘Master’’ puts a ‘‘Start Condition’’ on the bus. Normally, when the bus is in

the ‘‘Idle State’’, both the clock and data lines are not being driven (and are pulled high). To initiate a data transfer, the master requesting the bus pulls down the SDA bus line followed by the SCL bus line. During data transmission this is an invalid condition (because the data line is changing while the clock line is active/high). Each bit is then transmitted to or from the ‘‘Slave’’ (the device the message is being communicated with by the ‘‘Master’’) with the negative clock edge being used to latch in the data. To end data transmission, the reverse is executed; the clock line is allowed to go high, which is followed by the data line.

Data is transmitted in a synchronous (clocked) fashion. The most

significant bit is sent first and after eight bits are sent, the master allows the data line to float (it doesn’t drive it low) while strobing the clock to allow the receiving device to pull the data line low as an acknowledgment that the data was received. After the acknowledge bit, both the clock and data lines are pulled low in preparation for the next byte to be transmitted or a Stop/ Start Condition is put on the bus. Fig. 13-14 shows the data waveform.

Sometimes, the acknowledge bit will be allowed to float high, even though the data transfer has been completed successfully. This is done to indicate that the data transfer has completed and the receiver (which is usually a ‘‘slave device’’ or a ‘‘Master’’ which is unable to initiate data transfer) can prepare for the next data request.

There are two maximum speeds for I2C (because the clock is produced by a master, there really is no minimum speed). ‘‘Standard Mode’’ runs at up to 100 kbps and ‘‘Fast Mode’’ can transfer data at up to 400 kbps.

Asynchronous Serial Interfaces

Understanding how asynchronous serial communications works is easy; implementing them on a PC is frustrating and hard and used to be especially true for casual PC owners. This situation is improving with newer high-speed interface connection protocols (USB and Firewire), but actually sitting down and getting RS-232 communication between two devices working can be a pain. Much of the information I will present on RS-232 in this section will seem quite obvious, but I urge you to read through this material as there are some tricks and information contained here that could probably get you out of a bind or two.

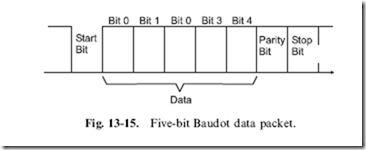

Asynchronous long distance communications came about as a result of the Baudot ‘‘teletype’’. This device mechanically (and, later, electronically) sent a string of electrical signals (which we would call ‘‘bits’’), like the one shown in Fig. 13-15, to a receiving printer. This data packet format is still used today for the electrical asynchronous transmission protocols described in the following sections. With the invention of the teletype, data could be sent and retrieved automatically without having an operator having to sit by the teletype all night unless an urgent message was expected.

The Baud Rate specified for the data transmission is the maximum number of possible data bit transitions per second (measured in ‘‘bits per second’’, abbreviated to ‘‘bps’’). This includes the ‘‘Start’’, ‘‘Parity’’ and ‘‘Stop’’ bits at the ends of the data ‘‘packet’’ shown in Fig. 13-15 as well as the five data bits

in the middle. I use the term ‘‘packet’’ because we are including more than just data (there is also some additional information in there as well), so ‘‘character’’ or ‘‘byte’’ (if there were eight bits of data) are not appropriate terms. This means that for every five data bits transmitted, eight bits in total are transmitted (which means that nearly 40% of the data transmission bandwidth is lost in teletype asynchronous serial communications).

The ‘‘Data Rate’’ is the number of data bits that are transmitted per second. For this example, if you were transmitting at 110 baud, the actual data rate is 68.75 bits per second (or, assuming five bits per character, 13.75 characters per second).

With only five data bits, the Baudot code could only transmit up to 32

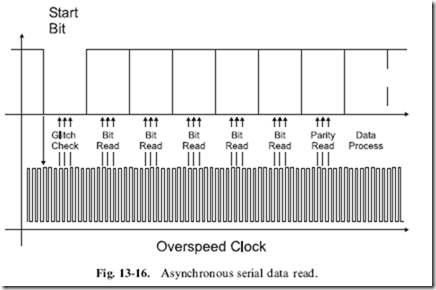

distinct characters. To handle a complete character set, a specific five-digit code was used to notify the receiving teletype that the next five-bit character would be an extended character. With the alphabet and most common punctuation characters in the ‘‘primary’’ 32, this second data packet wasn’t required very often. In the data packet shown in Fig. 13-15, there are three control bits. The ‘‘Start Bit’’ is used to synchronize the receiver to the incoming data. In most hardware circuits designed to read an asynchronous serial packet, there is an overspeed clock running at 16 times the incoming bit speed which samples the incoming data and verifies whether or not the data is valid. When waiting for a character, the receiver hardware polls the line repeatedly at 1/16 bit period intervals until a ‘‘0’’ (‘‘Space’’) is detected (down arrow at the left of Fig. 13-16). The receiver then waits half a cycle before

polling the line again to see if a ‘‘glitch’’ was detected and not a Start bit. This polling takes place in the middle of each bit to avoid problems with bit transitions (or if the transmitter’s clock is slightly different from the receivers, the chance of misreading a bit will be minimized).

Once the Start bit is validated, the receiver hardware polls the incoming data once every bit period multiple times (again to ensure that glitches are not read as incorrect data).

The ‘‘Stop’’ bit was originally provided to give both the receiver and the transmitter some time before the next packet is transferred (in early computers, the serial data stream was created and processed by the computers and not custom hardware, as in modern computers).

The ‘‘Parity’’ bit is a crude method of error detection that was first brought in with teletypes. The purpose of the parity bit is to indicate whether the data was received correctly. An ‘‘odd’’ parity meant that if all the data bits and parity bits set to a ‘‘Mark’’ were counted, then the result would be an odd number. ‘‘Even’’ parity is checking all the data and parity bits and seeing if the number of ‘‘Mark’’ bits is an odd number. Along with even and odd parity, there are ‘‘Mark’’, ‘‘Space’’ and ‘‘No’’ parity. ‘‘Mark’’ parity means that the parity bit is always set to a ‘‘1’’, ‘‘Space’’ parity is always having a ‘‘0’’ for the parity bit and ‘‘No’’ parity is eliminating the parity bit all together. I said that parity bits are a ‘‘crude’’ form of error detection because they can only detect one bit error (i.e. if two bits are in error, the parity check will not detect the problem). If you are working in a high induced noise environment, you may want to consider using a data protocol that can detect (and, ideally, correct) multiple bit errors.

The most common form of asynchronous serial data packet is ‘‘8-N-1’’, which means eight data bits, no parity and one stop bit. This reflects the capabilities of modern computers to handle the maximum amount of data with the minimum amount of overhead and with a very high degree of confidence that the data will be correct.

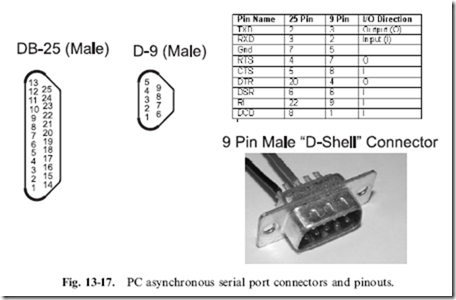

Having reviewed the data protocol for asynchronous serial communications, let’s go on and look at the electrical specifications, starting with the connectors that you will find on the back of your PC (Fig. 13-17). Either a male 25 pin or male 9 pin connector is available on the back of the PC for each serial port – chances are you will have a 9 pin connector because it takes up the least amount of space.

Working with MS-DOS in early systems, only a maximum of four serial ports could be addressed by the PC, and of these probably only two were useable for connecting external devices to the PC due to conflicts with other hardware devices. In modern systems, which have ‘‘Plug and Play’’ capabilities and the Windows operating system, which can allocate resources

throughout the system, the number of standard serial ports has been greatly expanded. My personal record is 64 serial devices for environmental chamber status test software.

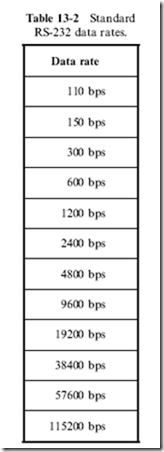

The standard RS-232 data rates available to you in the PC are listed in Table 13-2. As an interesting exercise, I suggest that you find the reciprocal of the data rates listed in Table 13-2, multiply by 1,000,000 and then divide by 13 – what you will find is that the results for the data rates starting at 1200 bps and going higher will have a very small fraction. In fact, the error will be much less than 0.1%! This is a good trick to keep in your hip pocket when you have to implement an RS-232 interface and you don’t have any crystals that have been cut specifically to provide a multiple of these data rates.

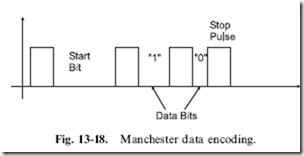

Asynchronous communications based on the Baudot teletype/RS-232 is known as ‘‘Non-Return to Zero’’ (‘‘NRZ’’) asynchronous communications, because at the end of each data packet the serial line is high. There are other methods of sending asynchronous serial data, with one of the most popular being ‘‘Manchester encoding’’. In this type of data transfer, each bit is synchronized to a ‘‘start’’ bit and the following ‘‘Data Bits’’ are read with the ‘‘space’’ dependent on the value of the bit.

Manchester encoding is unique in that the ‘‘Start Bit’’ of a packet is quantitatively different from a ‘‘1’’ or a ‘‘0’’ (shown in Fig. 13-18). This allows a receiver to determine whether or not the data packet being received is actually at the start of the packet or somewhere in the middle (and should be ignored until a start bit is encountered).

Manchester encoding is well suited for situations where data can be easily interrupted or there is a conflict in the middle of data reception. Because of this, it is the primary method of data transmission for infrared control (such as used in your TV’s remote control).

RS-232 Electrical Standards

In the previous section, I didn’t tell the whole story about RS-232 asynchronous serial communications. I left out one very important point – signals do not travel at the same voltage levels as what we’ve discussed so far in the book. When RS-232 was first developed into a standard, computers and the electronics that drive them were still very primitive and unreliable. Because of that, we’ve got a couple of legacies to deal with and this can complicate connecting digital electronics circuits to another device using RS-232.

The biggest concern is the voltage levels of the data. A ‘‘Mark’’ (‘‘1’’)

is specified to be -3 volts to -12 volts and a ‘‘Space’’ (‘‘0’’) is þ3 volts to þ12 volts. This means that there must be some kind of voltage level conversion when passing RS-232 to or from digital electronic devices. There are a number of ways of doing this.

Before working with the voltage levels, I just want to say a few words about the ‘‘handshaking’’ signals built into RS-232 (these are all the RS-232 connections other than RX, TX and GND in Fig. 13-17). These six additional lines (which are at the same logic levels as the transmit/receive lines) are used to interface between devices and control the flow of information between computers.

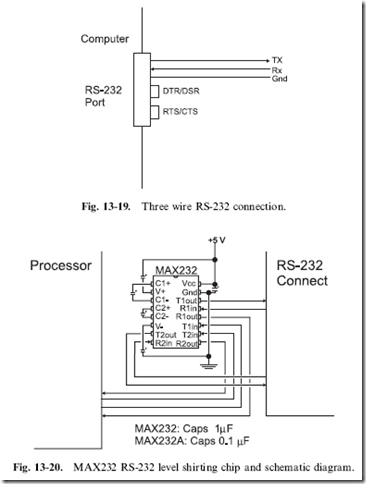

The ‘‘Request To Send’’ (‘‘RTS’’) and ‘‘Clear To Send’’ (‘‘CTS’’) lines are used to control data flow between the computer (‘‘DCE’’) and the modem (‘‘DTE’’ device). The ‘‘Data Transmitter Ready’’ (‘‘DTR’’) and ‘‘Data Set Ready’’ (‘‘DSR’’) lines are used to establish communications. There are two more handshaking lines that are available in the RS-232 standard that you should be aware of, even though chances are you will never connect anything to them. The first is the ‘‘Data Carrier Detect’’ (‘‘DCD’’), which is asserted when the modem has connected with another device (i.e. the other device has ‘‘picked up the phone’’). The ‘‘Ring Indicator’’ (‘‘RI’’) is used to indicate to a PC whether or not the phone on the other end of the line is ringing or if it is busy. Few of these lines are used in modern RS-232 applications and, as shown in Fig. 13-19, the DTR/DSR and CTS/RTS pairs are often simply shorted together to avoid any ‘‘hardware handshaking’’ issues with the PC. There is a common ground connection between the DCE and DTE devices. This connection is critical for the RS-232 level converters to determine the actual incoming voltages. The ground pin should never be connected to a chassis or shield ground (to avoid large current flows or be shifted and prevent accurate reading of incoming voltage signals). Incorrect grounding of an application can result in the computer or the device it is

interfacing having to reset or have they power supplies blow a fuse or burn out. The latter consequences are unlikely, but I have seen it happen in a few cases. To avoid these problems make sure that chassis and signal grounds are separate or connected by a high value (hundreds of k Q) resistor.

The most popular method for converting TTL/CMOS Logic signals to RS-232 levels is to use the MAXIM MAX232 (see Fig. 13-20,) which has a built in charge-pump voltage generator. This chip is ideal for implementing three-wire RS-232 interfaces (or to add a simple DTR/DSR or RTS/CTS handshaking interface). Ground for the incoming signal is normally connected to the digital electronics ground. Along with the MAX232,

MAXIM and some other chip vendors have a number of other RS-232 charge-pump equipped devices that will allow you to handle more RS-232 lines (to include the handshaking lines). Some charge-pump devices that are also available do not require the external capacitors that the MAX232 chip does, which will simplify the layout of your circuit (although these chips do cost quite a bit more).

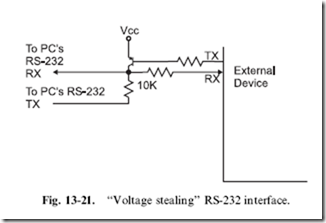

The next method of translating RS-232 and TTL/CMOS voltage levels is to use the transmitter’s negative voltage as the circuit, as Fig. 13-21 shows.

This circuit relies off of the RS-232 communications, only running in ‘‘Half- Duplex’’ mode (i.e. only one device can transmit at a given time). When the external device wants to transmit to the PC, it sends the data either as a ‘‘Mark’’ (leaving the voltage being returned to the PC as a negative value) or as a ‘‘Space’’ by turning on the transistor and enabling the positive voltage output to the PC’s receivers. If you go back to the RS-232 voltage specification drawing, you’ll see that þ5 volts is within the valid voltage range for RS-232 ‘‘Spaces’’. This method works very well (consuming just about no power) and is obviously a very cheap way to implement a three-wire RS-232 bi-directional interface. There is a chip, the Dallas Semiconductor DS275, which incorporates the circuit above (with a built-in inverter) into the single package shown, making the RS-232 very simple.

Before finishing, I want to make a final point on three wire RS-232 connections. The first is that it cannot be implemented blindly; in about 20% of the RS-232 applications that I have had to do over the years, I have had to implement some subset of the total seven wire (transmit, receive, ground and four handshaking lines) protocol lines. Interestingly enough, I have never had to implement the full hardware protocol. This still means that four out of five times if you wire the connection as shown in Fig. 13-19, the application would have worked.

1. Which type of memory responds in the least amount of time?

(a) Processor cache

(b) All three types respond equally fast

(c) Main Memory (S)DRAM

(d) Processor ROM

2. What is not a characteristic of a computer bus?

(a) Controlled by a central processor

(b) The ability of peripherals on the bus to request information

(c) Data can be read/written to peripheral busses

(d) Keeping a log of the processor bus accesses

3. The minimum timing between signal edges in the parallel port is:

(a) 0.5 ms

(b) 0.5 ms

(c) 0.5 ns

(d) There are no delays; the port works completely asynchronously

4. The raster display on a video display looks like:

(a) A series of parallel lines going across the display

(b) Parallel lines that loop back like plough lines in a farmer’s field

(c) A series of small dots drawn on the video display

(d) A series of brush strokes on the video display

5. ‘‘Horizontal synch’’ in a video display:

(a) Moves the electron beam in the CRT to the left

(b) Moves the electron beam in the CRT to the top

(c) Starts the raster going side to side

(d) Is needed for CRTs laid down on their side

6. Devices on a synchronous serial bus are normally referred to as:

(a) ‘‘Dominant’’ and ‘‘Recessive’’

(b) ‘‘Master’’ or ‘‘Slave’’

(c) ‘‘1’’ or ‘‘0’’

(d) ‘‘Transmitter’’ or ‘‘Receiver’’

7. The maximum speed of the ‘‘SPI’’ synchronous serial protocol is:

(a) 100 kpbs (thousands of bits per second)

(b) 1 Mbps (millions of bits per second)

(c) 2 Mbps

(d) 3 Mbps

8. To connect to a modern PC’s RS-232 connector, you will need:

(a) Fiber optic cable

(b) 75 Ohm Coax and BNC connector

(c) RJ-45 cable and crimper

(d) A 9 pin male D-Shell connector

9. The RS-232 voltage levels of -12 volts for a ‘‘1’’ and þ12 volts for ‘‘0’’ means that:

(a) You can connect digital electronics devices directly to RS-232 connections

(b) You can connect TTL/CMOS Logic drivers directly to RS-232

(c) You can connect TTL/CMOS Logic inputs directly to RS-232

(d) You cannot connect digital electronics devices directly to RS- 232 connections

10. The MAX232:

(a) Uses a charge pump to power the circuit

(b) Requires þ12 volts and -12 volts to convert TTL/CMOS Logic signals

(c) Produces correct RS-232 voltages and converts TTL/CMOS Logic signals

(d) Will allow a full RS-232 connection with only one chip