Test On Digital Electronics Applications

Do not refer to the text when taking this test. You may draw diagrams or use a calculator if necessary. A good score is at least 38 correct answers. Answers are in the back of the book. It’s best to have a friend check your score the first time so you won’t memorize the answers if you want to take the test again.

1. A signal with a 100 ns time ‘‘On’’ and a 230 ns time ‘‘Off’’ has a frequency of:

(a) 30.3%

(b) 3 GHz

(c) 3 MHz

(d) 3 kHz

2. A toggle flip flop will divide a clock frequency by:

(a) The value selected in its inputs

(b) 2

(c) 1.5, but the output duty cycle is 50%

(d) The toggle flip flop is used for debouncing switch inputs

3. The NPN transistor relaxation oscillator is well suited for:

(a) High-speed computer applications

(b) Only audio applications

(c) Low-cost applications where accuracy isn’t important

(d) Power supply duty cycle generators

4. If you wanted an oscillator that produced a period of 4 gate delays, you would:

(a) Use a standard ring oscillator

(b) Use something other than a ring oscillator

(c) Use two three inverter ring oscillators and XOR their outputs

(d) Use a two inverter ring oscillator and divide the output frequency by two using a toggle D flip flop

5. The duty cycle of a ring oscillator is:

(a) Always 50%

(b) Equal to the number of inverters used in the ring oscillator multiplied by the gate delay

(c) Dependent on the technology used in the inverters

(d) Always 100%

6. Why are TTL inverters not recommended for relaxation oscillators?

(a) They are too costly

(b) They do not operate at a fast enough speed

(c) Their current controlled inputs will affect the operation of the oscillator

(d) They may short out internally when used as part of an oscillator.

7. A relaxation oscillator has an R1 value of 1k, C of 0.1 mF and R2 equal to 10 k. What frequency will it oscillate at?

(a) It won’t oscillate

(b) 4.54 kHz

(c) 4.54 MHz

(d) 4.54 Hz

8. Crystals used in oscillators are:

(a) Relatively high cost but very accurate

(b) Very robust and immune to shock damage

(c) Low cost with an accuracy that is similar to that of a ‘‘canned oscillator’’

(d) Mined in South America

9. The crystal inverter circuit requires the following parts:

(a) Crystal and inverter

(b) Crystal, inverter, two capacitors and two resistors

(c) Crystal, inductor, three resistors, two capacitors and an NPN transistor

(d) Crystal, diode, two capacitors, hand wound coil, two diodes

10. Changing the voltage at the ‘‘Vcontrol’’ pin of a 555 astable oscillator:

(a) Will change the period of the oscillator output

(b) Won’t change anything

(c) Will lower the amount of power consumed

(d) Will add unnecessary costs to the circuit

11. A 555 astable oscillator with R1 ¼ 47 k, R2 ¼ 100 k and C ¼ 4.7 mF will oscillate at:

(a) 805 Hz

(b) 0.805 Hz

(c) 1.24 Hz

(d) 1.24 kHz

12. Decreasing value of a resistor or capacitor in a 555 monostable will:

(a) Lower its operating frequency

(b) Raise its operating frequency

(c) Increase the pulse width

(d) Decrease the pulse width

13. A chip with two 555 timers built in has the part number: (a) 75555

(b) 556

(c) No such chip exists

(d) 2×555

14. The delay in a ‘‘canned delay line’’ is produced by:

(a) Elves

(b) A piece of quartz, cut to provide a specified delay

(c) A long piece of copper wire, formed as a coil

(d) A large array of simple gates

15. Why is reset passed to the ‘‘Output Formatter’’ in the sequential circuit block diagram?

(a) To control the operation of tri-state drivers built into the ‘‘Output Formatter’’

(b) To synchronize outputs with the operation of the chip

(c) To minimize power usage when the chip is reset

(d) To speed up operation of the sequential circuit

16. To create a cascaded counter from multiple chips, what signal(s) are passed between the chips?

(a) The most significant two bits

(b) The ‘‘Carry’’ from the least significant counter and the ‘‘Borrow’’ from the more significant counter

(c) Just the carry from the least significant counter to the clock input of the more significant counter

(d) The clock and chip enable signals to be shared between the two counters

17. What are the disadvantages of serial data transmission over parallel data transmission?

(a) Increased product chip count

(b) Slower data transmission

(c) Increased product power requirements

(d) Increased data error rate

18. The linear feedback shift register polynomial defines:

(a) The XOR ‘‘taps’’ used to modify the incoming data

(b) The execution order of magnitude

(c) The value needed to decode any value run through the LFSR

(d) The relationship between the number of bits and speed of the LFSR’s operation

19. The number of states and inputs in a hardware state machine are a function of:

(a) The fanout capabilities of the chips used

(b) The number of discrete states required

(c) The requirements of the application

(d) The size of the ROM used

20. Since commands to a Hitachi 44780 controlled LCD require 160 ms or more to execute, what is an effective way of waiting the suggested delay before sending the next command?

(a) Using a 555 timer wired as a monostable

(b) Passing requests to the LCD through an RC delay

(c) Polling the busy flag

(d) Using a clock with a 5 ms period

21. What signal is not included in a typical sequential logic circuit interface bus?

(a) _Read

(b) Data Read Ready

(c) _Write

(d) Address Bit 0

22. A ‘‘three to eight’’ decoder:

(a) Cannot be implemented in TTL or CMOS Logic

(b) Converts three data selects into eight device read requests

(c) Converts three clock cycles into eight state machine addresses

(d) Converts three binary bits into eight interface device selects

23. The segments to be turned on in a seven-segment LED display is determined by:

(a) A circuit which enables the common cathodes or common anodes in the LED displays

(b) A microprocessor built into each seven-segment LED display

(c) A combinatorial circuit performing Boolean arithmetic operations on the display bits

(d) A sequential circuit that compares the display bits to expected values

24. A PWM with a period of 10 ms and a ‘‘high’’ signal of 4 ms has a duty cycle of:

(a) Not enough information is available to determine the duty cycle

(b) 60%

(c) 0.4

(d) 40%

25. To produce a PWM output signal of 20 kHz and have 6 bits of accuracy, what input clock frequency should be used?

(a) 20 kHz

(b) 64 Hz

(c) 1.28 MHz

(d) 5.1 MHz

26. The two inverter debounce circuit is best suited for what kind of input devices?

(a) Push buttons

(b) 40%

(c) 0.4

(d) Double throw switches

27. Hysteresis causes logic inputs to be registered:

(a) Faster than normal inputs

(b) At lower thresholds than devices with standard inputs

(c) At more extreme thresholds than devices with standard inputs

(d) When there is an inductor on the line

28. A switch matrix keypad is:

(a) Used by Trinity and Neo to access the Matrix

(b) A two-dimensional array of switches used to provide multiple button inputs

(c) A series of switches that change the output signal of a

sequential circuit

(d) The natural evolution of a single button to multiple buttons

29. The Princeton architecture was criticized because:

(a) The single memory interface was felt to be a performance bottleneck

(b) It relied too heavily on vacuum tube technology

(c) The design was taken from other, earlier computer designers

(d) The amount of space required for it seemed to be prohibitive

30. The first digit to the right of the decimal point in a binary floating point number has a value of:

(a) 0.1 decimal

(b) 0.25 decimal

(c) 0.5 decimal

(d) 1.0 decimal

31. Floating point numbers are stored in data size except:

(a) 2 bytes

(b) 4 bytes

(c) 8 bytes

(d) 10 bytes

32. SRAM memory is best suited for applications which require:

(a) Data stacks

(b) Gigabytes of memory

(c) Mass storage of data

(d) Fast data access for a relatively large memory area

33. Stacks cannot be modeled by:

(a) Trays in a lunchroom

(b) Pieces of paper on a person’s desk

(c) Stacks of paper produced by a computer processor

(d) A jelly bean jar

34. The operation of the Zener regulator is analogous to:

(a) A car’s carburetor

(b) A bowl with a hole cut in the bottom

(c) A PWM output driven by a comparator

(d) A comparator output driven by sensor

35. The operation of the linear regulator is analogous to:

(a) A car’s carburetor

(b) A bowl with a hole cut in the bottom

(c) A PWM output driven by a comparator

(d) A comparator output driven by sensor

36. A 10:1 transformer has an input of 110 volts AC. What is its output?

(a) 11 volts DC

(b) 11 volts AC

(c) 110 volts DC

(d) 11 amps AC

37. ‘‘PAL’’ I/O pins are:

(a) Input and Output

(b) Programmable Input or Output

(c) Input only

(d) Output only

38. What is not a ‘‘local memory’’ device:

(a) Processor cache

(b) PCI status registers

(c) Main memory (S)DRAM

(d) Processor ROM

39. The Logic levels for the PC’s parallel port are?

(a) 3.3 volt CMOS Logic compatible

(b) 5 volt TTL/CMOS Logic compatible

(c) 5 volt ‘‘HCT’’ Logic compatible

(d) Current controlled, voltage levels are not considered

40. The inventor of the parallel port pinout standard was:

(a) IBM

(b) Apple Computers

(c) The Centronics Corporation

(d) Xerox FARC

41. The ‘‘Data’’ bits of the PC’s parallel port have what kind of outputs?

(a) Discrete transistors

(b) CMOS totem pole outputs

(c) Pulled up Open Collectors that can be changed by external

devices

(d) TTL tri-state buffers

42. ‘‘Vertical synch’’ in a video display:

(a) Moves the electron beam in the CRT to the left

(b) Moves the electron beam in the CRT to the top

(c) Starts the raster going up and down

(d) Is needed for CRTs pointing upwards

43. The ‘‘NTSC’’ video standard was first developed for:

(a) Military radar screens

(b) Portable news gathering services

(c) Electronic instruments

(d) Televisions

44. The ‘‘Microwire’’ synchronous serial protocol sends:

(a) A word consisting of 16 bits of data

(b) A word consisting of 8 bits of data

(c) Status Information before Data

(d) Command Information before Data

45. I2C’s ‘‘Acknowledge’’ bit:

(a) Is used as a ‘‘Parity Bit’’ for Received Data

(b) Indicates the Received Data was Valid

(c) Is a placeholder in case 9 bits of data is required

(d) Is not currently implemented, but will be in the future

46. Baudot asynchronous serial communications was developed for:

(a) Networking

(b) Televisions

(c) Teletypes

(d) Telegraphs

47. What are the differences between Baudot asynchronous serial communications and NRZ serial communications?

(a) None

(b) The number of bits transmitted

(c) The speed at which data is transmitted

(d) The number of ‘‘overhead’’ bits

48. The primary difference between Manchester Encoding and NRZ is:

(a) The media used to transmit the data

(b) The bit timing for ‘‘0’’ and ‘‘1’’ change in Manchester Encoding

(c) The data rates used to transmit the data

(d) The companies that hold the original patents on the technologies

49. To implement a three wire RS-232 connection, you will have to tie together:

(a) RTS/CTS and DSR/DTR

(b) RI/CTS and DSR/RTS

(c) DCD/DSR and RTS/CTS

(d) DCD/CTS and RI/DSR

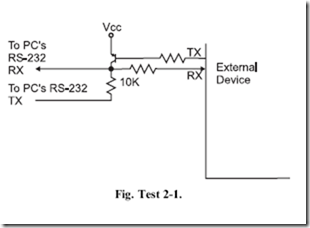

50. The RS-232 to TTL/CMOS level translator shown in Fig. Test 2.1:

(a) Is an inexpensive, full capability RS-232 interface

(b) Sends data in ‘‘half duplex’’ mode only

(c) Can be used for handshaking lines as well as RX and TX

(d) Is limited by the speed it can operate at