Chapter 8: Data Storage Device Interfaces

Overview

Data storage devices—removable and nonremovable hard and floppy disk drives, CD and DVD optical disks, streamers, solid disks, etc.—are connected to computers in various ways. The first PC data storage devices—floppy disk drives (FDD)—were connected by an interface ribbon cable to the controller, which was separated from the drive itself. This specialized interface has survived to the present day, and is used to connect disk drives that only require transfer speeds of 500 Kbps (about 60 KBps). The speeds of 1,000 Kbps needed for the 2.88 MB floppy drives, which were not as widely accepted as had been expected, has not been utilized. Old streamers (very low-speed ones) used to be connected to the disk drive interface. The similar interface was also used to connect MFM and RLL hard drives; raw, albeit amplified, data were sent over it to and from the disk heads.

Later, data storage devices were given some “brains,” and for a short time the ESDI disk interface—which provided whopping transfer speeds of 1 MBps—appeared. However, soon the controller was moved to the drive itself and, moreover, was provided with its own buffers (at first holding only one sector, but subsequently growing rapidly), and everything that had to do with magnetic data recording and reproducing was taken out of the external interface. Thus developed were ATA interface devices, which first appeared in 1988 and now are the most commonly used type of data storage devices. For devices that are logically different from hard disks—optical, magneto-optical, tape, and any others—the ATAPI specification was accepted in 1996. This is a packet expansion of the interface that makes it possible to send command information blocks whose structure has been modeled on the SCSI to a device over the ATA bus. The ATA speed ceiling is 133 MBps in Ultra DMA Mode 6. The ATA interface has an addressing limit of about 137 GB, which is now being overstepped; the ATAPI interface employs 32-bit addressing, which allows up to 2 TB to be addressed (using 512 byte blocks). The next step in the development of the interface is the Serial ATA. In this interface, issues such as increasing the exchange speed, simultaneous work with multiple devices, and expanding the addressing limits are addressed. The same addressing has been introduced in the latest version of the parallel ATA.

Universal interfaces also are employed for storage devices. The SCSI bus is the ATA’s first challenger in both the parallel and serial (FCAL) versions. Providing approximately the same exchange rates, the SCSI allows operation of multiple devices on the bus. The bus itself is available for use by other devices when it is executing a command with a long data wait time. In contrast to the purely internal ATA bus, the SCSI bus allows external devices to be connected to it. For connecting external storage devices, the USB and, less frequently, Fire Wire buses are employed; the LPT port can also be enlisted for this purpose.

8.1 FDD Interface

Floppy disk drives are connected to the controller using a special standard interface. The major control functions, as well as data coding/decoding, are performed by the controller, which is built into the overwhelming majority of modern motherboards. In the past, the controller was often built on a special expansion card along with floppy drive interface. The printed circuit board that is located on the floppy case contains only the motor controlling circuitry, the read and write signal amplifiers and generators, respectively, and sensor signal-drivers.

8.1.1 Hardware Interface

All FDD interface signals are active low logical TTL levels. The output signal drivers have the open collector type output. The interface presupposes terminators—load resistors—for each signal line of the device. Theoretically, they are supposed to be turned on only on the last drive in the chain, but in practice they are always on. Modern 3-inch drives employ “distributed terminators,” relatively high value (1K-1.5K) resistors that permanently link the interface input lines with’ the +5 V rail. Because the interface operates at low frequencies, the problem of precisely matching the impedance of the ribbon cable and the terminator’s resistors does not arise. However, if only old 5-inch floppy drives with their terminators removed are connected to the ribbon cable, they may not operate reliably (the open collector output lines will have no loads).

In terms of logic, the interface is quite simple. To set the drive into work, it needs to be selected by the Drive Sel signal and start the motor spindle with the Motor On signal. There are four signals for selecting a floppy drive (Dso … DS3), but a particular drive responds to only one, which is determined by its jumper settings. The selected drive responds to the controller’s signals and sends its signals to the controller. The fact of a drive having been selected is indicated by a lit LED on its front panel.

To move the heads one step, the controller must issue the step pulse; the direction is determined by the Direction signal level: the move is toward the center of the disk (track number increases) when the signal is active (low). The controller locates the zero track by moving the heads from the center toward the edge until the TrackOO signal is sensed. The head number is selected by the side1 signal. The drive marks the beginning of a track by the index pulse that is generated when the index hole of the revolving disk passes under the sensor. The data that are read are MFM coded, amplified, converted to a TTL signal, and output over the Read Data line. The write mode is enabled by the Write Gate signal; encoded digital data are input from the controller over the Write Data line. If the diskette is write-protected, the drive will generate a Write Protect signal. To obtain the lower write current needed when double or quadruple density diskettes are used in a high density drive, the Reduce Write signal is employed. This signal is also called Low Current or FDHDIN. To switch the heads into the “vertical write” mode used for 2.88 MB diskettes, the FDEDIN signal is used. Both of these signals are generated by the controller, but for the drive itself they are duplicated by signals from the diskette type sensors. (The FDEDIN signal is not required; the drive itself will switch the mode at the sensor signal.)

Some disk drives allow the described diskette type sensor operating method, which is used in the PC compatible computers, to be modified: They may be disconnected or provide information to the controller. However, practically all controllers themselves control the interface lines that correspond to the sensor signals. In doing this, they take into consideration the disk drive type defined in the SMOS Setup and the requested diskette type. The controller generates the low-level Reduce Write signal at any time it accesses the drive described in the CMOS as high density (1.2 MB or 1.44 MB) for working with double or quadruple density diskettes (360 KB or 720 KB, respectively). Some controllers only generated this signal when they were set to the 300 Kbps operating speed (360/720 KB diskette in a 1.2 MB disk drive). This type of controller can format and write 720 KB diskettes in a 1.44 MB drive only when the drive is equipped with a high density sensor and the latter is properly configured; otherwise, it will write all 3.5 inch diskettes with high write current, which cannot be done for quadruple density diskettes.

High density drives assert the Disk changed signal when a diskette has been changed; it is deasserted after the drive has been accessed. This signal, deserves special attention; only high density and extra high density (the rare 2.88 MB) drives have it. The function of this signal is determined by setting the drive’s jumpers. In PCs, the corresponding jumper is set to the DC (Disk Change) position. The alternative function of this line—device ready, which may be called RY, RDY, or SR—cannot be used in PC-compatible computers.

There are no signals in the interface that directly inform the controller of the drive being ready (i.e., a diskette having been inserted). The controller can determine this only after selecting the drive and starting its motor. Then, the absence of Index pulses will mean that the drive is not ready: either there is no diskette inserted, or it is not fixed on the spindle, or the drive’s interface or power cables are not connected. The controller may determine whether the drive is present by issuing the recalibration command; the drive should respond with the TrackOO signal when it is executed.

Regardless of their type and capacity, all floppy disk drives used in PCs employ the same interface and standardized 34-contact connectors of two types: two-sided PCB connectors used for 5.25 inch drives, and the other with two rows of pin connectors used for 3.5 inch devices. The ribbon cable used to connect floppy drives in PCs has wires 10-16 twisted around (Fig. 8.1). This twist allows two floppy drives to be connected to the controller by one ribbon cable. A drive’s address is determined by its location of the ribbon cable: The B drive is connected by the straight cable, the A drive is connected to the connector on the twisted part of the ribbon cable. The universal ribbon cable with five connectors (shown in the drawing) allows a pair of any type of drives to be connected; they must be connected to the different parts of the cable. Some connectors may be absent, and this will limit the drive’s configuration flexibility. Table 8.1 describes interface cable signals that arrive to different drives. Signal direction (I/O—input/output) is shown with respect to the controller.

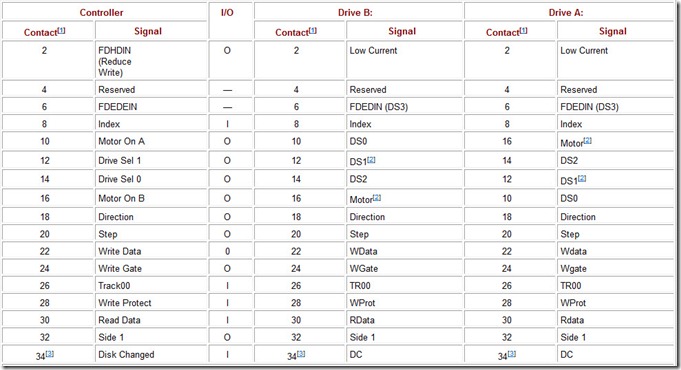

Table 8.1: FDD Interface Cable Signals

[1]Odd contacts 1-33 are grounded. For 5.25-inch drives, the key is between contacts 4-5 and 6-7.

[2]The signal pair that selects the FDD. (Motor On A and Drive Sel 0 for the A: drive and Motor On B and Drive Sel 1 for the B: drive.)

[3]Contact 34 is not used in XT.

The floppy drive controller and the interface cable employed in PCs allow one of the two drives be addressed and its motor turned on. The Drive Sel 0 and Motor On A signals are used for the A: drive, and the Drive Sel 1 and Motor on B signals are used for the B: drive. The jumpers on both drives are set so that they both respond to the DS1 signal (connector contact 12). Usually, the jumpers are labeled DAO/DS1 DS2/DS3; in this case, the DS1 jumper must be set. If the jumpers are named as DS1/DS2/DS3/DS4, which is not encountered often, then the DS2 jumper must be installed. The adopted drive selection system allows all the drives to be configured the same way and their addresses to be set by their location on the ribbon cable. Certain PC clones employ a different drive selection system and a “straight” ribbon cable. In this case, a device is selected by the DSO signal. However, using this line for selecting drives is not supported by some drives; consequently changing drives in these proprietary machines may turn out to be very troublesome, especially if the technical manual is not available.

8.1.2 FDD Controller

Software interacts with floppy disk drives via the Floppy Drive Controller, enlisting, as a rule, the DMA controller and interrupts. Programming the FDD controller to work with diskettes is a troublesome task. All functions necessary for using FDD for storing data are implemented in the BIOS int 13h services and the operating system. Ignoring the BIOS services and even the operating system is justified mainly when implementing non-trivial tasks such as working with key diskettes and the like.

All controllers used in IBM PCs are compatible with the historical NEC PD765 controller microchip, an analog of the 18272 microchip. The AT floppy drive controller supports two drives and several data transfer speeds: 250 Kbps (for single, double, and quadruple density diskettes for old 5.25-inch drives), 500 Kbps for high density diskettes (1.2 MB and 1.44 MB), and also 300 Kbps for working with single, double, and quadruple density diskettes in high density 5.25-inch drives. Modern controllers that support extra-high density drives (2.88 MB) must provide transfer rates of 1,000 Kbps. The controller’s modes that correspond to speeds of 250/300 Kbps, 500 Kbps, and 1,000 Kbps are named 1M, 2M, and 4M, respectively. In the 1M mode, one track holds nine 512-byte sectors, which requires a transfer rate of 250 Kbps at a rotational speed of 300 rpm and 300 Kbps at 360 rpm. In the 2M mode at 300 rpm (3.5-inch high-density drives), one track holds 18 sectors, and at 360 rpm (5.25-inch high-density drives), one track holds 15 sectors. The 4M mode appears to have been left unused. The selected speed determines the write and format synchronization frequency, and also adjusts the frequency locked loop circuitry of the controller’s data separator. The data separator can reliably extract data and sync signal from the signal received from the reading head only when deviations in speed are within ±10% of the nominal; therefore, the speed for all disk data exchange operations must be selected correctly.

In the AT resource map, an area for two floppy disk controllers is allocated:

-

AT#1 FDC (standard or main) is allocated ports 3F0h-3F7h (the same as the XT FDC).

-

AT#2 FDC (supplementary) is allocated ports 370h-377h.

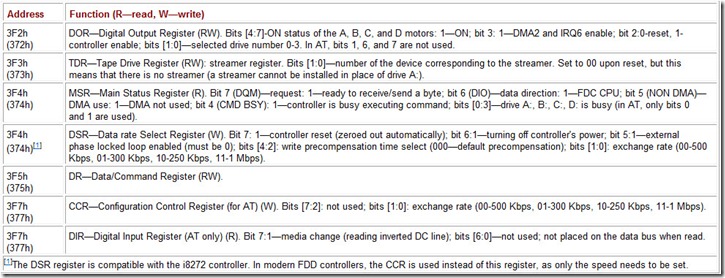

Upon completing execution of an internal operation, controllers generate the hardware interrupt request IRQ6 (BIOS Int OEh). The DMA2 channel can be used for data exchange. The functions of the controller’s registers are listed in Table 8.2.

Table 8.2: FDD Controller Registers

The FDC status register address 3F7h (377h) coincides with the address of HDC register (long not used), which makes separate operation of FDC and HDC located on different boards problematic. In the standard (not diagnostic) mode, only bit 7—media change indicator—is of any interest.

An FDD controller can also be used to work with streamers. Especially for this purpose, it is equipped with the tape drive register TDR. The two lower bits of this register set the number of the device corresponding to the streamer. (The data separator phase locked loop circuitry is adjusted differently for streamers).

All operations with diskettes are done by commands sent by the host to the DR (3F5h) according to the status of the MSR (3F4h) bits. A command or data byte can only be written to the DR when MSR=10xxxxxxb; writing is allowed when MSR=11xxxxxxb. To read/write this register, separate subroutines need to be used that not only wait for the MSR enabling values, but also can exit upon an emergency timeout. The host also writes to the DOR (3F2h) to start/stop the drive, as well as to the CCR (3F7h) or DSR (3F4h) to set the data transfer rate. The DMA controller is usually involved in the diskette data exchange operations and it has to be initialized in due time. The TC signal (DMA cycle completion) is used to indicate the end of the data phase. The overall data exchange procedure consists of the following steps:

-

Disk selection and motor start (by writing to the DOR).

-

Setting the speed (by writing to the CCR).

-

Executing a recalibration command.

-

Waiting for the motor to spin up (if it has been on for less than 0.5 sec).

-

Positioning the head on the necessary cylinder.

-

Initializing the DMA controller.

-

Sending a read/write command.

-

Waiting for an interrupt from the controller. An interrupt will be generated upon completion of the controller/host data exchange phase execution. If no interrupt is forthcoming within the specified time period, a time-out access error is recorded.

-

After the controller issues an interrupt, the resulting bytes are read and if they are correct, the process terminates. If the data contain errors, then the DMA initialization and the read/write command sending steps are repeated. If the data still contain errors after three attempts, then another recalibration command is executed and steps 6-7 repeated. If after several recalibration attempts the data still contain errors, an abnormal exchange termination is performed.

In addition to the mechanism described, there is a mechanism to automatically turn off the FDD motor if it has not been accessed for a prolonged period of time. For this purpose, cell 0:0440h in the BIOS Data Area contains the FDD motor timer and cell 0:043Fh contains the address of the drive whose motor is currently ON. Every time diskette access is attempted, BIOS places the default time-out motor off value (25h, or about 2 seconds) into this cell. During each timer hardware interrupt IRQ0 (BIOS int 08h), which occurs about every 55 msec, the value in this byte is decremented by 1. When it finally reaches 0, the drive motor is shut off. Therefore, if no accesses to diskette are made during the set interval, the motor automatically switches off. Of course, this works only when BIOS services the hardware timer interrupts, so the drive motor not shutting off may be an indirect indication that the computer has hung.

Execution of each command is broken into three phases:

-

The command phase. The controller sets bits DQM=1 and DIO=0, which is an invitation to input a command. A command byte is sent to the DR, followed by the parameter bytes in a strictly defined order. The controller respond to each received byte by zeroing out the DQM bit for the duration of the byte processing. After receiving the last required byte, the DQM bit remains zeroed out and the controller proceeds to the execution phase. The parameters involved are: the cylinder number C, the head number H, the sector number R, the size code N or the sector data field length DTL, the number of the last sector on the track EOT, the number or sectors SC, the gap length GPL, and some other data.

-

The execution phase requires the transfer of data from the host to the controller or vice versa. The transfer can be conducted in both the DMA mode and in the Programmed Input/Output (PIO) mode. In the DMA mode, the transfer is performed by the DRQ and DACK# signals of the channel being used. If the DMA mode is not used, then the transmission request is done by the DQM bit and the interrupt request signal. After the phase is terminated, the interrupt request signal is generated (and its flag is set in the STO register), and the controller advances to the result phase.

-

In the result phase DQM=1 and DIO=1, the host must read the result bytes from the DR, after which these bits change to DQM=0 and DIO=0, which corresponds to moving to the command reception phase.

From the moment a command is received and until the result phase terminates, the CMD BSY bit in the MSR remains set to logical 1. The controller can always be reset (i.e., moved to the beginning of the command phase) by writing to the DOR or DSR. If the controller receives a command it does not support, it sets DQM=1 and DIO= 1, which means that the DR needs to be read. The host then must read the status code out of the DR; this code will be 80h (invalid command).

Modern FDD controllers employ a 16-byte-deep FIFO buffer to transfer data (but not commands or parameters) through the DR. The “historical” i8272 controller did not have this FIFO buffer. The logic to communicate with the DR remains the same. The buffer must be serviced in a timely manner so that it does not overflow or underflow. The buffer logic fashions data requests in such a way as not to bother the host unnecessarily. When reading the DR, the request is sent when there are 16-minus-threshold bytes in the buffer, or when the last byte of the sector has been read off. When writing to the DR, at first the request is set and held until the buffer gets, filled up, thereafter it is set when threshold bytes are left in the buffer. The advance to the result phase happens when the host concludes the exchange with the DR and the buffer empties. Communication with the DP. when writing commands or parameters must be done according to the values of the high bits of the MSR (the FIFO buffer is not used in these communications).

8.2 ATA/ATAPI (IDE) Interface

The ATA (AT Attachment for Disk Drives) was developed during 1936-1990 to connect hard disk drives to IBM PC AT computers built around the ISA bus. The standard, which was developed by the X3T10 committee, defines a set of device registers and functions of the 40-contact interface connector signals. The interface came about as a result of moving the standard (for PC/AT) hard drive controller on the drive itself (i.e., creating a device with a built-in controller: IDE (Integrated Drive Electronics)). The standard AT controller allowed up to two hard drives to be connected, which in the ATA interface means connecting individual controllers of two devices in parallel. The ATA specification defines the following components:

-

A host-adapter is a means to couple the ATA interface with the computer bus. In this book, the host is called a computer equipped with an ATA interface host-adapter. A host-controller is a more advanced version of a host-adapter.

-

A master device in the ATA specification is officially called Device-0.

-

A slave device in the ATA specification is officially called Device-1.

The host-adapter and devices are connected by a ribbon cable that connects the like contacts of the interface connectors in parallel. The registers of both controllers turn out to occupy the same area of the I/O address space. To select the device executing the current command, the DEV drive select bit in the drive/head register is used. If DEV=0, then the master device is selected; if DEV=1, then the slave device is selected. Writing to this register is sensed by both the master and the slave, but only the selected device reacts to access to the other registers. A fairly universal signal set allows the connection of any device that can support the device select method using the above-mentioned bit and that has a built-in controller for whose I/O operations the available register set is sufficient. The adopted system of commands and registers, which is a part of the ATA specification, is oriented at block data exchange with direct access devices. For other devices, there is the AT API specification, which is based on the same hardware resources but allows control of the information package to be exchanged (PI—Package Interface). Packets’ structure and contents are borrowed from the universal SCSI interface. The packet interface makes it possible to expand the boundaries of ATA applications.

The ATA addressing has “disk roots”: originally, so-called tri-dimensional CHS addressing was used for disk drives, in which the addresses of the cylinder, head, and sector were specified. At first, this addressing corresponded exactly to real spatial geometry: Physically, the sector was actually located at the given address. Later, due to many factors, ATA disks began to be described using logical geometry that differed from the actual internal disk structure. (Thus, for example different areas on tracks have a different number of sectors; moreover, some of the sectors may be reserved for future replacement of defective sectors.) Virtual addresses are converted into real ones by the device’s built-in controller. Using the CHS system, an ATA device may address up to 267,386,880 (65,536 × 16 × 255) sectors (clusters), which, assuming sector size is 512 bytes, gives 136,902,082,560 bytes (or about 137 GB). Later, Logical Block Addressing (LBA) began to be employed. In this method, the sector address is specified by a 28-bit number, which allows up to 268,435,455 (228) sectors to be addressed (a little more than using the CHS system). For ATA devices that support both CHS and LBA, the addressing mode for each command is determined by the L bit (bit 6) of the D/H register; the modes can alternate in random order. ATAPI devices use a 32-bit logical addressing method like the one used in the SCSI; this allows up to 2 TB be addressed (using 512-byte cluster size).

If only one device is connected to the ATA interface, it must be designated the master. If two devices are connected, one of them must be designated the master and the other the slave. Devices are configured as master or slave by setting their configuration jumpers. If the “cable selection” method is used (see below), the device’s role is determined by its location on the special ribbon cable. Both devices perceive commands from the host-adapters at the same time; however, only the selected device will respond. Only the selected device has the right to output signals to the ATA bus. This type of system implies that once the host-adapter has begun an exchange operation with one of the devices, it cannot switch to servicing another until it has completed the operation in progress. Only devices connected to different ATA channels can work in parallel. The ATA-4 specification defines a method to get around this limitation, but this capability is seldom used.

Several versions of the interfaces exist for IDE devices. They are as follows:

-

ATA, or AT-BUS—a 16-bit interface for connecting devices to an AT computer bus. This is the most common 40-wire signal and four-wire power interface for connecting disk drives to AT computers. For miniature (2.5-inch and smaller) drives, 44-wire cable incorporating the power supply lines is used.

-

PC Card ATA—a 16-bit interface using a 68-contact PC Card (PCMCIA) connector for connecting devices to notebook PCs.

-

XT IDE (8-bit), or XT-BUS—a 40-wire interface similar to the AT, but incompatible with it.

-

MCA IDE (16-bit)—a 72-wire interface designed especially for the PS/2 bus and diskdrives.

-

ATA-2—an extension to the ATA specification. It supports two channels, four devices, PIO Mode 3, Multiword DAM Mode 1, Block mode, disk size of up to 8 GB, and LBA and CHS.

-

Fast ATA-2 allows the Multiword DMA Mode 2 (13.3 MBps) and PIO Mode 4 to be used.

-

ATA-3—an extension to ATA-2. It provides password protection, improved power management, and a self test with advanced failure warning (Self-Monitoring Analysis and Report Technology (SMART)).

-

ATA/ATAPI-4 is an extension to ATA-3 that includes Ultra DMA (with transfer rates of up to 33 MBps) and the AT API packet interface. It also supports command queues and protocol overlap.

-

ATA/ATAPI-5—a revision of ATA-4/ATAPI-4. Outdated commands and bits are removed, new protection capabilities and power management are added. Includes Ultra DMA mode (transfer rates of up to 66 MBps).

-

ATA/ATAPI-6—a supplement to the ATA-5/ATAPI-5. Contains audio and video streaming for multimedia application, hard disk noise reduction, Acoustic Management, and Ultra DMA mode with transfer throughput of up to 100 MBps.

-

Serial ATA.

-

E-IDE (Enhanced IDE)—expanded interface introduced by Western Digital. It is implemented in adapters for the PCI and VLB buses. The interface allows up to four devices, including CD-ROM and streamers (ATAPI) be connected (to two channels). PIO Mode 3, Multiword DMA Mode 1, and LBA and CHS drives of up to 8 GB are supported. Hardware-wise, it conforms almost completely to the ATA-2 specification.

ATA IDE, E-IDE, ATA-2, Fast ATA-2, ATA-3, ATA/ATAPI-4, ATA/ATAPI-5, and ATA/ATAPI-6 devices are electrically compatible. The degree of logical compatibility is quite high: All basic functions are available. However, in order to implement all the extensions fully, the specifications of the devices must match up to the host-adapter and its software.

The ATA/ATAPI specifications are developed by the T13 technical committee of the International Committee for Information Technology Standards (INCITS). The specifications they develop are approved and published by the American National Standards Institute (ANSI). The ATA/ATAPI-6 specification has been declared the last parallel ATA version; it is followed by the Serial ATA serial interface.

8.2.1 ATA Parallel Interface

The ATA parallel interface is a bus with standard TTL logic signals:

-

Output signal high level is no lower than 2.4 V (at up to 40 microampere current, the DMARQ signal is up to 50 microampere); low level is no higher than 0.5 V (at 4 milliampere current; current on the DASP line is 12 milliampere for compatibility with old devices).

-

Input signal high level is not lower than 2.0 V; low level is no higher than 0.8 V.

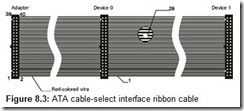

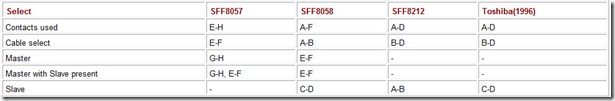

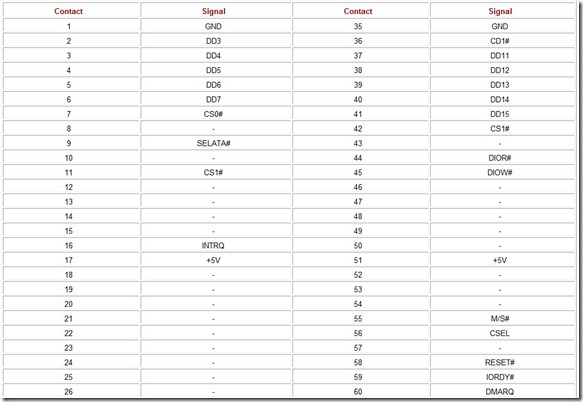

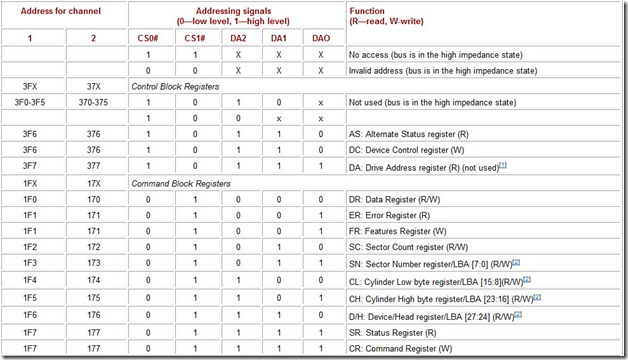

All the interface’s information signals are sent over a 40-contact connector. To ensure correct connection, the connector has a key: removed are a pin on the plug and a hole on the socket in the place of contact 20. The standard does not approve the use of a notch on the plug case and a protrusion on the socket as keys. Devices are connected using multiple-wire ribbon cable. Its length must not exceed 18 inches (0.46 meters); allowable conductor capacitance is no more than 35 picofarads. Terminators for the cable are not required by the standard (each device and the host-adapter are equipped with them). However, if a three-connector cable is used to connect one device, then it is recommended to connect the device and the host-adapter to the end connectors. The ATA interface signal set is shown in Table 8.3; the cable is shown in Fig. 8.2. In most connectors, the like contacts of all connectors are connected in parallel and all the connectors are equal. However, sometimes (not very often), ribbon cables adapted to select devices are encountered. These cables have their wire 28 cut (Fig. 8.2); consequently, contact 28 (SCEL) of the master device is grounded at the host-adapter and the slave device has this contact unconnected. This type of device selection is called cable select. Cable used must correspond to the addressing system selected for both devices.

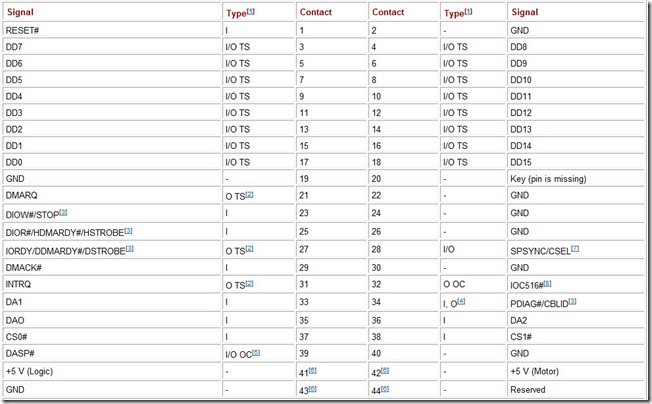

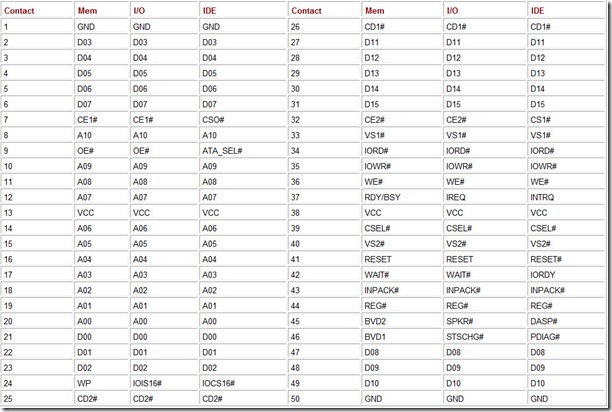

Table 8.3: ATA (IDE) Interface

[1]Signal type for a device: I—input, O—output, I/O—bidirectional, TS—tristate, OC—open collector. For host-adapter, meanings of I and O are reversed.

[2]In old devices, signal may be of the OC type (different type signals on one bus may create a bus conflict).

[3]Signals listed after the/signs are only used in the Ultra DMA (ATA-4) mode.

[7]Starting with ATA-3—only SCEL.

[8]Starting with ATA-3—reserved.

[4]Input for the master device, output for the slave device.

[5]Output only for the slave device.

[6]Contacts 41-44 are only used for miniature disks.

Starting from ATA/ATAPI-4, cable-select ribbon cables were approved and the middle connector was designated for connecting device 1. In this cable, contact 28 is either not connected to the wire or is simply missing. Naturally, when using cable-select ribbon cables, the host-adapter cannot be connected to the middle connector (nor to the right connector in Fig. 8.3). If a device is assigned a number by a jumper, then devices and the host-adapter can be connected to any connector on the 40-wire ribbon cable; however, it is desirable to avoid loose ends.

For stable operations in the Ultra DMA mode, 80-wire cables with alternating signal and ground wires are recommended. These cables are required for Ultra DMA modes higher than 2 (transfer rates greater than 33 MBps). These cables are connected to special connectors whose pinout is the same as the regular 40-contact connectors.

All ground wires are connected to the special jack-in contacts. Either all even or all odd wires are grounded, depending on the type of the connectors used (they must be marked EVN GND or ODD GND). Different types of connectors cannot be mounted on one cable (in this case, all 80 wires will be connected together). On the 80-wire cable, contact 34 on the host-adapter connector is connected to the GND rail but not to the cable wire; this serves to identify the type of cable used (CBLID). The cable wire connects contacts 34 of the device connectors, allowing the PDIAG# signal pass from the master to slave. Because the cable select system is used, connectors’ roles on the 80-wire cable are position-specific:

-

The host-controller connector is located at one and of the cable; its contact 34 is grounded and not connected to the cable. It must be colored blue.

-

The device 0 (master) connecter is located on the opposite end of the ribbon cable; all of its contacts are connected to the cable. It must be colored black.

-

The device 1 (slave) connector (optional) is located in the middle of the cable; its contact 28 is not connected to the cable. It must be colored gray.

If the cable-select system is not used, devices 0 and 1 can be connected to any of the two device connectors.

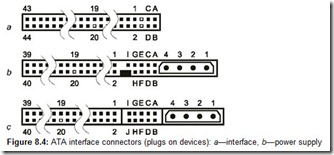

The ATA specification allows both the 40-contact signal connector and the 4-contact power connector (Fig. 8.4), but for compact devices power can be supplied over 44-wire interface cable.

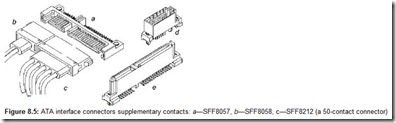

Most devices are connected using a 40-contact connector with the contacts spaced 0.1 inch (2.54 mm) apart. Additional contacts employed for device configuration, diagnostic, and other service operations using the serial interface may be located next to the main contact group. The ATA/ATAPI specification defines two versions of supplementary contact group connectors (Fig. 8.5, a and b). In these drawings, unshaded squares indicate missing contacts taken by the keys; contacts 1-40 are used for the interface signals (Table 8.3), and contacts A-H are used to set jumpers (Table 8.4) and for the servicing signals. Compact devices are connected using a 50-contact connector with contacts 2 mm apart (Fig. 8.5, c) whose contacts correspond to Table 8.3 and contacts A-D correspond to Table 8.4. (Contacts A-D are used for configuration, and the missing pair of contacts serve as an additional key). In the 50-contact connectors, contacts A-D are usually assigned functions like those of the IBM Think-pad/Travelstar drive outputs:

-

Contact a is connected by a 10 K resistor to the +5 V rail.

-

Contact B sets the device’s role: low level—device 0, high level—device 1.

-

Contact C sets the device mode on powering up: low level—Standby, high level—Idle.

-

Contact D is connected to contact 28 (CSEL) and through a 10 K resistor to the +5 V power rail.

Table 8.4: Functions of Supplementary Contacts

These contact functions, allowing both device selection and power consumption mode to be configured, are used not in all devices. In Toshiba drives, contacts A and B may be employed as serial interface input and output (B is pulled to the +5 V power rail through a 47 K resistor), contact C is connected to the GND rail, and contact D sets the device role (low level for device 1).

For compact external drives, a quite common HP 36 connector is used, but it is not covered by the ATA/ATAPI specification. Flash memory storage devices use connectors conforming to the CompactFlash Association specification.

Device documentation may name signals somewhat differently. The ATA/ATAPI-4 standard signal names are given below:

-

RE5ET#—Device Reset. A signal of no shorter than 25 fisec is generated after the power supply voltages have settled. The signal resets the interface into the initial state and sets the default parameters.

-

DA [2:0]—Device Address. Three lower system address bus bits used to select device registers.

-

DD [15:0]—Device Data. Biderectional 16-bit data bus between the adapter and devices. In 8-bit exchanges, only the lower D [7:0] bits are used. There must be no pull-up resistor on the device’s DD7 line: on the host-controller, this is line connected by a 10 K resistor to the GND rail. This allows the host to determine whether there is no device on the bus right after a hardware reset: When an attempt to read the status register of a non-existing device is made, the BSY bit would seem as being reset, which is impossible for ATA/ATAPI.

-

DIOR#—Device I/O Read. I/O read strobe. Data are latched at the positive signal transition.

-

DIOW#—Device I/O Write. I/O write strobe. Data are latched at the positive signal transition.

-

IORDY—I/O Channel Ready. Device is ready to complete the exchange cycle. By driving this signal low during the exchange cycle, a device can insert bus wait cycles. The signal is needed when performing exchanges in the PIO Mode 3 or higher. On the host-controller, this line must be pulled up to the power rail by a 1 K resistor.

-

IOCS16#—16-bit Operation Enable. All registers, except the data register, are always accessed in the 8-bit mode. In the PIO Modes 0, 1, and 2, when this signal is active (low), the access is 16 bits; when the signal is inactive (high), the access is 8 bits. In the PIO Modes 3 and 4 and DMA, all exchanges are 16 bits, with the exception of supplementary bytes (those extending past the 512-byte sector boundary) of the long read and write operations. Not used starting from ATA/ATAPI-3.

-

DMARQ—DMA Request (optional). When the exchange is enabled, the high level signal is asserted by the device when it is ready to perform exchange. Having asserted the DMARQ signal, the device must wait until it receives the DMACK# acknowledgement signal from the host-adapter, after which it can deassert the DMARQ signal. The request must be asserted for next transmission. In the Multiword MDA mode, the signal may be held asserted for the duration of the transmission of all the data. The signal must have the tristate output; during DMA mode operations, only the selected device can hold it in an active state (either 0 or 1). In ATA-1, this signal could use both the tristate and the regular TTL outputs. Having two devices with different types of the DMPRQ outputs on one bus may cause conflicts. On the host-controller, the line must be connected to the GND rail by a 5.6 K resistor.

-

DMACK#—DMA Acknowledge. The signal is generated by the host-controller as a confirmation of the transmission cycle. Transmission of a data byte is controlled by the DIOR# or DIOW# signals. During exchange over a DMA channel, the IOCS16#, CSO#, and CS1# signals are not used; exchange is always conducted in 16-bit words.

-

INTRQ—Interrupt Request. The output must be tristate. Only the selected device generates the active signal (logical one) when it has an unserviced interrupt request under the condition that it is not disabled by the nIEN bit in the Device Control register. The request is cleared by the RESET# signal, by setting the SRST bit in the Device Control register, by writing to the command register, or by reading the status register. In PIO exchanges, the request is set at the beginning of the transmission of each block (a sector or a group of sectors in multi-sector operations). The Format Track, Write Sector(S), Write Buffer, and Write Long commands at the beginning of the transmission of the first data block are exceptions and do not generate an interrupt request. In DMA exchanges, the interrupt request is generated only upon completion of the operation. On the host-controller, this line must be pulled up to the GND rail by a 10 K resistor.

-

CSO#—Chip Select 0. A Command Block Register select signal. For channel 1, it is generated when there is an I/O port address in the 1FOh-1F7h range on the system bus. The signal is also called CS1FX#.

-

CS1#—Chip Select 1. A Control Block Register select signal. For channel 1, it is generated when there is an I/O port address in the 3F6h-3F7h range on the system bus. This signal is also often called CS3FX#.

-

PDIAG#—Passed Diagnostics. The master device monitors this signal, which the slave device must generate in response to a reset signal or a diagnostics command. If a slave device has been detected (by its DASP# signal), the master device waits for this signal 31 seconds after reset and 6 seconds after a diagnostics command. If during this time the signal does not come, the master device records this by setting bit 7 in the error register. If a slave device has not been detected, the master device zeroes out the slave device status register and informs the system of its own status immediately after completing its own self-diagnostics. The signal is only used for communicating between the two devices, and is not used by the hostadapter. (In ATA-4, this contact is used for the CBLID# signal.)

-

CBLID#—Cable Assembly Type Identifier. In the 80-wire cable, contact 34 on the host-adapter connector is connected to the GND rail; contacts 34 of the device connectors are connected to each other but not to the host-adapter connector. On devices, this line must be pulled to the power rail by a 10 K resistor. After reset and when the PDIAG# signal is deasserted, a low level of signal informs the host that the 80-wire cable is present.

-

DASP#—Device Active/Slave Present dual-purpose signal. Devices’ outputs are of the open collector type and are connected by 10 K load resistors to the +5 V rail. Within 1 msec after a RESET# signal, or when initializing upon being powered up, both devices must deactivate this signal; afterward, the slave device asserts it no later than within 400 msec to inform the system of its presence. The master device does not activate this signal for 450 msec. The slave device deactivates this signal after it receives a command or automatically after 31 seconds, whichever happens first. Any device can then assert this signal to indicate its readiness. The host-adapter uses this signal to operate the HDD access LED indicator.

-

SPSYNC/CSEL—Spindle Synchronization/Cable Select. A dual function signal. The function selected must be the same for the both devices. The SPSYNC allows spindles of devices to be synchronized, which is important for RAID systems. It is used at the user’s discretion; since ATA/ATAPI-3, this signal has been removed from the specification. The CSEL signal allows devices to determine their addresses by their location on the special cable with wire 28 between the two devices cut (the seldom used cable select method). On the host-adapter, this line is grounded; the master device gets the grounded line and the slave device gets the unconnected line. On the device side, the line is pulled to the high level by a 10 K resistor. If the signal is controlled by the host-adapter, it must hold it for at least 31 seconds after the RESET# signal.

When the Ultra DMA mode is used, four signal lines get new functions:

-

STOP—Stop Ultra DMA burst.

-

DDMARDY#—Device Ultra DMA ready when receiving an Ultra DMA packet (flow control).

-

DSTROBE—Host Ultra DMA data strobe from device when sending a burst to the host. Data are sent at both transitions of the DSTROBE signal.

-

HDMPRDY#—Host Ultra DMA ready when receiving a burst (flow control).

-

HSTROBE—Host Ultra DMA data strobe when sending a packet to a device. Data are sent at both transitions of the HSTROBE signal.

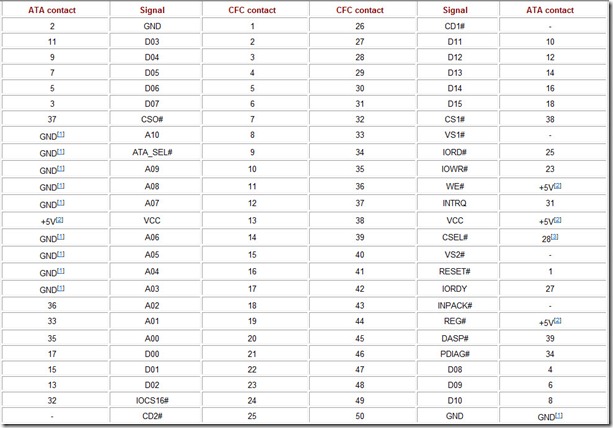

For notebook PCs, the standard has a version of the IDE interface using the 68-contact PCMCIA connector (PC Card) shown in Table 8.5. This version of the standard has several specific signals.

Table 8.5: 68-Contact ATA PC Card (PCMCIA) Interface

-

SELATA#—Select 68-pin ATA. This is a signal that the host uses to identify the mode in which the connector is used: in the PC Card mode, the signal is deasserted (high), in the ATA mode, the signal is asserted (low). The host must set this signal before the power is applied to the connector. For 19 msec after the power is applied, the device ignores all interface signals but this one. If this signal is active (low), the device must configure itself for ATA mode operation. If the signal is inactive, the device must configure itself for the PC Card mode or not answer to other signals from the host.

-

CD1# and CD2#—Card Detect signals; grounded on the device. By these signals, the host determines whether a device is present.

-

CS1#—Device Chip Select 1. Applied by the host to both contacts (11 and 42), but the device recognizes only one of them.

-

DMARQ, DMACK#, and IORDY—optional signals.

-

M/S#—Master/Slave. Inversion of the CSEL signal. The host issues the M/S# and CSEL signals before the power is applied; the device only recognizes one of them.

To provide for hot swap connection, the GND contact mates first when connecting a device and disconnects last when disconnecting it. The device’s CSO#, CS1#, RESET#, and SELATA# signals are pulled to inactive (high) level.

There is an 8-bit version of the interface—called XT-IDE or, less frequently, XT-Bus—for XT class computers. Like the ATA interface, this interface is implemented by a 40-wire cable, and many of its signals match the 16-bit ATA bus signals. The XT-IDE interface may be considered as a subset of the ATA interface, although they are not directly compatible. Some ATA type devices have a jumper for selecting the XT/AT mode (in Seagate drives, this is indicated by the suffix AX in the model’s name).

Device Registers

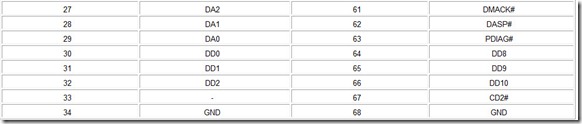

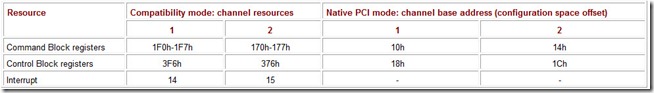

All ATA devices have a standard set of registers that are addressed by signals from the host-adapter (CSO#, CS1#, DA1, DAD, DIOR#, and DIOWS). The register set (Table 8.6) consists of two blocks that are selected by the CSO# and CS1# signals, of which only one may be active (asserted low). The table lists register addresses for the first and second ATA channels in the I/O space of an IBM PC compatible computer. When the registers are accessed, the DMACK# signal must be inactive (high). The command block registers serve to send commands to a device and read information about its status. The control block registers are used to control the device and to obtain more detailed information about its status. A zero value of the BSY bit in the status register indicates that the contents of the command block registers and of the alternative status register are valid. Except in separately stipulated cases, registers can be written to only when BSY=0 and DRQ=0. If the device supports power management control, in the sleeping mode the contents of these registers are invalid and a write to them is ignored, except in separately stipulated cases.

Table 8.6: ATA Device Controller Registers

[1]Recommended that the device not answer read signals at this address.

[2]Sector, cylinder, and head registers in the LBA mode contain the logical address bits shown.

The alternative status register AS (the address for channel 1 is 3F6h, for channel 2 it is 376h) has the same bits as the main register, but reading it does not change the device status in any way.

The device control register DC (3F6h, 376h,) is used to reset both devices simultaneously by software and to control interrupt enable of the selected device. This register can be written to at any time. Software reset using the DC register must also function in the Sleep mode.

DC register bit functions are as follows:

-

Bits [7:3]—reserved.

-

Bit 2—SRST: Software Reset. Active all the time while the bit is not cleared (both devices on the bus sense the software reset simultaneously).

-

Bit 1—nIEN: Interrupt Enable. Inverted interrupt enable bit (When the bit has the zero value, the selected device can generate the INTRQ signal on the tristate output).

-

Bit 0. Set to 0.

The device address register DA (3F7h, 377h) was only used in the first version of ATA in order to provide compatibility with old controllers; by reading this register, the addressed drive and head could be determined. The register drops out of the block (it coincides with the FDD controller status diagnostic register) and it is recommended that an ATA device not respond to reading this register. If the device does respond to a register reading, then it must not control the DD7 bit, in order to avoid a conflict with the FDD controller, which uses this line for the media change signaling. Not observing this rule may cause problems when the ATA adapter and the FDD controller are located on separate cards.

The functions of the DA register bits are as follows:

-

Bit 7—HiZ: Tristate. Not placed on the bus when read.

-

Bit 6—nWTG: inverted write indicator. During the physical write operation to the medium, the bit has zero value.

-

Bits [5:2]—nHS [3:0]: head number (inverted bits).

-

Bits [1:0]—nDS [1:0]: device select (inverted bits). 10—device 0 selected; 01—device 1 selected.

The data register DR (1FOh, 170h) can be used in the 8-or 16-bit mode depending on the type of data being transferred in the current command. This register is accessed in the PIO exchange mode (when the DMACK# signal is inactive (high)). When executing transmissions under the PO (PIO Out) protocol, the host writes to this register; when doing PI (PIO In) operations, the hosts reads the register. In the DMA mode, data exchange is carried via the data port; during this operation, the DMPRQ and DMACK# signals are active and the CS0# and CS1# signals are inactive.

The error register ER (1 Fl h, 171h) stores the results of executing the last operation or a diagnostic code. After the operation terminates, the status register ERR bit indicates if there has been an error.

The functions of the ER register bits are as follows:

-

Bit 7—reserved.

-

Bit 6—UNC: Uncorrectable Data Error.

-

Bit 5—MC: Media Changed. After media is changed, the first access command is rejected and the bit is set; after the bit is cleared, subsequent commands will be executed normally.

-

Bit 4—IDNF: ID Not Found. Indicates that the sector ID has not been found.

-

Bit 3—MCR: Media Change Requested. Media change request indicator. After the media change request is detected, the Door Lock command will return the ERR error bit and the MCR bit. The MCR bit is cleared by the Door Unlock and Media Eject commands or by a hardware reset signal.

-

Bit 2—ABRT: Aborted Command. Set if a command is rejected as invalid or if some other error occurs.

-

Bit 1—TKONF: Track 0 Not Found. Indicates that the Recalibrate command could not find track 0.

-

Bit 0—AMNF: Address Mark Not Found. Data address marker in the sector header not found.

After execution of any type of reset or after the Execute Device Diagnostic, the error register contains a diagnostic code. With the exception of bit 2 (ABRT), the meaning of the bits varies depending on the command that has been executed.

The use of the features register FR (1Flh, 171h) depends on the current command. In the Set Features command, this register is used to set the subcommand code. Some old devices may ignore a write to this register. Prior to accepting the ATA-2 specification, the value of the recommended cylinder number for write precompensation was placed into this register.

The sector count register SC (1 F2h, 172h) holds the number of sectors involved in the exchange. The host initializes this register prior to issuing the command (zero value corresponds to 256 sectors). After a successful termination of a data access operation, the register must be zeroed out. If the command terminates with an error, the register will contain the number of sectors that must be transferred to complete the previous request successfully. The Initialize Device Parameters or Write Same commands may redefine the function of this register. In some commands, the register is used to send other parameters.

The sector number SN (1F3h, 173h) and cylinder number registers—low CL (1F4h, 174h) and high CH (1F5h, 175h) bytes—have dual functions depending on the addressing system being used (CHS or LBA). They are initialized by the host-adapter. If a device encounters an error during execution of a command, it places the address, at which the error occurred, into this register.

The device and head number register D/H (1F6h, 176h), in addition to storing part of the address information, is used to select the master or slave device and the addressing method.

The functions of the D/H register bits are as follows:

-

Bits 7 and 5 in the ATA standards up to ATA-3 had to have values of logical 1. In ATA/ATAPI-4, these bits were declared obsolete.

-

Bit 6—L. Logical 1 indicates the LBA addressing mode; logical 0 indicates that the CHS mode is used.

-

Bit 4—DEV: Device select. When DEV=0, the master device is selected; when DEV=1, the slave device is selected.

-

Bits [3:0] have dual functions depending on the addressing system being used. In the CHS mode, they hold the head number; in the LBA mode, they contain the higher bits of the logical address.

Like the SN, CR, and CL registers, the address register D/H is initialized by the hostadapter and a device places into it the address, at which it encountered an error during execution of the operation. Prior to accepting the ATA-2 specification, it was assumed that the address registers should also be modified after an operation terminated successfully to reflect the current medium address.

The status register SR (1F7h, 1 77h) reflects the current device command execution status: busy, ready, the presence of errors, etc. Reading the status register allows its bits to be subsequently changed and clears the hardware interrupt request.

The functions of the SR bits are as follows:

-

Bit 7—BSY: Busy. Indicates that the device is busy; this bit is always valid. When BSY=1, the device ignores attempts to write to the command block registers, and reading these registers produces indeterminate results. When BSY=0, the command block registers are accessible; the device cannot set the DRQ bit or change the values of the ERR bits or other registers’ contents at this time (only the values of bits IDX, DRDY, DF, DSC, and CORR may change). The bit may be set for a fleeting period of time so the host may not notice it. The bit is set when one of the following events happens:

-

Device reset.

-

A command is received and the DRQ is not set.

-

Between PIO mode data block transfers and afterward until the DRQ is zeroed out.

-

During DMA mode data transfers.

-

-

Bit 6—DRDY: Device Ready. Indicates that the device is ready to receive any commands. If the bit’s status has changed, it cannot be returned to its previous state until the status register has been read. When DRDY=0, the device only recognizes the Execute Device Diagnostic and Initialize Device Parameters commands, terminating execution of the current command and indicating this by setting the ABET flag in the error register and the ERR flag in the status register. Other commands produce unpredictable results. An ATA device sets the bit when it is ready to execute any command. An ATAPI device sets the bit prior to terminating command execution, except for the Device Reset and Execute Device Diagnostic commands.

-

Bit 5—DF: Device Fault indicator.

-

Bit 4—DSC: Device Seek Complete. In commands that allow overlapping, the bit is called SERV (Service Required) by the device.

-

Bit 3—DRQ: Data Request. Indicates that the device is ready to exchange a word or byte of data.

-

Bit 2—CORE: Corrected Data Error indicator.

-

Bit 1—IDX: Index. Treated at individual vendor’s discretion.

-

Bit 0—ERR: Error executing last command. Additional information is contained in the error register. If the ERR bit is set, the device will change neither it nor the error, sector count, sector number, cylinder, and head registers until it receives the next command, or until its hardware or software reset is executed. For the Packet and Service commands, the bit is called CEK and indicates an exception condition.

In the ATA/ATAPI-4 standard, bits 4 and 5 may have different functions in some commands and bits 1 and 2 are declared obsolete.

The function of the command register CR (1F7h, 177h) is obvious from its name. The device begins executing a command as soon as its code is written to this register. The Device Reset command is executed by an AT API device regardless of the status of the BSY and DRQ bits; it is even executed in the Sleep mode.

The 8-bit register formats described above allow only 28 bits of a logical block address to be stored (137 GB), and no more than 256 blocks to be transferred by one command. The 137-GB limitation has been overcome in the ATA/ATAPI by increasing the width of the SC, SN, SL, and CR registers to 16 bits. At the same time, the functions of their lower bytes have been preserved. The addresses of these registers in the I/O space have not changed, which is somewhat unexpected for 16-bit registers (by conventional logic, they ought to have even addresses). These registers are now “double-bottomed”: The first 8-bit access to each of them pertains to the lower byte, while the following 8-bit access pertains to the upper byte. In the LBA mode, the upper bytes of the SN, CL, and CR registers carry bits [24:31], [32:39], and [40:47] of the logical address, respectively, which provides addressing of up to 248 blocks (247 KB). The 16-bit sc register allows transmission of up to 65,536 blocks to be ordered by one command. Serial ATA block addressing is expanded in a similar way.

Data Transfer Protocols and Modes

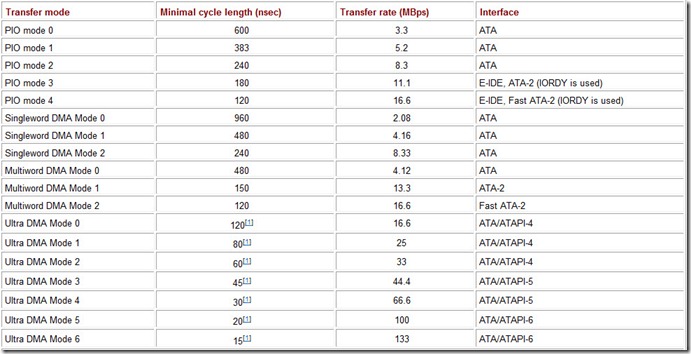

A program communicates with ATA devices that employ registers by using the IN and OUT I/O instructions. To transfer data at maximum speed, the PIO software method is used to access the data register by the INSW/OUTSW instructions or to exchange over the DMA channel. It is mandatory that all devices support the PIO access method; the DMA access method is optional. Table 8.7 lists parameters for various ex-change modes.

Table 8.7: Transfer Mode Parameters

[1]In the Ultra DMA mode burst, two data words are sent in each clock cycle: one at the positive transition of the clock, the other at the negative. The period-of the sync signals equals double the cycle time.

Programmed Input/Output (PIO) is implemented as a series of read/write operations executed at the data register address in the I/O space. Before a block is transmitted, the device readiness is checked, after which the host performs a series of operations at a set rate, which is determined by the PIO Mode selected (0-4). Each mode has the allowable exchange cycle timing parameters defined. The PIO exchange is implemented by software using processor line I/O instructions REP INS or REP OUTS with the cx register containing the number of words (or bytes) in the transmitted block. These instructions provide the maximum possible exchange rate for the particular processor and system bus. To slow down the processor according to the chosen mode is a task of ATA adapter, which uses the bus ready signal (IOCHRDY for ISA) to extend the cycle. The traditional modes 0, 1, and 2 have timing parameters to which only the host-adapter responds. The advanced ATA-2 (PIO Mode3 and higher) modes a device can slow down the exchange using the IOPDY ready signals. Software exchange occupies both the processor and the system bus during the whole time a block is being transmitted.

Exchange over a DMA channel only occupies the I/O and memory buses. All the processor needs to do is to initialize the channel, after which it disengages until the device requests its services by an interrupt at the end of the block transmission (multitask systems can take advantage of this method). ISA bus standard DMA channels are not used for the ATA interface because of their low throughput. High-efficiency ATA adapters have their own, more productive controllers. There are Singleword and Multiword DMA exchange modes. In the Singleword mode, the device generates a DMARQ request signal and clears it at the DMACK# signal that confirms the exchange cycle. In the Multiword mode, the host answers the DMARQ signal with a stream of cycles accompanied by DMACK# signals. If the device cannot handle the cycle, it can suspend it by clearing the DMARQ signal and setting it again when it is ready to resume. The Multiword mode makes it possible to achieve higher transfer rates.

A new mode—Ultra DMA—introduced in the ATA/ATAPI-4 specification makes it possible to exceed the 16.6 MBps barrier that had been specific to the traditional modes and cables. It also provides for controlling the validity of data transmitted over the bus, which was not done in the PIO or in the standard DMA mode (although it should have been!). The ATA-4 standard defined three Ultra DMA modes (0, 1, and 2); other modes were added later. A particular mode is selected by the set Features command. In the Ultra DMA mode, the DMARQ and DMACK# signals have the same functions, but the meanings of the DIOR#, DIOW# and IORDY# signals change significantly during transmission of an Ultra DMA burst. Burst data on the bus are accompanied by a strobe that is generated by the data source; moreover, both strobe signal transitions are used to clock the data. This makes it possible to increase the bus bandwidth to 33 MBps without increasing the signal switching frequency over 8.33 × 106 sec−1 (this limit for regular cable is reached in PIO Mode 4 and Multiword DMA Mode 2). Each transmitted word is used in calculating the CRC code, which the host-controller sends at the end of the burst. The calculation is performed by both the data source and receiver. If the code received by the device is not what it expected, a transmission error is recorded and the receiver indicates this at the end of the command execution. Burst transmission may be suspended if the receiver clears the ready signal (DDMARDY# or HDMARDY#). Burst transmission may be terminated by the device (by clearing the DMARQ signal) or by the host (by the STOP signal). The opposite side must confirm the end of the cycle by the STOP or DMRRQ signal, respectively.

A transmission-error reporting method depends on the type of command that caused the error. For the READ DMA, WRITE DMA, READ DMA QUEUED, or WRITE DMA QUEUED commands, bit 7 (ICRC) and bit 2 (ABRT) are set in the error register ER. For the burst command REQUEST SENSE, bit 0 (CHE) is set in the status register SR and value OBh (command rejected) is reported in the Sense key in case of an error. Errors caused by all other burst commands set the CHK bit and report status code 04h (hardware error); in the following REQUEST SENSE commands, values 08h/03h are reported for the ASC/ASCQ (a CRC error when communicating with a logical device). If the host receives an error message, it must re-execute the command. If frequent errors occur, the host must lower the transfer speed (exiting the Ultra DMA mode if necessary).

The exchange mode is determined by the capabilities of the host-adapter (and its driver), devices, and cable; for each device, it will be limited by the lowest maximum capabilities of all these devices. As a rule, the mode is set automatically by the system, but the user is allowed to customize the controller’s settings from the BIOS setup. For operations in the Ultra DMA Mode 3 and higher, an 80-wire cable is needed. Its presence must be determined by software prior to enabling one of these exchange modes. However, the specification allows a 40-wire cable without the middle connector to be used in modes 3 and 4 for a two-point connection (controller-device). The system must not allow the user to enable the high-speed mode using regular cable; in this case, it is desirable that it inform the user about the detected non-compliance. The type of cable can be determined in several ways.

-

The type of cable is detected by the host controller. For this, the host-controller must have a receiver for the CBLID# signal. Upon powering up or after a hardware reset, the host waits until the reset protocol completes and then issues the Identify (Packet) Device command to device 1. After a reset, an ATA-3 or higher device must deassert the PDIAG#/CBLID# signal no later than upon arrival of the first command. If an old device is detected, the protocol for identifying the cable by the host will not work (but with an old device on the cable, the high-speed mode should not be enabled anyway). A modern device will deassert the signal, and the host-adapter will be able to detect an 80-wire cable by the low-level signal on the CBLID# line. A faulty device may continue asserting the signal at low level; in this case, a 40-wire cable will be mistakenly identified as an 80-wire one.

-

The type of cable is determined by the device. This method does not require an additional receiver in the controller: the PDIAG#/CBLID# line on the host-controller is grounded through a 0.047$$20% microfarad capacitor. The receiver of the cable identification signal is located in the device. To determine the cable type, the host sends an Identify (Packet) Device command to device 1 (slave) ordering it to release the line (deassert the PDIAG# signal). An identification command is then sent to device 0. Approximately 30 $$sec after it receives the command, the device briefly zeroes out this line and then releases it; 20-30 $$sec later, the device reads the line’s status and reports it in bit 13 of word 93. In the devices the line is pulled by 10 K resistors to the +5 V rail. If a 40-wire cable is used, then the capacitor in the host-adapter will not have enough time to recharge, and the device will report logical zero value for the bit. With an 80-wire cable, the capacitor will be disconnected from the PDIAG#/CBLID# line in the master device, which will report logical one value for the bit. If the host-controller does not have a capacitor installed, then even a 40-wire cable will be identified as an 80-wire one, which does not bode well for data transfers. If a faulty slave device does not release the line in time, then even an 80-wire cable will appear to be a 40-wire one.

-

The combined cable type identification method presupposes both a CBLID# signal receiver and a capacitor on the host-controller (they do not interfere with each other). The decision that an 80-wire cable is present is made only if both identification methods confirm it. A possible identification error will be harmless: if there is a faulty device 1 present, the high-speed mode will not be enabled on an 80-wire cable (which is, perhaps, for the better).

A correctly selected exchange mode makes data transfer reliable and efficient. All devices support PIO Mode 0, in which a parameter identification block is read. The block contains fields that describe the default exchange mode and the most efficient exchange mode supported by the device. The exchange mode parameters can be changed by the Set Features command. Sometimes, a drive will not provide reliable data transfer in the declared high-speed mode. If data begin to get lost, the first thing to do is to lower the exchange mode.

BIOS defines the exchange mode for each device, taking into account the restrictions set during Setup. Old drives that do not provide information about their parameters may not work with the new PIO modes. The specification allows two devices supporting different exchange modes to be put on one ribbon cable (ATA channel). In real life, however, hardware and software limitations may arise. Some chipsets do not allow the exchange mode to be programmed separately for each device in the channel. In this case, if two different mode devices (for example, PIO Mode 1 and PIO Mode 3) are connected on one cable, exchange with both devices will be conducted at the lower mode device speed (in this case, PIO Mode 1). Therefore, it is not recommended to connect a fast hard drive and a slow CD-ROM to one ATA channel (IDE port). Sometimes, the restricted exchange mode selection of two devices is caused by the limited choice of parameters in the BIOS configuration. Only operating system drivers support fast multiple DMA exchange modes. A “dumb” driver may attempt to force a slow exchange mode on both devices, so this is another reason not to mix different devices on one channel.

Using the PIO exchange protocol only is suitable for single task operating systems. For a multitask operating system, exchange using the DMA protocol presents more interest; that is, of course, if the supported mode provides an acceptable exchange rate. For the driver, only the type of the exchange mode matters (i.e., whether it is PIO, DMA, or UltraDMA); hardware variations of modes within a type only affect the transfer rate. The UltraDMA mode differs significantly from regular DMA in that it has to service potential errors that occur during transmissions over the bus; if transmission errors are a constant occurrence, then the drive must switch into a lower UltraDMA mode, or move to the regular exchange modes if necessary.

The host/device interaction protocol looks as follows:

-

The host reads the device’s status register, waiting for the BSY bit’s zero value. If there are two devices, the host addresses them randomly: The status information will be provided by the device selected last.

-

When a device becomes available, the host writes a byte whose DEV bit points to the addressed device into the D/H register.

-

The host reads the main or alternative status register of the addressed device, waiting for the ready status indicator DRDY= 1.

-

The host enters the required parameters into the command block registers.

-

The host writes the command code to the command register.

-

The device sets the BSY bit and begins executing the command.

What happens next depends on the data transfer protocol specified by the command.

Commands that do not need to transmit data terminate in the next step (step 7). Having completed execution of the command, the device clears the BSY bit and asserts the interrupt request (if it has been enabled). By this time, the status and error registers contain the information about the results of the command execution. Between steps 6 and 7, the BSY bit may go low so fast that the host will not even notice it going high; however, to indicate that a command or a part of it has been executed, the interrupt request is employed.

Commands that need to read data in the PIO mode continue execution the following way:

-

With the first block of data ready for transmission over the ATA bus, the device sets the DRQ bit. If there has been an error, it is recorded in the status and error registers. The device then clears the BSY bit and sets the interrupt request (if it has not been disabled).

-

Having detected that the BSY bit has been zeroed out (or reacting to an interrupt), the host reads the status register, which resets the interrupt from the device.

-

If the host detects that DRQ= 1, then it reads the first data block in the PIO mode, addressing the data register. If an error has been detected, the data that have been read may turn out to be invalid. One of the following actions is possible when transmitting a block of data:

-

If no mistake has been discovered in step 8 and the next block needs to be transmitted, the device sets the BSY bit and steps 7 to 9 are repeated.

-

If an error has been made or the last data block has been transmitted, the device clears the DRQ bit and the execution of the command terminates.

-

For data write operations, the active phase of writing to the medium begins after step 6, which is marked by setting the BSY bit.

For commands that need to write data in the PIO mode, the procedure after step 6 continues as follows:

-

When it is ready to receive the first data block over the ATA bus, the device sets the DRQ bit (if no errors have been detected) and clears the BSY bit. If there has been an error, it is recorded.

-

Having detected that the BSY bit has been zeroed out, the host reads the status register.

-

If the host has detected that DRQ= 1, it writes the first data block in the PIO mode to the address in the data register.

-

After the data block has been transmitted, one of the following happens:

-

If an error has been detected, the device clears the DRQ bit, sets an interrupt request, and terminates execution of the command; the data that have been transmitted over the bus are not processed by the device (not written to the medium).

-

If no error has been detected, the device sets the BSY bit and moves on to the next step.

-

-

The device processes the received data block and then does one of the following:

-

If there have been no errors and the processed block is the last one, the device clears the BSY bit and sets an interrupt request; the command has been successfully executed.

-

If an error has been detected, execution of the command completes in the same way but the error bits are set.

-

If there have been no errors and another block needs to be transmitted, the procedure continues.

-

-

When it is ready to receive the next block, the device sets the DRQ bit, clears the BSY bit and sets an interrupt request.

-

When the BSY bit is zeroed out or reacting to the interrupt, the host reads the status register.

-

Having detected that DRQ= 1, the host writes the next block to the data register and the sequence is repeated starting from step 11.

Commands transmitting data in the DMA mode are executed similarly but with certain differences:

-

Direct memory access is used instead of PIO. The host must initialize the DMA channel before the code is written to the command register so that the exchange can start when the DMARQ signal appears.

-

Even in multisector transmissions, the interrupt request is set only once, upon completion of the command execution.

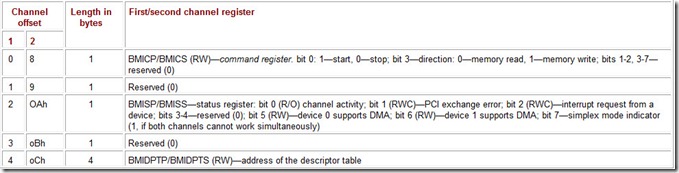

ATA Bus Adapters and Controllers

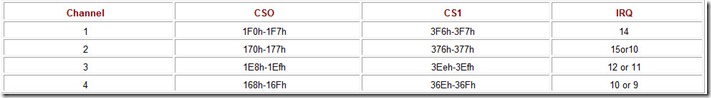

The simplest ATA adapter consists only of bus signal buffers and address range decoders. All controller registers and the coding circuitry are located in the IDE device itself. The ATA bus requires some system resources—two I/O areas and an interrupt line—to be allocated to it; a DMA channel may also be needed. The first channel ATA interface was allocated resources that used to be utilized by the HDD controller. The second channel was allocated resources that used to belong to the alternative HDD controller. Later, resources for two more channels were allocated (Table 8.8). The traditional HDD controller used to be assigned the DMA3 channel; however, it is 8 bits wide, whereas the ATA bus requires a 16-bit DMA channel. The throughput of the standard DMA channels is obviously not sufficient for the ATA bus.

Table 8.8: System Resources of the ATA Channels

Typical for PCI bus motherboards is a two-channel adapter, which is allocated the resources of channels 1 and 2. In the ideal case, the buses of two-channel controllers are totally isolated from each other by means of buffer and logic circuitry. In the cheapest case, they use common buffers for data and control signal lines and separate buffers only for especially exclusive signals. There is nothing wrong with this approach in terms of logic, but the load-carrying capacity (influence of stray parameters) must be kept in mind: The total length of both ribbon cables must not exceed 46 centimeters, and the total capacity of each line with all its devices must not exceed 35 picofarads. If these requirements are not met, data may get corrupted when transmitted in high transfer rate modes. The ATA/ATAPI-6 standard mandates the following:

-

The recommended configuration option is that each channel have its own drivers of the DIOR# and DIOW# control signals and an IORDY signal receiver. The other option is that there must be separate drivers for the CS0# and CS1# signals. This is a more logical option, but is more susceptible to interferences. This configuration supports all exchange modes, with the exception of Ultra DMA.

-

In order to provide support for Ultra DMA modes 0, 1, and 2 (up to 33 MBps), these requirements are supplemented with a requirement for a separate driver for the DMACK# signal.

-

To provide support for Ultra DMA 3 and higher (44-100 MBps), all lines must have individual transceivers. The only shared signals may be the RESET#, INTRQ, DA (2:0), CS0#, CS1#, and DASP# signals, but the standard does not recommend this arrangement.

Because the speed of software-controlled exchange is set by the host-adapter, programming individual PIO modes for each channel/device may be problematic. Several chipsets do not allow this, and set a common minimum mode when initialized. As a result, connecting a slow device will drag down the exchange rate of its faster bus neighbor.

Modern motherboards are equipped with high efficiency ATA bus controllers that support PCI bus mastering when conducting an exchange with a device in the DMA and Ultra DMA modes. Bus mastering raises overall efficiency in computers with multitask and multithreaded operating systems. By themselves, DMA modes do not provide any gains in the ATA bus exchange rate: only Ultra DMA Mode 1 and higher surpass PIO Mode 4 in speed (see Table 8.7). However, conducting exchange in a DMA mode places a significantly lighter load on the processor, so the latter may process other threads (tasks) in parallel with conducting the disk exchange. In single-task (and single-thread) systems, the processor does not have anything else to do when conducting a disk exchange, so the PIO Mode is sufficient for it. For bus mastering to be actually used, a special Bus Master driver for the ATA controller (usually built into the motherboard) needs to be installed. The standard PCI IDE controller is described below. MS-DOS does not support DMA or bus mastering. Bus master drivers may be included into the installation distributives of multitask operating systems (such as Windows 9x/NT/2000, OS/2, Unix, Linux, NetWare, etc.) or they may be included with the motherboard utilities software supplied by the vendors. Finally, the connected devices must support the DMA mode. Practically all modern devices support Ultra DMA (or Multiword DMA), but if an old device not supporting this mode is connected to the controller in pair with a modern device, then the advanced modes may turn out to be unavailable (through the chipset’s or driver’s fault) to the new device as well.

Caution

The Ultra DMA mode is attractive not only because of its speed and light processor loads, but also because of its ATA bus transfer data validity control (although this control does not work correctly with all drivers).