10.6.1 Logical Instructions

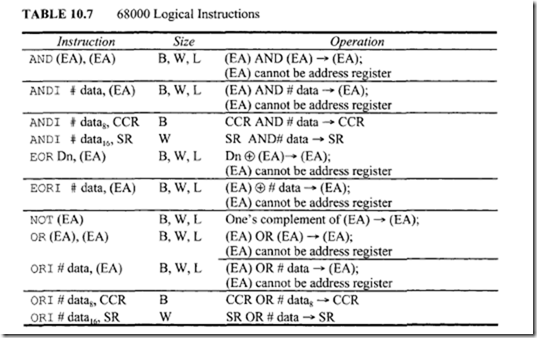

These instructions include logical OR, EOR, AND, and NOT as shown in Table 10.7.

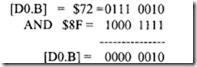

• Consider AND. B # $8 F, DO . If prior to execution of this instruction, [DO.B] = $72, then after execution of AND. B # $ 8 F, D0, the following result is obtained:

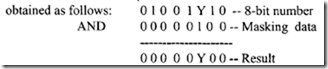

Z = 0 (Result is nonzero) and N = 0 (Most Significant Bit of the result is 0). C and V are always cleared to 0 after logic operation. The condition codes are similarly affected after execution of other logical instructions such as OR, EOR, and NOT. The AND instruction can be used to perform a masking operation. If the bit value in a particular bit position is desired in a word, the word can be logically ANDed with appropriate data to accomplish this. For example, the bit value at bit 2 of an 8- bit number 0100 IY10 (where unknown bit value ofY is to be determined) can be obtained as follows:

Z = 0 (Result is nonzero) and N = 0 (Most Significant Bit of the result is 0). C and V are always cleared to 0 after logic operation. The condition codes are similarly affected after execution of other logical instructions such as OR, EOR, and NOT. The AND instruction can be used to perform a masking operation. If the bit value in a particular bit position is desired in a word, the word can be logically ANDed with appropriate data to accomplish this. For example, the bit value at bit 2 of an 8- bit number 0100 IY10 (where unknown bit value ofY is to be determined) can be obtained as follows:

If the bit value Y at bit 2 is 1, then the result is nonzero (Flag Z=O); otherwise, the result is zero (Z= 1) . The Z flag can be tested using typical conditional ru MP instructions such as BEQ (Branch if Z= 1) or BNE (Branch if Z=O) to determine

whether Y is 0 or I. This is called masking operation. The AND instruction can also be used to determine whether a binary number is ODD or EVEN by checking the Least Significant bit (LSB) of the number (LS8=0 for even and LS8=1 for odd).

-

Consider AND. W Dl, DS. If [Dl.W] = 0001 16 and [D5.W) = FFFF 16, then, after execution of this AND, the low 16 bits of both Dl and D5 will contain 0001 16•

-

Consider ANDI .B #$00, CCR. If[CCR) = 01 16, then, after this ANDI, register CCR will contain 0016•

-

Source (EA) in AND and OR can use all modes except An .

-

Destination (EA) in AND or OR or EOR can use all modes except An, relative, and immediate.

-

Destination (EA) in ANDI, 0RI, and EORI can use all modes except An, relative, and immediate.

-

(EA) in NOT can use all modes except An, relative, and immediate .

-

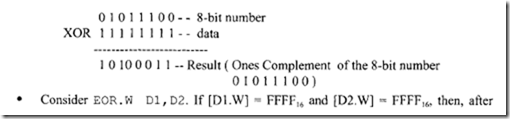

Consider E0R. W # 2, DS . If prior to execution of this instruction, [ DS. W J $2 3 4 2, then after execution of EOR. W # 2, D 5, low 16-bit contents of D5 will be $ 2 3 4 0. All condition codes are affected in the same manner as the AND instruction. The Exclusive-OR instruction can be used to find the ones complement of a binary number by XORing the number with ali i’s as follows:

execution of this EOR, register D2.W will contain 0000 16, and Dl will remain unchanged at FFFF 16•

• Consider NOT. B 05. If [D5.B] = 02 16,then, after execution of this NOT, the low byte ofD5 will contain FD 16•

• Consider OR. B 02, D3 . If prior to execution of this instruction, [D2.B] = A2 16 and lD3.B] = 5D16, then after exection of OR. B 02, 03, the contents of D3.B are FFH. All flags are affected similar to the AND instruction. The OR instruction can typically be used to insert a 1 in a particular bit position of a binary number without changing the values of the other bits. For example, a 1 can be inserted using the OR instruction at bit number 3 of the 8-bit binary number 0 1 1 1 0 0 1 1 without changing the values of the other bits as follows:

-

Consider ORI #$1002, SR. If [SR] = 111D16, then after execution of this ORI, register SR will contain lllF16• Note that this is a privileged instruction because the high byte of SR containing the control bits is changed and therefore, can be executed only in the supervisor mode.

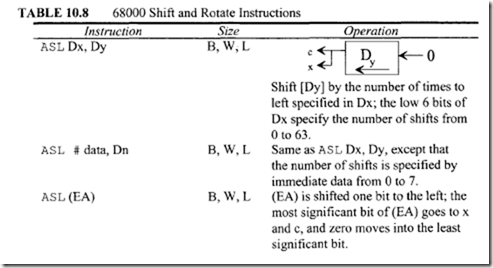

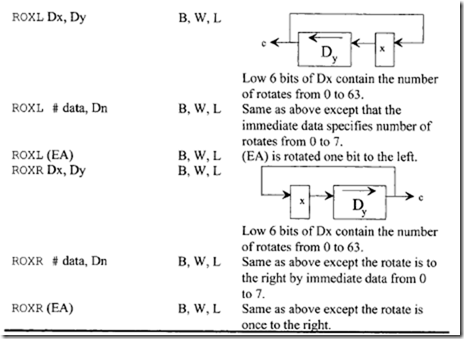

10.6.2 Shift and Rotate Instructions

The 68000 shift and rotate instruction are listed in Table I0.8.

• All the instructions in Table 10.8 affect Nand Z flags according to the result. Vis reset to zero except for ASL.

• Note that in the 68000 there is no true arithmetic shift left instruction. In true arithmetic shifts, the sign bit of the number being shifted is retained. In the 68000, the instruction ASL does not retain the sign bit, whereas the instruction ASR retains the sign bit after performing the arithmetic shift operation.

• (EA) in ASL, ASR, LSL, LSR, ROL, ROR, ROXL, and ROXR can use all modes except Dn, An, relative, and immediate.

• Consider ASL. W Dl, 05. If [D1]1ow 16 bits = 0002 16 and [D5]1ow 16 bits = 9FF0 16, then, after this ASL instruction, [D5]10w l6bits = 7FC016, C = 0, and X= 0. Note that the sign of the contents of D5 is changed from 1 to 0 and, therefore, the overflow is set. The sign bit of D5 is changed after shifting [D5] twice. For ASL, the overflow flag is set to one if the sign bit changes during or after shifting. The contents of D5 are not updated after each shift. The ASL instruction can be used to multiply a signed number by 2" by shifting the number n times to the left; the result is correct if V = 0 while the result is incorrect if V = 1. Since execution time of the multiplication instruction is longer, multiplication by shifting may be more efficient when multiplication of a signed number by 2" is desired.

• ASR retains the sign bit. For example, consider ASR. W #2, Dl. If[D1.W] = FFE2 16, then, after this ASR, the low 16 bits of [D1] = FFF8 16, C = 1, and X = 1. Note that the sign bit is retained.

• ASL (EA) or ASR (EA) shifts (EA) 1 bit to left or right, respectively. For example, consider ASL. W (AO). If [AO] = 00002000 16 and [00200016] = 9001 16, then, after execution of this ASL, [00200016] = 2002 16, X= 1, and C = 1. On the other hand, after ASR. w (AO), memory location 002000 16 will contain C80016, C = 1, and X= I.

• The LSL and ASL instructions are the same in the 68000 except that with the ASL, V is set to 1 if the sign of the result is changed from the sign of the original value during or after shifting. This will allow one to multiply a signed number by 2" by shifting the number n times to left; the result is correct if V = 0 while the result is incorrect if V = 1. Since execution time of the multiplication instruction is longer, multiplication by shifting may be more efficient when multiplication of a signed number by 2" is desired.

-

(EA) in the above instructions can use all modes except An, relative, and immediate.

-

If (EA) is memory location then data size is byte: if (EA) is Dn then data size is long word.

-

Consider LSR. W # 3, 01. If [Dl.W] = 800016,then after this LSR, (Dl.W] = 100016, X= 0, and C = 0.

-

Consider ROL. B #2, 02. If [D2.B] = B1 16 and C = 1, then, after this ROL, the low byte of [D2] = C616 and C = 0. On the other hand, with [D2.B] = B 116 and C = I, consider ROR. B # 2, 02. After this ROR, low byte of register D2 will contain 6C 16 and C =0.

-

Consider ROXL. W 02, 01. If [D2.W] = 000316, [Dl.W] = F201 16, C = 0, and X= I then after execution of this ROXL, [D1.W] = 900F16, C = I, and X = 1.

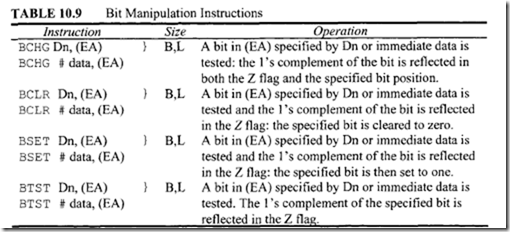

10.6.3 Bit Manipulation Instructions

The 68000 has four bit manipulation instructions, and these are listed in Table 10.9.

-

In all of the instructions in Table 10.9, the ones complement of the specified bit is reflected in the Z flag. The specified bit is ones complemented, cleared to 0, set to I, or unchanged by BCHG, BCLR, BSET, or BTST, respectively. In all the instructions in Table 10.9, if(EA) is Dn, then the length of Dn is 32 bits; otherwise, the length ofthe destination is one byte memory.

-

Consider BCHG. B #2, $0 03 0 0 0. If [003000 16] = 05 16, then, after execution of this BCHG, Z = 0 and [00300016] = 01 16•

-

Consider BCLR. L # 3, 01. If [Dl] = F210E128 16, then after execution of this BCLR, register D1 will contain F210E120 16 and Z = 0.

-

Consider BSET. B #0, (Al). If[AI]= 00003000 16 and [00300016] = 0016, then, after execution of this BSET, memory location 003000 16 will contain 01 16 and Z = 1.

-

Consider BTST. B #2, $0 02 0 0 0. If [002000 16] = 02 16, then, after execution of this BTST, Z = 1, and [00200016] = 02 16; no other flags are affected.

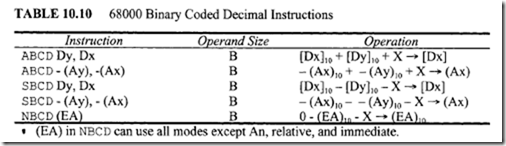

10.6.4 Binary-Coded-Decimal Instructions

The 68000 instruction set contains three BCD instructions, namely, ABCD for adding, SBCO for subtracting, and NBCO for negating. They operate on packed BCD byte(s) and provide the result containing one packed BCD byte. These instructions always include the

extend (X) bit in the operation. The BCD instructions are listed in Table 10.10.

-

Consider ABCO.B D1, D2. If[Dl.B] = 25 10, [D2.B] = 1510, and X= 0, then, after execution of this ABCO instruction, [D2.B] = 4010, X= 0, and Z = 0.

-

Consider SBCO. B – (A2) , – (A3). If [A2] = 00002004 16, [A3] = 00003003 16, [002003 16] = 0510, [003002 16] = 0610, and X= 1, then after execution of this SBCD instruction, [00300216] = 0010, X = 0, and Z = 1.

-

Consider NBCO. B (Al). If[A1] = [0000300016], [00300016] =0510, and X= 1, then, after execution of this NBCO instruction, [00300016] = -610 •

Note that packed BCD subtraction used in the instructions SBCO and NBCO can be obtained

by using the concepts discussed in Chapter 2 (Section 2.5.2).