10.7 68000 Delay Routine

Typical 68000 software delay l00ps can be written using MOVE and DBF instructions. For example, the following instruction sequence can be used for a delay l00p of 2 millisecond:

Note that DBF.W in the above decrements D0 .W by one, and if DO.W "’ -1 branches to DELAY; ifDO.W = -1, the 68000 executes the next instruction. Since DBF.W checks for DO.W for -1, the value of "count" must be one less than the required l00p count. The initial l00p counter value of "count" can be calculated using the cycles (Appendix D)

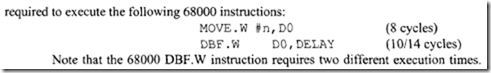

required to execute the following 68000 instructions:

DBF.W requires IO cycles when the 68000 branches if the content of D0.W is not equal to -1after autodecrementing D0.W by I. However, the 68000 goes to the next instruction and does not branch when [D0.W] = -1 after autodecrementing DO.W by 1, and this requires 14 cycles. This means that the DELAY l00p will require 10 cycles for "count" times, and the last iteration will take I4 cycles.

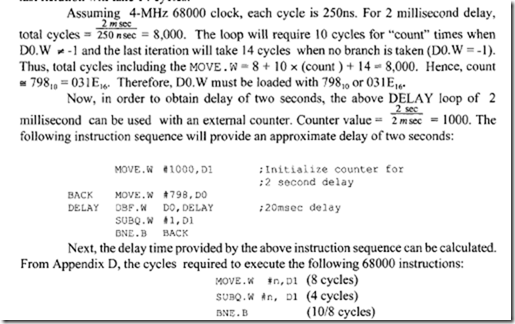

As before, assuming 4-MHz 68000 clock, each cycle is 250ns. Total time from the above instruction sequence for two-second delay= Execution time for MOVE.W + 1000 * (2 msec delay)+ 1000 *(Execution time for SUBQ.W) + 999* (Execution time for BNE.B for Z = 0 when Dl ..- 0) +(Execution time for BNE.B for Z = 1 when D1 = 0 for last iteration) = 8 * 250ns + I 000 * 2msec + 1000 * 4 * 250ns + 999 * 10 * 250ns + 8 * 250ns = 2.0035 seconds which is approximately 2 seconds discarding the execution times of MOVE.W, SUBQ.W, and BNE.B.