How Chips Are Made

In this chapter…

Clean Rooms and Fabs

Developing Technology: Chips and Photography

Silicon Ingots to Start

Polishing the Wafer Smooth

Building the Layer Cake

Laser Surgery: Etching Away the Transistors

Step and Repeat

Etching Bath

Ready for the Metal Round

Testing Phase I

Bringing out the Diamonds

Sorting the Fast From the Merely Good

Wrap It Up

How Many Nanometers in a Micron?

Let’ s Get Small

Silicon chips are made in a process that’s a combination of the familiar and the bizarre. Some aspects are as familiar as developing a few photographs, whereas others resemble space exploration or subatomic physics. In the end, it’s all of these and the process gets stranger and more fascinating the more you learn about it. In this chapter we take a brief tour as a hypothetical chip we’ve designed makes its two-month journey through a chip factory.

Chips might seem small and flat, but they’re really three-dimensional sandwiches 10 or 20 layers thick. It takes more than two dozen steps to build up this silicon sandwich, and plenty of things can go wrong along the way. It’s not until near the end, however, that you discover whether the chip is any good or not. Chips destined for the trash can cost just as much to manufacture as those headed for new PCs, so quality control is important, and manufacturing secrets are closely guarded.

Many chip-making companies are well known, and firms like Intel, Motorola, and Texas Instruments get plenty of credit for advancing the industry, but it’s really the behind-the-scenes companies that develop the chip-making equipment that deserve the glory. Companies like ASM Lithography, Applied Materials, and Ultratech Stepper (to name just a few) are responsible for moving the semiconductor industry forward at such a rapid pace. To some extent, the Intels of the world are only using the tools they’re given. Without these exotic and leading-edge tools, our world of computers, satellite communications, and consumer electronics would not be where it is today, or where it is headed tomorrow.

Clean Rooms and Fabs

Chip factories are called fabs, short for fabrication facilities. A fab looks like a normal two- or three-story office building from the outside. It’s the inside that’s special. Although most fab buildings do include some normal office space for the employees, most of the interior space is dedicated to one or more “clean rooms.” It is inside these clean rooms that chips are made.

The term clean room understates the truth. These rooms are phenomenally, spectacularly, unbelievably clean. The best hospital operating room is filthy in comparison. Clean rooms are from 1,000 times to 10,000 times cleaner and more sanitary than any operating room. They are designed with fanatical attention to details that will keep the entire room immaculate and dust-free. Stainless steel is used everywhere; floors and ceilings are perforated with holes and the air conditioning keeps the air moving through them all the time. Surfaces are sloped and flat tabletops are avoided because they give dust a place to settle. Bright, slightly yellowish lighting prevents mildew from forming in the recessed corners of equipment or behind desks.

Even the workers in a clean room are kept astonishingly spotless. Everybody wears the now familiar “bunny suits,” as shown in Figure 4.1. Looking like astronauts, the people working in the clean room are covered from head to toe, walking amid polished chip-making equipment like explorers in a science fiction movie. To enter the clean room you must pass through a series of air lock doors, pass through an “air shower” that blows dust off your clothes, and walk across a sticky floor mat that removes grime from the bottom of your shoes. Suiting up in the stainless steel locker room requires at least 10 minutes. Another pass through the air shower blows any remaining contamination off the outside of the bunny suit. Completely sealed in a bulky suit, helmet, battery pack, gloves, and boots you pass through another set of air lock doors into the clean room. Workers learn to identify each other by their eyes alone.

Inside, the clean room is quite long and narrow, a bit like a corridor in a submarine. Tall stainless-steel equipment lines each side of the walkway. A constant breeze blows down from the ceiling to the open-grate floor to discourage dust particles from settling on flat surfaces. Occasional windows might let you see some of the offices near the clean room; there are no windows to the outside. Push-to-exit fire doors are to be used in case of dire emergency only.

Developing Technology: Chips and Photography

If you’re an amateur photographer, you’ll already understand most of what’s involved in making silicon chips. The technique is amazingly similar to the process of developing prints from film negatives. In both cases you start with a sharp negative image on film, which is then projected onto light-sensitive paper resting in a bath of special chemicals. You control exposure, light, and the chemicals to produce just the image and effects you want. You can also enlarge or reduce the image, if desired. Once you’ve made the first print, it’s relatively easy to produce several more just like it.

If you substitute silicon for paper, you’ve got a pretty accurate description of how chips are made, too. It’s basically a photographic process, albeit an extremely accurate and precise one. It’s so precise, in fact, that all the equipment must be kept 100 times cleaner than a surgeon’s instruments and all the people involved in the process wear astronaut-like sealed spacesuits to prevent contamination. Whereas a photographer’s darkroom must be kept dark, a chip factory is brightly lit. The “light” used to develop chips is invisible to the human eye.

Unlike a conventional photograph, though, each “print” of a chip is developed from several different film negatives. A typical chip might require 10 or 20 different layers of film. This is where chip making starts to resemble building a layer cake. Every chip is built of layer on layer of silicon, aluminum, and other chemicals stacked on top of each other like a layer cake or a three-dimensional puzzle. Each layer of this tasty product is developed using a separate piece of film.

Silicon Ingots to Start

The first step in making any silicon chip is getting the silicon, of course. Silicon is basically purified sand; it’s one of nature’s elements and, thankfully, one of the cheapest and most plentiful. For the chemists in the audience, silicon is element 14, right between aluminum and phosphorus on the periodic table of elements. For the nonchemists in the audience, silicon is not the same as silicone, the stuff that lubricates squeaky door hinges or maintains the business of cosmetic surgeons.

Silicon crystals are melted in a vat and purified to 99.9999 percent purity and grown into ingots, long sausage-like cylinders that are heavy and shiny, as shown in Figure 4.2. If you’ve ever grown sugar or salt crystals in a drinking glass as a science experiment, the process is exactly the same, just done on an industrial scale.

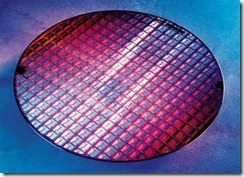

The ingot is cut into very thin slices called wafers, shown in Figure 4.3. Wafers are round, of course, and about as thick as a business card. Wafers come in a few standard sizes, usually 6 inches, 8 inches, or 300 millimeters (just under 12 inches) in diameter. One edge of the otherwise round wafer is traditionally cut off straight. That’s partly to help the automated equipment handle the wafer, but also so the people operating the equipment can tell which way is “up.” The flat edge also prevents the wafer from turning or spinning as it rests inside some of the equipment.

Polishing the Wafer Smooth

Before the real work begins, one side of each wafer must be polished absolutely smooth. These wafers will be so smooth after they’re finished that you couldn’t detect any imperfections on the surface even with a microscope. The process is called chemical-mechanical polishing (CMP). As the name implies, it involves bathing the wafers in special abrasive chemicals and gently grinding any imperfections away.

The wafers need to be smooth and flat because the features that will be projected onto them in the chip “darkroom” are extremely small and close together. In photography, it’s important to keep the print lying flat as it develops because any warping or bending will throw the picture out of focus. Each part of the print must be the same distance from the projecting lens, and the principle is the same for chip making. Any variations in the surface of the silicon wafer will make the chip design out of focus, possibly causing shorts and other faults.

Building the Layer Cake

After a wafer is polished, it’s time to start building up the layers of material that will become the transistors on our chip. A wafer is pure silicon, but it takes more than silicon to make a chip work. There are the metal wires, of course, but those will be added later. At this stage, we need to build up a few layers of silicon (which conducts electricity) alternating with a few layers of an insulator (which doesn’t conduct electricity). These two types of material will be stacked, like layers of frosting between layers of cake. Later, we’ll etch away some of this insulator (most of it, actually), leaving a carefully planned-out three-dimensional pattern of silicon and other materials that channel electricity in exactly the paths we want.

Engineers call this layering process deposition because chemicals are deposited on the supersmooth surface of our wafer. Deposition can be done in a couple of different ways. One way is to put the wafer in an oven along with pure oxygen gas and let the oxygen seep into the top of the wafer. (Oxygen doesn’t conduct electricity; it is an insulator.) Another way is to spray the chemicals onto the wafer, called chemical vapor deposition (CVD). After we’ve built up the first layer of our chip, it will look like Figure 4.4.

After we coat the wafer with insulating chemicals, there comes a second layer of special chemicals, this one called photoresist. Photoresist is like the coating on black-and-white print film before it’s been developed. The stuff reacts to light, which we’re depending on to make our chips work.

Laser Surgery: Etching Away the Transistors

Once the wafer is coated with photoresist, it’s light sensitive and must be kept in the dark so that it doesn’t accidentally get “developed” before it’s ready. Fortunately for us, the photoresist is sensitive to light we can’t see, so there’s no need to shut off the lights in the clean room. The wafer still needs to be handled carefully, however, to avoid scratching its delicate and carefully prepared surface.

To develop the wafer, we put it into a machine called a stepper. Usually a robot arm takes a wafer off the top of a stack and places it in the stepper automatically. Mounted just a few inches above the wafer is a copy of the film negative that the chip designers created (which was described in the previous chapter). Engineers call this film the reticle, and it’s usually made of quartz instead of normal camera film. Just above the film is a lens and behind that is a bright light. Basically, we’re going to project an image of the film down onto our wafer, like projecting slides onto a wall (see Figure 4.5). The only real difference is the scale: The image we project will be tiny, only a fraction of an inch on a side, just big enough to make one copy of our chip.

The other difference is in the light used in our “slide projector.” It’s not really light at all, in the usual sense. Human eyes can’t see it, for example. Chip images are projected using light that’s closer to lasers or x-rays than normal light. (Sometimes they really are x-rays.) The reasons for this are a bit complicated but have to do with wavelengths. Normal light has a tendency to bend around objects, making fuzzy shadows. Look outside and notice how the sun shining through a leafy tree casts slightly fuzzy shadows on the ground. The edges of the shadows aren’t sharp. In fact, very thin objects, such as a thread or a spider web, often don’t cast shadows at all because sunlight tends to bend around these small objects.

That kind of fuzziness won’t work at all for making chips. We need to cast shadows that are razor sharp, especially for small objects because the transistors and wires on our silicon chip are going to be microscopically tiny. Steppers therefore use light sources that are a lot closer to x-ray machines than slide projectors. That’s why these basically simple machines are 10 feet high and costs millions of dollars (see Figure 4.6). They are designed and calibrated to the nth degree to project extremely sharp, fine, focused images through the film onto our wafer.

As the light shines through the film and onto the wafer below, it shines on the photoresist, which reacts to light and starts to harden. After a few moments of this illumination, all the photoresist that was exposed to light has “set up” and made a tough crust on top of our wafer. All the parts of the wafer that were in shadow, however, are still soft, and that’s exactly what we want.

Step and Repeat

What good is it to make just one copy of a little chip onto a big wafer? Don’t we need to fill the whole wafer with hundreds of copies of the chip? Indeed we do, and that’s why these machines are called steppers. After projecting one image onto the wafer long enough for the photoresist to harden, the stepper moves the wafer slightly to the left and projects the image through the reticle again. After that chip is done, the wafer moves over one more position, and again the process is repeated. Like plowing a field from one corner to the other, a stepper passes from left to right, and top to bottom until the entire wafer has been exposed (see Figure 4.7). The entire process takes just a few minutes.

Why not use a bigger piece of film and expose the entire wafer at once? Wouldn’t it take less time and cost less money to do all the chips in a single exposure? The reason is one of focus. As owners of big-screen TVs know, the sharpness of a picture deteriorates as it gets bigger. Photographers also know that big poster-size prints are blurrier than small 5 x 7 portraits. That’s just the nature of photography and light. Steppers can’t afford to sacrifice sharpness for speed. Each chip has to be absolutely sharp and perfect. It doesn’t make sense to mass-expose an entire wafer if all the chips around the edges will be thrown away.

Amazingly, even the corners of normal chips are a bit blurry. Only the center of the chip is truly in focus. Intel produced an extraordinarily large chip in the early 1990s that was octagonal instead of square. The corners had to be cut off because they would have been too badly out of focus to work.

Etching Bath

Now that the entire wafer has been exposed with dozens of images of our little chip, it’s time to use a little chemical wizardry to start cutting away the parts we don’t want. If we bathe our wafer in a bath of just the right chemicals, all the soft parts of the photoresist (the parts that weren’t exposed to light) will wash away, along with the insulating chemicals that were underneath. The hardened areas of photoresist, however, will protect the insulating material beneath them.

We’ve photographically carved away part of our layer cake, leaving tiny valleys in exactly the places we want. It’s as if we’d taken a very sharp knife and carefully sliced away some parts of the chip, although no surgeon’s scalpel is sharp enough (and no hands steady enough) to do this manually (see Figure 4.8). Even robots could not be made skillful enough. Ever since the first days of semiconductor manufacturing, chips have always been made using this photographic process.

This cycle of depositing chemicals, covering the wafer with photoresist, exposing it to light through our film mask, and etching away the unexposed parts gets repeated more than a dozen times. Over and over, we’ll build up layers of material in elaborate three-dimensional constructions to create the transistors that make up our chip.

Ready For the Metal Round

Although chips are made of many layers, the transistors are all near the bottom. The upper layers are for the metal connecting wires. That means the size of a chip is determined mostly by the number of transistors it has, not by the amount of wiring it requires. That’s what pushes semiconductor manufacturers to constantly shrink the size of their transistors: The smaller the transistor, the smaller the chip (or the more transistors you can fit on a same-sized chip). The smaller the chip, the more you can fit on a wafer. The more chips on a wafer, the more you can sell for the same amount of work. Moore’s Law is just good old capitalism at work.

After the transistors are built up on our chip, it will go through the same process several more times to build up the “metal layers.” These are the copper or aluminum wires that connect the transistors together. The amount of wiring depends on the complexity of the chip. (Remember the houses-and-utilities puzzle from Chapter 3, “How Chips Are Designed”?) Some chips might have only three or four layers of wiring; complex chips might have eight or more.

The process of applying metal is the same as for the other layers that were put on earlier. First, the entire wafer is covered with an insulating material that runs into all the cracks and grooves of the chip (it won’t be smooth anymore). Then a thin layer of metal, either aluminum or copper, is applied on top of that. Finally, a layer of photoresist covers the metal.

Tech Talk

Around 1996, the whole process of using copper wiring in chips got a lot of coverage in the press. It’s not clear why this happened, because this abstruse facet of chip manufacturing was of little interest to the general public and of even less interest to those in the industry, who had known about it for some time. Copper certainly makes a better electrical conductor than does aluminum, as any electrician or homeowner will confirm.

The major reason copper wasn’t adopted sooner was cost. Although chips use a tiny amount of copper, the billions of chips produced each year add up to a significant drain on this limited resource. Gold is an even better conductor than copper, and perhaps future “designer chips” will flaunt their gold wiring.

Now the wafer goes under another stepper with a different piece of film. Again the stepper exposes the photoresist, and again it sets up and protects the metal we just applied. After it’s washed away, the net result is that some of the metal remains, although most of it will be eaten away, leaving very thin metal lines or wires. Depending on which company is making the chip, there might be gaps underneath the metal wires. Other companies use a slightly different process that leaves material under the wires for support.

This process will be repeated several more times, each time building up another layer of metal wires atop the previous layer. Each layer of this elaborate cake is separated by a layer of insulating material so that wires crossing over each other don’t touch and short out.

Testing Phase I

After several passes through the deposition-expose-etch-repeat process, our chip is finished! It takes, on average, 20 to 30 individual steps to finish a chip of medium complexity. By this time, the chip has been in production for several weeks and has passed through dozens of people’s hands and almost as many robotic handlers. In short, an enormous amount of expensive time and effort has been expended to produce this wafer full of chips. Now it’s time to see how many of them actually work.

When a new fab is built, it’s a sad reality that practically all of the chips it produces for the first few weeks will probably be bad. Hundreds of wafers will be processed, representing thousands of chips, and not one of them will work. Over time, the production yield will improve, but it’s usually not until a fab has been operating nonstop for more than a year that production yields will surpass 90 percent. Some fabs never do; for whatever reasons, they will always throw out 20 percent or more of everything they produce.

One of the reasons for this high “mortality rate” is contamination in the clean rooms. A new fab necessarily has some dust left over and it takes time for the air filters and extractors to scrub the atmosphere in the clean room to the extraordinary levels required. Also, the new equipment needs to literally settle in to the new building. Minor shifts in the floor or walls as the building’s foundation settles can wreak havoc on the sensitive steppers and other equipment. Companies have been known to reroute foot traffic around clean rooms to avoid upsetting sensitive equipment with heavy footsteps. Oddly, some equipment just never seems to acclimate; sometimes replacing a finicky machine is the only option.

For a variety of economic reasons, it’s important for chip companies to test each chip as early as possible in its life span. The sooner you can identify a bad chip, the sooner you can stop spending money on it. The first step in this process is called wafer probing. While all the chips are still together side-by-side on a single wafer, the entire wafer is put under a tester. Like a mechanical spider, the tester lowers several delicate wire legs and places them gently on the edges of a chip. It applies a voltage and tests the chip’s reaction. Does everything turn on and off when it’s supposed to? Does the chip respond quickly enough, or perhaps too quickly? Any behavior out of the ordinary probably signals a fault and a chip that’s doomed to the dustbin. Faulty, or even suspect, chips are quickly marked with a tiny dot of red paint. Later on they’ll be cut away from their siblings and discarded. This is the source of many high-tech lapel pins, tie tacks, and paperweights.

Bringing Out the Diamonds

Assuming that at least some chips pass inspection and the entire wafer isn’t bad, all the chips will be cut apart using a diamond-bladed saw. The stepper leaves a bit of space between each chip as it moves left to right and top to bottom. This blank area allows the saw to carefully cut in between the chips without damaging them. The diamond saw is very thin, as you might imagine, and is designed to kick up a minimum of “silicon sawdust.” Contaminating an entire wafer at this late stage would be economically unpleasant.

After the chips are cut apart, the good chips are sorted from the bad chips by a robot that searches for the tell-tale red dot. Also, the cut-off fringes of the round wafer are discarded like high-tech cookie dough. Unfortunately, this material can’t be recycled because it’s been too heavily treated, exposed, and processed to be of any use as a raw material.

Chips that have been cut apart are called die. One chip is one die but several chips together are also called die, not dice. There’s no particularly good reason for this grammatical inconsistency.

Sorting the Fast from the Merely Good

Once each chip is tested to see if it’s functional, it’ll often be tested again to see exactly how fast it is. Natural (although unwelcome) variations in manufacturing will make some chips work slightly faster than others. If the difference is significant (say, 20 percent faster) and if the numbers of these overachieving chips are also significant (about 20 percent or more) then it’s probably worthwhile to sell them at a premium price. For highly profitable microprocessor chips for PCs and other computers, this extra financial gravy can be more than $100 per chip.

Other times, it’s not worth the trouble to sort the chips by speed. If a good chip sells for only $1.25, a fast one is unlikely to command a premium of much more than 25 cents. For that amount, it’s more cost-effective to skip the testing and sell all the parts at the same price. This means some enterprising customers or technicians might be able to discover a few chips in their monthly shipment that are faster than advertised, but that’s for them to discover.

Even when faster than average chips do carry a price premium, chip companies will intentionally avoid selling them as such for marketing reasons. Early in a chip’s product life, there might be relatively few that make the faster speed cut. Later on, as the manufacturing process matures and the yield improves, there might actually be too many faster parts. The chip maker can arbitrarily limit the number of such parts to, say, 15 percent of the total product offering to maintain the aura of exclusivity surrounding the higher priced part. Technically astute PC hobbyists call this “overclocking.” They will test their computer’s chips at home to see what the upper limit of performance is, fine-tuning their PC to extract the maximum possible performance from each chip. Half of the appeal is appearing to cheat the chip maker out of a few extra dollars.

Wrap it Up

Eventually each chip needs to be wrapped up in a package so it can be handled and shipped without damage. Most chips are housed in plastic packages that look like little black houses. (Chips are universally black; it’s traditional.) The bare silicon is not simply dipped in melted plastic or sprayed with a covering because that would damage the delicate device. Instead, they’re packaged clamshell style, as shown in Figure 4.9. First the chip is laid in the lower half of a plastic package, usually on a spot of glue to hold it still; then the upper half of the package is cemented to the bottom. A hollow cavity in the middle leaves room for the chip and avoids crushing it.

Finally, the outside of the package is marked with some lettering, one or two identifying part numbers, a date code that indicates when the chip was manufactured, and, if there’s enough room, a company logo. The lettering is usually just stamped on with ink, but large chips are sometimes marked with a laser that burns the letters onto the outside of the package. This latter process is fascinating to watch and makes good promotional video footage for the companies that use it.

After the chips are packaged, they’ll be completely tested once again. A few chips are damaged during packaging so it’s important to make one last check to be sure everything’s in order. If any chips fail at this point, they’re just thrown in the trash.

A few chips never get packaged. Some very high-volume customers prefer to receive their chips “naked.” These are called known-good die (KGD). If a customer prefers to work with KGD it’s usually because they’re combining several bare chips together into something called a multichip module (MCM). MCMs are like chip apartment houses: several chips sharing a single package. An MCM package is comparatively large, about the size of a matchbox. Usually military contractors or aerospace companies build MCMs because they can pack the chips very densely together and shield the entire assembly against radiation, such as a spacecraft might encounter in orbit.

How Many Nanometers in a Micron?

It’s hard to overhear any discussion of chip manufacturing for more than a few minutes without hearing about microns or nanometers. (Okay, it’s hard to listen to any discussion of chip manufacturing at all, but that’s not the issue here.) These two terms describe exactly how small the transistors and metal wires on a chip are. For clean room workers and manufacturing technicians, microns and nanometers are everything.

Both terms are simply measurements. In fact, they’re measurements of the same thing. One micron is exactly one one-millionth of a meter (0.000001 meter). For fans of English measurement, that’s about 25,000 microns to the inch (see Figure 4.10). For comparison, a human hair is about 50 microns thick, so we’re talking about very small measurements here.

Yet a micron is a vast distance to a chip manufacturer. Individual transistors are smaller than a single micron across, and have been since the early 1990s. Starting around 2001, manufacturers started producing the first transistors that were smaller than one-tenth of a micron (0.1 micron), leading to some tongue-twisting dimensions, even for engineers. So rather than continue to speak in fractions of a micron, silicon engineers began using the next smallest unit of measure, the nanometer.

A nanometer is one one-billionth of a meter (0.00000001 meter), or 1,000 times smaller than a micron. For comparison, a single hydrogen atom is only about 0.25 nanometers across (assuming one can measure these things). Amazing as it seems, we are rapidly approaching a time when the thickness of these materials will be measured by counting their atoms.

Let’ s Get Small

What exactly are these engineers measuring with their very small rulers? They measure something they call effective length, often abbreviated Leff in engineering lingo. Broadly speaking, the effective length is the thickness of the thinnest thing that can be manufactured reliably. Effective length depends very much on the maturity of the fab and its equipment, the experience of the technicians in the clean room, the company’s tolerance for risk versus aggressiveness, and the amount of money it’s willing to invest in the process. The best (i.e., the smallest) effective length achievable varies from company to company, and even from fab to fab within a company. Some large companies operate a few fabs on the cutting edge of current technology while keeping a few other fabs one half-step back, running at more conservative dimensions. This allows them to produce both very fast chips (with risky yield profiles) and very reliable chips (with commensurately higher yields).

The state of the art in fab technology moves in distinct jumps every few years. In years past, the best companies were producing 0.25-micron transistors. Then these companies made a change to 0.18-micron processes, more or less all at once. Following the 0.18-micron generation came the 0.13-micron generation, and so on. The reason these firms—competitors all—adopted the same technology simultaneously is that they bought it from the same suppliers. With very few exceptions, chip manufacturers don’t make their own chip-making equipment; they buy it on the open market. The situation is not dissimilar to warring countries buying weapons from the same small group of arms merchants.

The number of these silicon merchants is shrinking. It gets harder and harder to develop machines that can produce finer and finer slivers of silicon. Indeed, many well-informed industry observers predicted that we’d never get this far. Serious technical obstacles reared their heads in past years that threatened to put a stop to Moore’s Law and halt the continual rate of improvement we’ve come to take for granted. Yet each time, semiconductor equipment suppliers have found more elaborate (and expensive) solutions to these problems. However, the staggering cost of research and development into these technologies weeds out a few suppliers at each process generation. Now former competitors are cooperating, sharing the multibillion-dollar development costs of reaching the next step in semiconductor evolution.

A big part of the challenge is finding sources of light with short wavelengths that are bright and strong enough to resolve small, sharp images into a wafer. As the effective length of film features gets smaller and smaller, it’s harder and harder to project a sharp image onto a wafer’s photoresist. Every process shrink, from 0.18 micron (180 nanometers), to 0.13 micron (130 nanometers), to 90 nanometers, and so on, makes projecting accurate images tougher. The light tends to bend around the microscopically small features on the film, blurring the image and ruining the chip.

Equipment makers have been experimenting with exotic-sounding techniques like i-beam lithography, e-beam epitaxy, x-ray sources, and extreme ultraviolet (EUV) lithography. Each approach has its pros and cons, and researchers are likely to develop at least two into working equipment. Despite the recurring cries of Chicken Little, the sky appears to stay firmly above the heads of the developers of this vital technology.