Signal-processing IC package

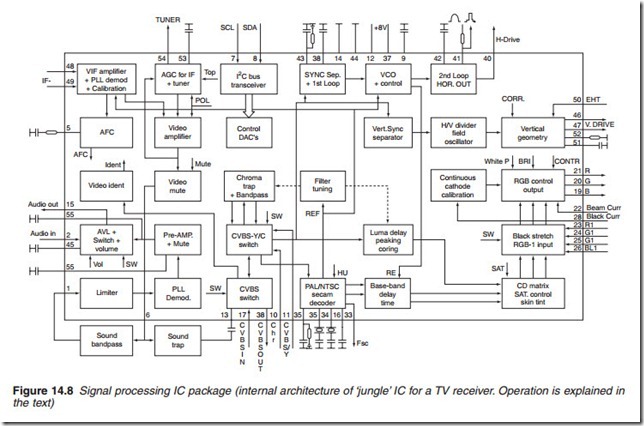

All the low-level signal-processing stages in a colour TV are amenable for integration on a single chip, an example of which is given in Figure 14.8. At the top left-hand corner, the IF signal from the SAW filter enters the vision IF amplifier and PLL demodulator. From here is produced an auto- matic frequency control (a.f.c.) potential for the tuner – it counteracts drift of the input carrier or the tuner itself. Baseband video signal, complete with inter-carrier sound, passes down to the video amplifier block. Taking first the ‘auxiliary’ outputs from here, a sample goes up to the a.g.c. sec- tion, whose link to the tuner feeds back information on signal strength at high input levels. A video mute block prevents noise in the form of ‘snowy screen’ being displayed in the absence of a transmission, and from this the video signal comes out of the IC on pin 6. The sound carrier is selected by a ceramic filter (‘sound bypass’) to re-enter the IC on pin 1, where it encoun- ters a limiter stage to clip off any amplitude modulation. A PLL FM demodulator follows from which the baseband (mono) audio signal passes through a mute/pre-amp/de-emphasis stage on its way out of the IC on pin 15. It is intercepted by a switch – under I2C bus control – to

enable other sources of audio, entering on pin 2, to be selected (along with external video on pin 17) when the set is switched to AV mode.

The main path for the video signal is out of IC pin 6 and through a sound trap, sharply tuned to 6 MHz, into chip pin 13. Here it encounters two routing switches, both working under I2C-bus instructions. The first of them selects between internal and external (coming in on pin 17) com- posite video; the second selects composite or Y/C signals, the latter enter- ing on IC pins 11 (Y) and 10 (C). We shall meet Y/C signals later. Pin 38 gives a route out for the composite signal, typically via an AV socket. The chroma trap and bandpass block is used to separate the video and colour sub-carrier signals contained in a composite video signal. The entire PAL decoder, also capable of NTSC and SECAM operation, is contained in the bottom centre block in the diagram. The delay line is catered for by on- chip components. The components at IC pin 36 provide time-constants for the sub-carrier flywheel filter, while 4.43 and 3.58 MHz crystals at pins 35 and 34 respectively regenerate colour sub-carriers for PAL and NTSC signals. In the latter case, hue control is affected via the I2C control bus. R – Y and B – Y are separated in the internal baseband delay line on their way to a colour difference/RGB matrix in the bottom right-hand side of the diagram. This also incorporates the saturation (colour) control. Luminance signal on its way to the RGB matrix is optimised in the peak- ing/’coring’ block, and delayed to coincide with the lower-bandwidth, slower-rising chrominance signals.

RGB signals from the chip internal decoder pass into the primary- colour switch, where selection is made between them and signals entering on pins 23/24/25, usually from a teletext decoder. ‘Black stretch’ provides level-dependent amplification to low-level (near black) video signals if required. The final picture-processing block in the chip is centre-right, RGB output. As well as providing buffered feeds out to pins 21/20/19, this provides brightness and contrast control for each of the three chan- nels: separately and in parallel, so that external RGB input signals, when selected, can also be controlled. Brightness and contrast settings are pulled back when the voltage entering on IC pin 22 indicates that the beam cur- rent in the picture tube is near the point at which its shadow mask will hot-bulge. Also present here is an auto greyscale correction system in which the black current sample enters the chip on pin 18 for entry to the cathode calibration block. RGB signals pass through a two-stage amplifier, usually mounted on the tube base panel, on their way to the cathodes of the picture tube.

It remains to trace the path of the synchronisation pulses. At top centre of the diagram of Figure 14.8, the sync separator stage is fed with com- posite video signal, from which it strips out line sync pulses and feeds them to a comparison stage which keeps the TV line frequency in step with the broadcast picture. Line drive pulses from IC pin 40 switch the line output stage at 15.625 kHz for PAL operation. A second feed from the com- posite video signal operates the on-chip vertical sync separator. The result is a single ‘clean’ pulse once per field to reset an H/V divider, a counter circuit which triggers field flyback every scanning line. Thus synchronised to the broadcast signal, the field oscillator’s drive waveform passes through a shaping stage (vertical geometry) on its way out of the IC on pins 46 and 47. There are two influences on the vertical geometry correc- tor: a feed coming into IC pin 50 contains a sample of EHT voltage to pre- vent the picture size changing with beam current; and from within the chip, a correction factor by which – under I2C bus control – the vertical scanning current can be adjusted in amplitude and shape to render good picture geometry and linearity. Control of all the functions of the IC depends on the I2C bus transceiver near the top centre of the diagram; it governs all the switches in the chip, plus the D-A converters which set parameters like colour, brightness, contrast and sound level as well as fac- tory/technician settings such as picture-white points and vertical scan correction. For information on the SCL and SDA control I2C bus which enter this chip on pins 7 and 8, refer to Appendix 2. To round up some of the pins not so far mentioned, pins 12 and 37 provide a +8 V operating voltage; pin 33 provides a sample of locked colour sub-carrier; pin 26 takes a picture-blanking pulse from the text decoder for use when text is super- imposed on a picture; and pin 41 has the dual purpose of dispensing a sandcastle pulse output and receiving a flyback input from the line scan stage. There are other pins and functions of this 56-pin package which are not absolutely essential to the main operation.