Z80 Microprocessor Architecture

The Z80 is one of the most versatile and widely used 8-bit microprocessors, and many microprocessor-based systems are designed around the Z80. The Z80 chip includes most of the logic circuitry for performing computing tasks and necessary bus signals. This topic discusses the Z80 architecture in terms of the generalized MPU discussed in the previous topic .

This topic describes the Z80 hardware model; it shows logic pinout of the chip and classifies the signals in various groups according to their functions. Similarly, the topic includes a brief description of programming registers and flags. The hardware model lists the operations the Z80 frequently performs and describes how the Z80 communicates with memory and I/Os by using various buses. These operations are illustrated in terms of machine cycles and logic levels of the buses in relation to the system clock.

Finally, the topic includes the discussion of similar 8-bit microprocessors in terms of the generalized model developed in the last topic and compares them with the Z80.

OBJECTIVES

· List the functional groups of the Z80 signals.

· Define the address bus. the data bus, and the control signals. and explain their functions.

· List the types of external signals and explain their purposes.

· Identify the Z80 programming registers and flags.

· List three categories of the Z80’s operations.

· Explain the terms instruction cycle, machine cycle, and T-state.

· List the steps the Z80 performs to execute the Opcode Fetch, the Memory Read, and the Memory Write cycles. and explain their functions.

· Show the bus contents and the appropriate control signals in reference to the system clock when these machine cycles are executed.

· Describe the 8085, the NSC800. and the 6800 microprocessors in terms of the generalized MPU and compare them with the Z80.

Z80 HARDWARE AND PROGRAMMING MODELS

The Z80 hardware model described in this section represents the microprocessor unit (MPU) as defined in Topic 2. The 280 microprocessor almost qualifies as an MPU. except that an external oscillator circuit is required to provide the operating frequency and appropriate control signals need to be generated to communicate with memory and I/O. In the following sections. we describe the Z80 microprocessor in relation to the model we developed in the previous topic. Then we examine the timing involved in reading an instruction from memory and generate the necessary control signals by using appropriate logic gates.

Z80 Hardware Model

The Z80 is a general-purpose 8-bit microprocessor with 16 address lines and requires a single +5 V power supply. It is housed in a 40-pin dual-in-line (DIP) package. The different versions of Z80 microprocessors such as Z80, Z80A, Z80B, and Z80H are rated to operate at various frequencies ranging from 2.5 MHz to 8 MHz. Even though the Z80 instruction set is upward compatible with the Intel 8080 set. neither of these microprocessors are pin compatible.

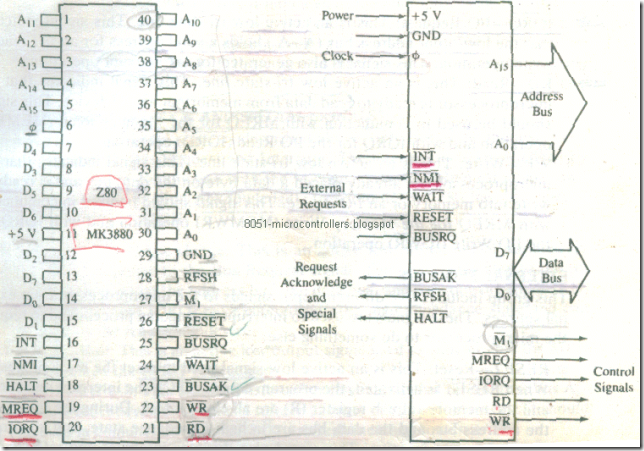

Figure 1 shows the pin configuration of the Z80 microprocessor and its hardware model with logic signals. All the signals can be classified into six groups: (1) address bus, (2) data bus. (3) control signals, (4) external requests, (5) request acknowledge and special signals, and (6) power and frequency signals. This Z80 hardware model matches the hardware model of the generalized MPU described in Topic 2. The specific details of these signals follow.

ADDRESS BUS

The Z80 has 16 tri-state signal lines. A15-A0 , known as the address bus. These lines are unidirectional and capable of addressing 64K (216) memory. The address bus is used to send (or place) the addresses of memory registers and I/O devices.

DATA BUS

The data bus consists of eight tri-state bidirectional lines D7-D0 and is used for data transfer. On these lines, data can flow in either direction-from the microprocessor to memory and I/Os or vice versa.

CONTROL SIGNALS

This group consist of five individual output lines: three can be classified as status signals indicating the nature of the operation being performed, and two as control signals indicating the nature of the operation being performed , and two as control signals to read from and write into memory or I/ os .

· M̅1__ Machine Cycle one: This is an active low signal indicating that an opcode is being fetched from memory . this signal is also used in an interrupt operation to generate an interrupt acknowledge signal , which will be explained in topic 12 .

· M͞R͞E͞Q __ Memory Request: This is an active low tri-state line. This signal indicates that the address bus holds a valid address for a memory read or write operation.

· I̅O̅R̅Q̅ __ I/O Request: This is an active low tri-state line. This signal indicates that the low-order address bus (A7 –A0) holds a valid address for an I/O read or write operation. this signal is also generated for an interrupt operation .

· R̅D̅__Read: This is an active low tri-state line. This signal indicates-that the microprocessor is ready to read data from memory or an I/O device . This signal should be used in conjunction with MREQ for the Memory Read (M̅E̅M̅R̅D̅) operation and with IORQ for the I/O Read (I̅O̅R̅D̅) operation.

· W̅R̅ __ Write : This is an active low tri-state line. This signal indicates that the microprocessor has already placed a data byte on the data bus and is ready to write into memory or an I/O device . This signal should be used in conjunction with MREQ for the Memory Write (M̅E̅M̅W̅R̅) operation and with IORQ for the I/O Write (I̅O̅W̅R̅) operation.

EXTERNAL REQUESTS

This group includes five different input Signals to the microprocessor from external sources. These signals are used to interrupt an ongoing process and to request the microprocessor to do something else.

· R̅E̅S̅E̅T̅ __ Reset: This is an active low signal used to reset the microprocessor.

When R̅E̅S̅E̅T̅ is activated. the program counter (PC), the interrupt register (I), and the memory refresh register (R) are all cleared to 0 .During the reset time. the address bus and the data bus are in high impedance state , and aII control signals become inactive . This signal also disables interrupt and refres . The R̅E̅S̅E̅T̅ signal can be initiated by an external key or switch and must be active at least for three clock periods to complete the reset operation.

·

INT __Interrupt Request

This is an active low signal. initiated by an I/O device to interrupt the microprocessor operation . when the microprocessor accepts the interrupt request, it acknowledges by activating the lORQ signal during the M1 cycle. The INT signal is maskable , meaning It can be disabled trough a software instruction. The interrupt process will be fully discussed in topic 12.

·

NMI__ Nonmaskable Interrupt

: This is a nonmaskable interrupt; it cannot be disabled. It is activated by a negative edge-triggered signal from an external source. This signal is used primarily for implementing emergency procedures.

There is no signal or pill to acknowledge this signal; it is accepted provided the Bus Request signal is inactive. (See topic 12 for details.)

· BUSRQ__Bus Request: This is an active low signal initiated by external I/O devices such as the DMA (Direct Memory Access) controller. An I/O device can send a low signal to BUSRQ to request the use of the address bus . the data bus, and the control signals . The external device can use the buses, and when its operations are complete, it returns the control to the microprocessor. This signal is used primarily for the direct memory access technique to be discussed in topic 16.

· WAIT__Wait: This is an active low signal and can be used by memory or I/O devices to add clock cycles to extend the Z80 operations . This signal is used when the response time of memory or I/O devices is slower than that of the

Z80. When this signal goes low, it indicates to the microprocessor that the addressed memory or I/O device is not yet ready for data transfer. As long as this signal is low, the Z80 keeps adding cycles to its operation. The signal will be discussed in topic 16 to illustrate how to interface slow memory chips using wait slates.

REQUEST ACKNOWLEDGE AND SPECIAL SIGNALS

Among the five external requests described above, only two of the requests need acknowledgment: Bus Request and Interrupt . The interrupt is acknowledged by the I̅O̅R̅Q̅ signal in conjunction with the M1 signal. The Bus Request is acknowledged by a B̅U̅S̅A̅K̅ (Bus Acknowledge). In addition. the Z80 has two special signals: H̅A̅L̅T̅ and R̅F̅S̅H̅.

-

B̅U̅S̅A̅K̅__Bus Acknowledge: This is an active low output signal initiated by the Z80 in response to the Bus Request signal. This signal indicates to the requesting device that the address bus, the data bus, and the control signals (R̅D̅, W̅R̅. M̅R̅E̅Q̅, and I̅O̅R̅Q̅) have entered into the high impedance state and can be used by the requesting device.

-

H̅A̅L̅T̅-Halt: This is an active low output signal used to indicate that the MPU has executed the HALT instruction.

-

R̅F̅S̅H̅-Refresh: This is an active low signal indicating that the address bus A6– A0 (low-order seven bits) holds a refresh address of dynamic memory; it should be used in conjunction with M̅R̅E̅Q̅ to refresh memory contents.

POWER AND FREQUENCY SIGNALS

This group includes three signals as follows:

-

Φ – Clock: This pin is used to connect a single phase frequency source. The Z80 does not include a clock circuit on its chip; the circuit must be built separately.

-

+ 5 V and GND – These pins are for a power supply and ground reference; the Z80 requires one + 5 V power Source.

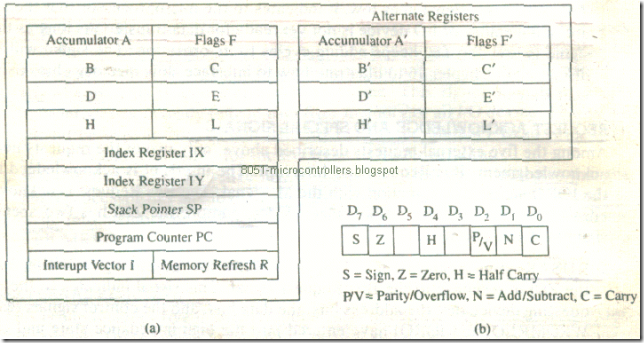

Z80 Programming Model

In the last topic, we developed a model to represent the internal structure of the MPU to process data, shown in Figure 3. Now, we will describe a similar model of the Z80 microprocessor as shown in Figure 2. The model includes an accumulator and a flag register, general-purpose register arrays, registers as memory pointers, and special-purpose registers. These registers and their functions are briefly described in the following sections; topic 6 provides greater detail.

GENERAL-PURPOSE REGISTERS

The Z80 microprocessor has six programmable general-purpose registers named B, C, D, E, H, and L, as shown in Figure 2. These are 8-bit registers used for storing data during the program execution. They can be combined as register pairs-BC, DE, HL-to perform 16-bit operations or to hold memory addresses. The programmer can use these registers to load or copy data.

ACCUMULATOR

The accumulator is an 8-bit register that is part of the arithmetic logic unit (ALU) and is also identified as register A. This register is used to store 8-bit data and to perform arithmetic and logic operations. The result of an operation performed in the ALU is stored in the accumulator.

FLAG REGISTER

The ALU includes six flip-flops that are set or reset according to data conditions after an ALU operation, and the status of these flip-flops, also known as flags, is stored in the 8-bit flag register. For example, after an addition in which the result generates a carry, the carry flip-flop will be set and bit Do in the flag register will show logic 1. The bit position of each flag is shown in Figure 2(b); bits D5 and D3 are unused.

Among the six flags. the H (Half-Carry) and N (Add or Subtract) flags are

used internally by the microprocessor for BCD (Binary Coded Decimal) operations. Each of the remaining four flags-S (Sign), Z (Zero), P/Y (Parity or Overflow). and C (Carry)-has two Jump or Call instructions associated with it: one when the flag is set and the other when the flag is reset. The details of these flags and their critical importance in programming and decision making are discussed in Topic 6.

ALTERNATE REGISTER SET

In addition to the general-purpose registers, the accumulator, and the flag register.

the Z80 includes a similar set of alternate registers designated as B’, C’, D’, E’, H’, L’, the accumulator A’, and the flag register F’. These registers are not directly available to the programmer: however. the exchange instructions can exchange information of register pairs with the respective alternate register pairs.

16-BIT REGISTERS AS MEMORY POINTERS

The Z80 microprocessor includes four 16-bit registers. and these registers are used to hold memory addresses: thus. they are classified here as memory pointers. The primary function of memory is to store instructions and data, and the microprocessor needs to access memory registers to read these instructions and data. To access a byte in a memory location, the microprocessor identifies the memory location by using the addresses in these memory pointers. The Z80 has two such specific 16-bit memory pointers, IX and IY. called index registers.

Stack Pointer (SP)

This is also a 16-bit register that is used to point to the memory location called the stack. The stack is a defined area of memory locations in R/W memory, and the beginning of the stack is defined by loading a 16-bit address in the stack pointer. We will discuss the concept of the stack memory in detail when we introduce the topic of subroutines in Topic 10.

Program Counter

(PCL This register functions as a 16-bit counter. The microprocessor uses this register to sequence the execution of instructions. The function of the pro ram counter is to point to the memory address from which the next byte is to be fetched. When the microprocessor places an address on the address bus to fetch the byte from memory. it then increments the program counter by one to point to the next memory location.

Special. Purpose Registers The Z80 microprocessor includes two special-purpose registers that are generally absent in other 8-bit microprocessors. These registers are shown in Figure 2 as the Interrupt Vector Register (I) and the Memory Refresh Register (R). The functions of these registers will be described in later topics.