MACHINE CYCLES AND BUS TIMINGS

The Z80 microprocessor is designed to execute 158 different instruction types. Each instruction has two parts: operation code (known as opcode) and operand. The opcode is a command such as Add, and the operand IS an object to be operated on, such as a byte or the contents of a register. Some instructions are 1-byte instructions. and some are multibyte instructions. To execute an instruction, the Z80 needs to perform various operations such as Memory Read/Write and I/O Read/Write. However, there is no direct relationship between the number of bytes of an instruction and the number of operations the Z80 has to perform. For example, the instruction to send the contents of the accumulator to the output port 10H,is a 2-byte instruction: OUT (10H), A.

-

Byte 1: OUT → This is the opcode to output data.

-

Byte 2: (10H*) , A → This is the operand to specify that the byte should be sent from the accumulator to port 10H .

(A hexadecimal number in an instruction is shown as a number followed by the letter H. )

But the Z80 has to perform three operations:

(1) read Byte 1 from memory,

(2) . read Byte 2 from memory,

(3) send data to port 10H .

In the previous section. numerous Z80 signals and their functions were described. Now we need to examine these signals in conjunction with execution of , individual instructions and their operations. This task may appear overwhelming

at the beginning; fortunately. all instructions are divided into a few basic operations called machine cycles. and these machine cycles are divided into precise system dock periods.

The microprocessor external communication functions can be divided into three basic categories:

1. Memory Read and Write.

2. I/O Read and Write.

3. Request Acknowledge .

These functions are further divided into various operations (machine cycles) as shown in Table 3.1. Each instruction consists of one or more of these machine cycles. and each, machine cycle is divided into T-states .

To understand various operations. we need to define three terms: instruction cycle. machine cycle. and T-state.

Instruction cycle is defined as the time required to complete the execution of an instruction The Z80 instruction cycle consists of one to six machine cycles or one to six operations.

Machine cycle is defined as the time required to complete one operation of accessing memory. accessing I/O. or. acknowledging an external request. This cycle may consist of three to six T-states.

T-state is defined as one subdivision of the operation performed in one clock period. These subdivisions are internal states synchronized with the system clock. and each T-state is precisely equal to one clock period. The terms T-state and clock period are often used synonymously.

In this topic. we focus on the first three operations listed in Table 3.1- Opcode Fetch, Memory Read, and; Memory Write-and examine the signals on various buses in relation to the system clock. In the next topic. we will use these timing diagrams to interface memory with the Z80 microprocessor. Similarly, we will discuss timings of other machine cycles in later topics in the context of their applications. For example, I/O Read/Write machine cycles will be discussed in Topic 5 and Interrupt Acknowledge will be discussed in Topic 12.

TABLE 3.1

The Z80 Machine Cycles and Control Signals

|

Machine Cycle |

M͞1 |

M͞R͞E͞Q |

IO͞R͞Q |

R͞D |

W͞R |

|

Opcode Fetch (M͞1 ) |

0 |

0 |

1 |

0 |

1 |

|

Memory Read |

1 |

0 |

1 |

0 |

1 |

|

Memory Write |

1 |

0 |

1 |

1 |

0 |

|

I/O Read |

1 |

1 |

0 |

0 |

1 |

|

I/O Write |

1 |

1 |

0 |

1 |

0 |

|

Interrupt Acknowledge |

0 |

1 |

0 |

1 |

1 |

|

Non-maskable Interrupt |

0 |

0 |

1 |

0 |

1 |

|

Bus Acknowledge (B͞U͞S͞A͞K = 0) |

1 |

Z |

Z |

Z |

Z |

NOTE: Logic 0 = Active. Logic 1 = Inactive. Z = High Impedance

Opcode Fetch Machine Cycle M͞ 1 )

The first operation in any instruction is opcode fetch. The microprocessor needs to get (fetch) this machine code from the memory register where it is stored before the microprocessor can begin to execute the instruction. The opcode fetch operation and its timing signals are illustrated in Example 1.

Example 1

The accumulator of the Z80 microprocessor holds the data byte 9FH . and the code for instruction LD B, A (opcode) 0 1 0 0 0 1 1 1 (47 H) is stored in memory location 2002H This is a I-byte instruction. and when this opcode is executed. the contents of the accumulator will be copied into register B. List the sequence of events that takes place to execute this machine code and illustrate the signals on various buses in relation to the system clock .

Solution

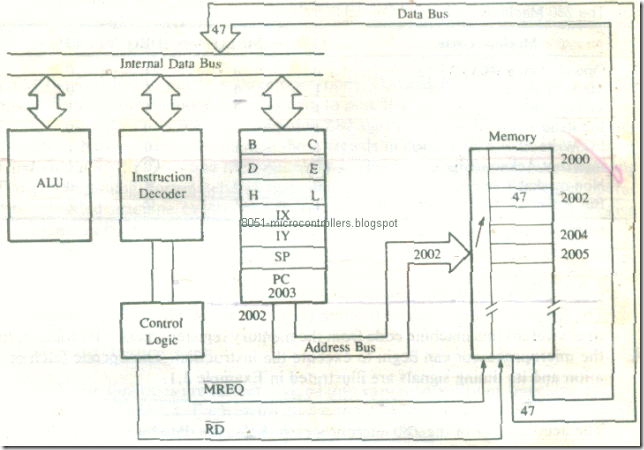

We assume here that the Z80 has already completed the execution of the code in memory location 2001H and the program counter holds the address 2002H Before the Z80 can execute the opcode, it needs to fetch the code from the memory location, To fetch the opcode, the Z80 performs the following steps:

1. The Z80 places the contents of the program counter (2002H) on the address

bus, and increments the program counter to the next address. 2003H:The program counter always points to the next byte to be executed.

2.The address is decoded by the external decoding circuit, and the register 2002H is identified.

3.The Z80 sends the control signals (M͞R͞E͞Q and R͞D) to enable the memory output buffer.

4.The contents of the memory register (opcode 47H) are placed on the data bus and brought into the instruction decoder of the microprocessor .

5. The Z80 decodes the Z80 ode and executes the instruction, meaning it copies the contents of the accumulator into register B.

FIGURE 3

Z80 Memory Read Operation

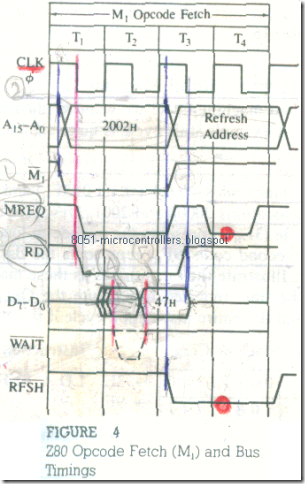

Figure 3 shows how the Z80 fetches the opcode using the address and the data buses and the control signal. Figure 4 shows the timing of the Opcode Fetch machine cycle in relation to the system’s clock. The address bus in Figure 4 is shown as two parallel lines. This is a commonly used practice to represent logic levels of groups of lines; some lines are high and others are low, and the crossover of the lines indicates that a new address is being placed on the address bus . the high impedance state is shown by a straight line as in the data bus ( D7 – D0 ) .The of these signals are given below.

1. Figure 4 shows that the Opcode Fetch cycle is completed in four clock periods or T-states. This machine cycle is also identified, as the M1 cycle.

2. At the beginning of the first clock period T1 , the control signal M͞1 goes low

and the contents of the program counter (2002H) are placed on the address bus .

3. After the falling edge of T1 , the Z80 asserts two control signals-M͞R͞E͞Q and R͞D, both active low The M͞R͞E͞Q indicates that it is a memory-related operation, and R͞D suggests that it is a Read operation. Both signals are necessary to read from memory.

4. The internal decoder of the memory and the Chip Select circuit (not shown in Figure 4) decode the address and identify register 2002H The control signals

FIGURE 4

Z80 Opcode fetch (M1) and Bus Timings

SOURCE: Courtesy or Zilog Inc.

(adapted).

M͞R͞E͞Q and R͞D are used to enable the memory output buffer. The data bus. which was in high impedance state. is activated as an input bus (to the micro- processor) shortly after the .leading edge of T2. After the falling edge of T2. memory places its register contents (47H) on the data bus.

5. At the leading edge of T3, the data on the data bus are read, and the control signals become inactive .

6. During T3 and T4 , when the instruction decoder in the microprocessor decodes and executes the opcode. These are internal operations and cannot be observed on the data bus.

The following two steps are irrelevant to the present problem; however. they are included here as part of the M1 cycle.

7. During T3 and T4 when the Z80 is performing internal operations. the low order address bus is used to supply a 7-bit address for refreshing dynamic memory . If the system includes dynamic memory, this operation simplifies its interfacing hardware. This aspect of the M1 cycle will be discussed again when

we illustrate interfacing of dynamic memory (Topic 16).

8. Figure 4 shows the signal called W͞A͞IT. The Z80 samples the Wait line during T2 and if it is forced low by an external device (such as memory or I/O). the Z80 adds Wait states (clock cycles) to extend the machine cycle and continues to add clock cycles until the Wait signal goes high again. This technique is used

to interface memories with slow response time and will be discussed again in Topic 16.

Memory Read Machine Cycle

The second machine cycle we want to illustrate is Memory Read. As explained in the next example, this cycle is quite similar to the Opcode retch cycle.

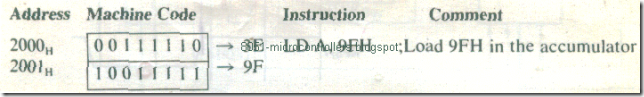

Example 2

Two machine codes-0 0 1 1 1 1 1 0 (3EH) and 1 0 0 1 1 1 1 1 (9FH)-are stored in memory locations 2000H and 2001 H , respectively, as shown below. The first machine code (3EH) represents the opcode to load a data byte into the accumulator, and the second code (9FH) represents the data byte to be loaded into the accumulator, Illustrate the bus timings as these machine codes are executed, and calculate the time required to execute the Opcode Fetch and the Memory Read cycles and the entire instruction cycle if the clock frequency is 4 MHz.

Address Machine Code Instruction Comment

Solution

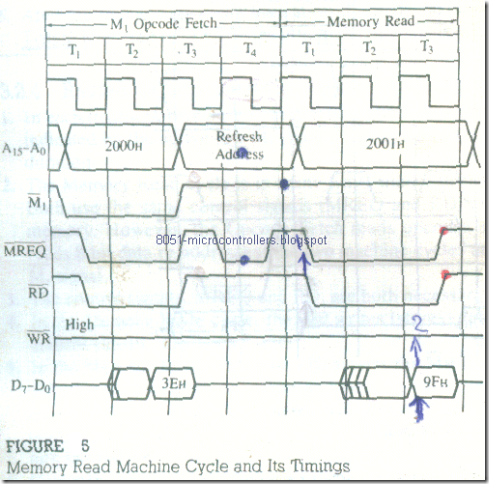

This instruction consists of two bytes ; the first is the opcode. and the second is the data byte. The Z80 must first read these bytes from memory and thus requires at least two machine cycles. The first machine cycle is Opcode Fetch. and the second machine cycle is Memory Read, as shown in Figure 5. These cycles are described in the following list.

1.The first machine cycle (Opcode Fetch) is identical in bus timings with the machine cycle illustrated in Example 1. except for the bus contents. The address bus contains 2000H , and the data bus contains the opcode 3EH . when the Z80 decodes the opcode during the T3 state, it realizes that a second byte

must be read.

2. After the completion of the Opcode Fetch cycle, the Z80 places the address

2001H on the address bus and increments the program counter to the next address. 2002H ,To differentiate the second cycle from the opcode Fetch cycle. the M1 signal remains inactive (high).

3. After the falling edge of T1 of the Memory Read cycle, the control signals M͞R͞E͞D and R͞D are asserted. These signals, along with the memory address, are used to identify the register 2001H and enable the memory chip .

4. After the leading edge of T3 , the Z80 activates the data bus as an input bus ; memory places the data byte 9FH on the data bus, and the Z80 reads and stores . the byte in the accumulator during T3 .

5. After the falling edge of T3 , both control signals become inactive (high). and at

the end of T3 , the next machine cycle begins.

FIGURE 3.5

Memory Read Machine Cycle and Its Timings

The execution times of the Memory Read machine cycle and the instruction cycle are calculated as follows:

Clock Frequency f = 4 MHz

T-state = Clock Period (1/f) = 0.25 µs

Execution Time for Opcode Fetch: (4 T) x 0.25 = 1.0 µs

Execution Time for Memory Read: (3 T) x 0.25 = 0.75 µs

Execution Time for Instruction: (7 T) x 0.25 == 1.75 µs

Memory Write Cycle

Now we want to illustrate the third machine cycle: Memory Write. This machine cycle writes or stores data in a specified memory register as shown in the following example.

Example 3

The HL register holds the address 2350H , and the accumulator has the data byte 9FH , The instruction code 0 1 1 1 0 1 1 1 (77H) is stored in memory location 2003H , When this code is executed, it stores the contents of the accumulator in the memory location indicated by the address in the HL register. Illustrate the bus contents and timings as this instruction is being executed.

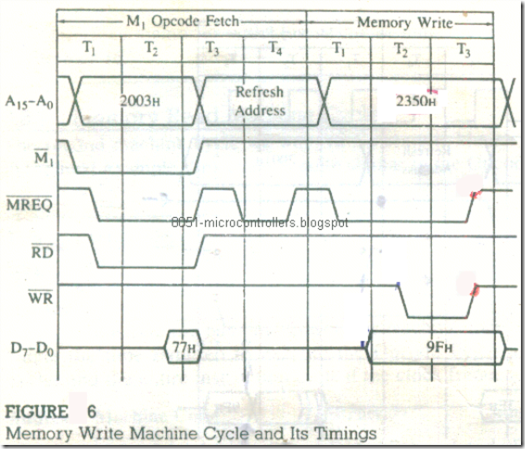

FIGURE 6

Memory Write Machine Cycle and Its Timings

Instruction: LD (HL), A ;Copy contents of the accumulator into memory location, the address of which is stored in HL register.

Solution

This is a one-byte instruction with two machine cycles: Opcode Fetch and Memory Write . In the first machine cycle, the Z80 fetches the code(77H), and in the second machine cycle, it copies the byte 9FH from the accumulator into the memory location 2350H , The timings of these machine cycles are shown in Figure 6 and explained be row.

1. In the Opcode Fetch machine cycles , the Z80 places the address 2003H on the address bus and gets the code 77H by using the control signals M͞R͞E͞Q and R͞D as in the previous examples. The program counter is also incremented to the next address, 2004H

2. During the T3 and T4 states, the Z80 decodes the machine code 77H and prepares for the memory write operation .

3. At the beginning of the next machine cycle (Memory Write). it places the contents (2350H) of the HL register on the address bus. At the falling edge of T3 M͞R͞E͞Q goes low and the data byte 9FuJrom the accumulator is placed on the data bus.

4. After allowing one T-state (after M͞R͞E͞Q) to stabilize the address. the Z80 asserts the control signal Write (W͞R), which is used to write the data byte at the address shown on the address bus.

5. After the falling edge of T3 , both control signals become inactive, and one-half T-state later, the data bus goes into high impedance state .

Review of Important Concepts

1. In each instruction cycle, the first operation is always Opcode Fetch, and it is indicated by the active low M͞1 signal, This cycle can be four to six T-states in duration.

2. The Memory Read cycle is in many ways similar to the Opcode Fetch cycle, Both use the same control signals (M͞R͞E͞Q and R͞D) and read contents from memory. However, the Opcode Fetch reads opcodes and the Memory Read reads 8-bit data or addresses; the two machine cycles are differentiated by the M͞1 signal.

3. The control signals, MREQ and RD, are both necessary to read from memory .

4. In the Memory Write cycle, the Z80 writes (stores) data in memory using the

control signals M͞R͞E͞Q and W͞R .

5. In the Memory Read cycle, the Z80 asserts the M͞R͞E͞Q and R͞D signals to enable memory, and then the addressed memory places the data on the data bus; on the other hand, in the Memory Write cycle, the Z80 asserts the M͞R͞E͞Q. places the data byte on the data bus. and then asserts the W͞R signal to write into the addressed memory.

6. Generally, the Memory Read and Write cycles consist of three T-states; however, they can take four T-states in some instructions. The Memory Read and Write cycles will not be asserted simultaneously; the microprocessor cannot read and write at the same time.