The primary reasons to discuss other 8-bit microprocessors are to examine how the MPU model developed in the last topic matches with various microprocessors and to confirm that the underlying basic concepts remain similar even though specific details may vary from one chip to another. At present. many 8-bit general-purpose microprocessors are available in the market. We will focus on three: the Intel 8085. the National Semiconductor NSC 800, and the Motorola 6800. These microprocessors are selected to illustrate various strategies used in designing the microprocessor. The recent trend in 8-bit microprocessors can be illustrated by so-called 8-bit super chips, such as the Hitachi HD64180, discussed in Topic 18.

Inte18085

The intel 8085 and its predecessor the 8080 are widely used 8-bit microprocessors. The 8080 MPU is composed of three chips-the 8080 microprocessor, the clock generator, and the system driver-and it needs three power supplies ( + 5 V, – 5 V. + 12 V). The 8085 is an upgraded version of the 8080: it operates with one + 5 V power supply, and one chip replaces the 8080’s three chips. The 8085 is upward software compatible with the 8080; it has only two more instructions than the 8080. The programming models of both microprocessors are identical; however. the 8085 hardware model differs significantly not only from the 8080 but also from other 8-bit microprocessors. The 8085 has a multiplexed bus (8 lines). which is used as both the 8-bit data bus and the low-order address bus. This feature allows Intel to provide additional interrupt lines.

HARDWARE MODEL

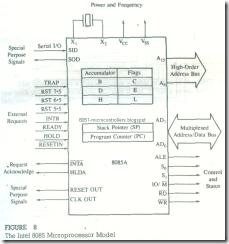

Figure 8 represents the hardware model with the logic pinout of the 8085. The six categories of the signals are address bus, data bus. control (and status) signals. external requests, request acknowledge, and power and frequency signals. In addition, the 8085 has two signals for serial I/O.

FIGURE 8

The Intel 8085 Microprocessor Model

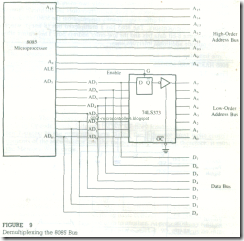

FIGURE 9

Demultiplexing the 8085 Bus

The 8085 has a 16-bit address bus: however. its low-order address bus is multiplexed with the data bus. These eight lines are time-shared by two functions; in the earlier part of a machine cycle. they are used for a low-order address, and in the later part for data. To interface this chip with memory (without any special features), these lines need to be demultiplexed (separated). The 8085 has a signal called ALE (Address Latch Enable), which can be used to demultiplex the bus. as shown in Figure 9. The ALE is asserted at the beginning of each machine cycle. when the bus has an address. Figure 9 shows that the ALE is used to latch the address. thus creating a separate low-order bus A7-A0. The Z80 does not need this signal because it has separate lines for the data and the address buses.

The 8085 has two status signals S0 and S1 to identify various machine cycles, and an IO/M͞ signal to differentiate between an I/O operation and a memory operation. In contrast. the Z80 identifies the Opcode Fetch cycle by asserting M͞1 , and has two separate signals (M͞R͞E͞Q and I͞O͞R͞Q) to identify memory and I/O operations. In the 8085, the control signals Memory Read/Write and I/O Read/Write are generated by ANDing IO/M͞ and control signals R͞D and W͞R.

Figure 8 shows that the 8085 provides five interrupt lines as external requests. out of which the TRAP is equivalent to the Z80 nonmaskable interrupt. The Z80 provides various additional interrupt modes through software.

8085 SOFTWARE MODEL

Figure 8 also shows the software model of the 8085. It includes one accumulator. a flag register, a general-purpose register array, and two 16-bit registers as memory pointers (program counter and stack pointer). This model matches very well with the requirements of the microprocessor as a processing unit (Figure 2). The Z80 includes all the 8085 registers in addition to an alternate set of registers, index registers, and special-purpose registers.

National Semiconductor NSC80

The NSC800 is an 8-bit microprocessor manufactured by National Semiconductor. It is a low-power CMOS device that combines features of the 8085 and the Z80. Because its power consumption is 5 percent of that of n-channel MOSFET (NMOS) devices. it is ideally suited for low-power or battery-operated applications.

The NSC800 has a bus structure similar to that of the 8085: a multiplexed bus with the status signals S0, S1. and IO/M͞ . It has a powerful interrupt scheme that combines the 8085 signals and the Z80 interrupt modes. Its software model. instruction set, and mnemonics are identical with those of the Z80.

In summary. the NSC800 combines the software capability of the Z80 with the bus structure of the 8085; its hardware and software models match with the generalized model we developed in the previous topic.

Motorola MC6800

The MC6800 was developed at about the same time as the Intel 8080. The hardware model of this processor is similar to any other processor we have discussed, but it has a different internal architecture.

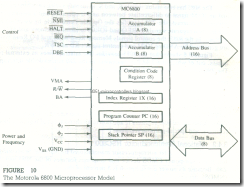

Figure 10 represents the 6800’s architecture. It has 16 address lines, 8 data lines, and fewer control (and status) signals than the Z80. The fewer control signals result from the lack of peripheral-mapped I/O; all I/Os are interfaced as memory-mapped I/Os. Therefore. the control signals in this processor need not differentiate between memory and I/O operations.

The other significant difference is in its internal architecture; it has two accumulators, one flag register shown as the Condition Code Register, but no general-purpose registers. This processor uses external memory for storing interim

FIGURE 10

The Motorola 6800 Microprocessor Model

calculations and data bytes; it makes extensive use of memory referencing in its operations. The 6800 has simple timing and control signals; the clock period is the same as the machine cycle.

The 6809 is the latest improved version of the 6800 family; however. its machine code is not compatible with that of the 6800. Its internal architecture is similar to that of the 6800, except it has an additional stack pointer, an additional index register. and a register to be used for referencing memory. The basic design philosophy is the same as that of the 6800, but it has eliminated some limitations of the 6800.

Review of 8-bit Microprocessors

In the last section, we examined the architectures of three microprocessors and occasionally compared them with the Z80. Now we can easily conclude that the architectures of various 8-bit microprocessors have similar patterns and can be represented by the hardware and the software models developed in the last chapter. We can classify these processors into two categories: one group, including the Z80, the 8085, NSC800, is register-oriented; the group including the 6800 and the 6809 is memory-reference-oriented.