Memory Organisation

1. Mention the address capability of 8086 and also show its memory map.

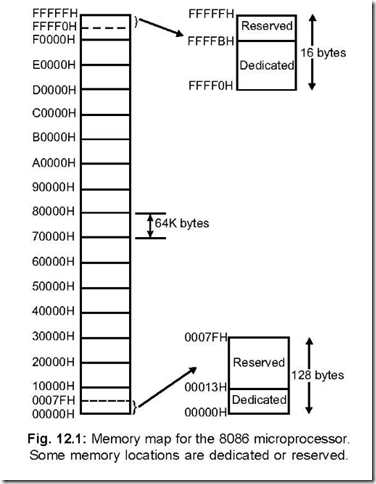

Ans. 8086, via its 20-bit address bus, can address 220 = 1,048,576 or 1 MB of different memory locations. Thus the memory space of 8086 can be thought of as consisting of 1,048,576 bytes or 524,288 words.

The memory map of 8086 is shown in Fig. 12.1, where the whole memory space starting from 00000 H to FFFFF H is divided into 16 blocks—each one consisting of 64 KB. This division is arbitrary but at the same time a convenient one—because the most significant hex digit increases by 1 with each additional block. Thus, 30000 H memory location is 65,536 bytes higher in memory than the memory location 20000 H.

The lower and upper ends of the memory map are shown separately—earmarking some spaces as reserved and some as ‘dedicated’.

The reserved locations are meant for future hardware and software needs while the dedicated locations are used for processing of specific system interrupts and reset functions.

2. Mention the different types of memory segmentations of 8086.

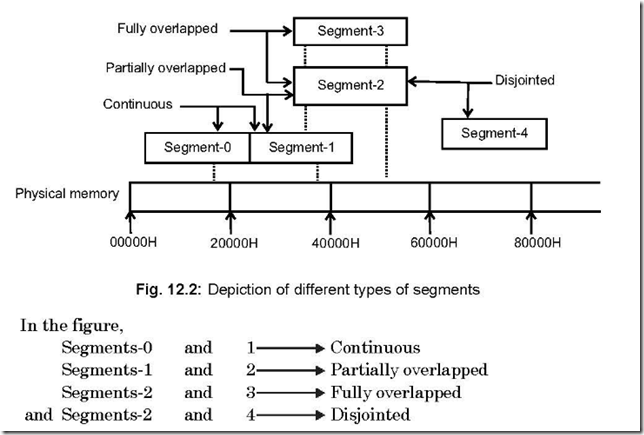

Ans. The different memory segmentations done in case of 8086 are

z Continuous

z partially overlapped

z fully overlapped and

z disjointed

This is shown in Fig.12.2.

3. Describe memory segmentation scheme of 8086. What is meant by currently active segments?

Ans. 1 MB memory of 8086 is partitioned into 16 segments—each segment is of 64 KB length.

Out of these 16 segments, only 4 segments can be active at any given instant of time— these are code segment, stack segment, data segment and extra segment. The four memory segments that the CPU works with at any time are called currently active segments. Corresponding to these four segments, the registers used are Code Segment Register (CS), Data Segment Register (DS), Stack Segment Register (SS) and Extra Segment Register (ES) respectively.

Each of these four registers is 16-bits wide and user accessible—i.e., their contents can be changed by software.

The code segment contains the instruction codes of a program, while data, variables and constants are held in data segment. The stack segment is used to store interrupt and subroutine return addresses.

The extra segment contains the destination of data for certain string instructions. Thus 64 KB are available for program storage (in CS) as well as for stack (in SS) while 128 KB of space can be utilised for data storage (in DS and ES).

One restriction on the base address (starting address) of a segment is that it must reside on a 16-byte address memory—examples being 00000 H, 00010 H or 00020 H, etc.

4. Mention the maximum size of memory that can be active for 8086. Ans. The maximum size of active memory for 8086 is 256 KB. The break-up being

64 KB for program

64 KB for stack and

128 MB for data.

5. Why memory segmentation is done for 8086?

Ans. Memory segmentation, as implemented for 8086, gives rise to the following advantages:

z Although the address bus is 20-bits in width, memory segmentation allows one to work with registers having width 16-bits only.

z It allows instruction code, data, stack and portion of program to be more than 64 KB

long by using more than one code, data, extra segment and stack segment.

z In a time-shared multitasking environment when the program moves over from one user’s program to another, the CPU will simply have to reload the four segment registers with the segment starting addresses assigned to the current user’s program.

z User’s program (code) and data can be stored separately.

z Because the logical address range is from 0000 H to FFFF H, the same can be loaded at any place in the memory.

6. Discuss logical address, base segment address and physical address.

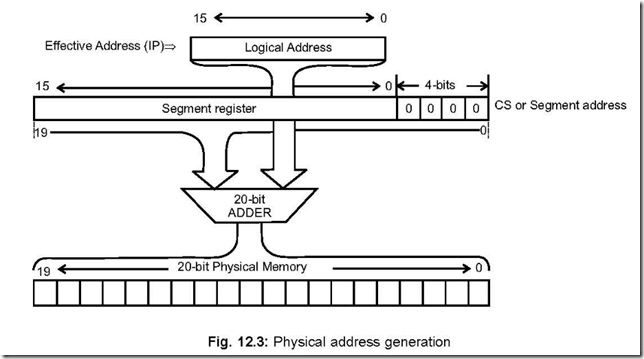

Ans. The logical address, also goes by the name of effective address or offset address (also known as offset), is contained in the 16-bit IP, BP, SP, BX, SI or DI.

The 16-bit content of one of the four segment registers (CS, DS, ES, SS) is known as the base segment address.

Offset and base segment addresses are combined to form a 20-bit physical address (also called real address) that is used to access the memory. This 20-bit physical address is put on the address bus (AD19 – AD0) by the BIU.

7. Describe how the 20-bit physical address is generated.

Ans. The 20-bit physical (real) address is generated by combining the offset (residing in IP, BP, SP, BX, SI or DI) and the content of one of the segment registers CS, DS, ES or SS. The process of combination is as follows:

The content of the segment register is internally appended with 0 H (0000 H) on its right most end to form a 20-bit memory address—this 20-bit address points to the start of the segment. The offset is then added to the above to get the physical address.

Fig. 12.3 shows pictorially the actual process of generating a 20-bit physical address.

Thus, Physical Address = Segment Register content 16 D + Offset.

8. Although 8086 is a 16-bit µP, it deals with 8-bit memory. Why?

Ans. This is so for the following two reasons:

z It enables the microprocessor to work with both on bytes and words. This is very important because many I/O devices such as printers, terminals, modems etc, transfer ASCII coded data (7 or 8 bits).

z Quite a few of the operation codes of 8086 are single bytes while so many other instructions are there which vary from 2 to 7 bytes. By working with byte-width memory, these varied opcodes can easily be handled.

9. Is the flat scheme of memory applied for 8086 µP?

Ans. No, the flat (or unsegmented) scheme of memory is not applied for 8086 µP, because the

memory of the same is a segmented one. In flat scheme, the entire memory space is

thought of as a single addressable memory unit.

The flat scheme can be applied for 8086 by initialising all the segment registers with identical (or same) base address. Then all memory operations will refer to the same memory space.

10. Describe how memory is organised for 8086 µP?

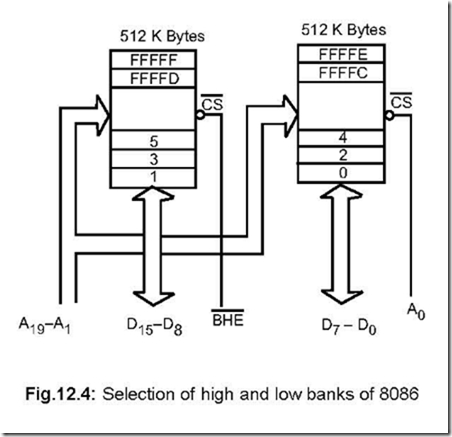

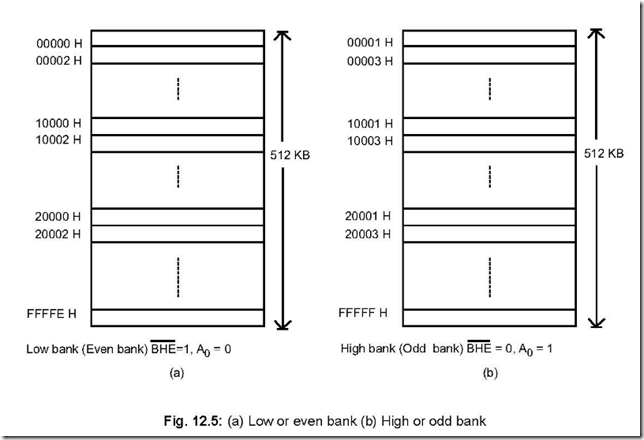

Ans. The total address space 1 MB of 8086 is divided into 2 banks of memory—each bank of maximum size 512 KB. One is called the high order memory bank (or high bank) and the other low order memory bank (or low bank).

Low bank, high bank or both banks can be accessed by utilizing two signals BHE

and A0. Table 12.1 shows the three possible references to memory.

Table 12.1: Memory references

|

BHE |

A0 |

Processing |

|

0 |

0 |

Both Banks Active 16-bit world transfer on AD15 ⇔ AD0 |

|

0 |

1 |

Only High bank Active (One byte from/to odd address on AD ⇔ AD ) 15 8 |

|

1 |

0 |

Only Low bank Active (One byte from/to even address on AD ⇔ AD ) 7 0 |

|

1 |

1 |

No Bank Active |

The high bank is selected for A0=1 and BHE =0 and is connected to D15–D8 while the low bank is selected for A0=0 and BHE =1. Neither low bank nor high bank would selected

for A0=1 and BHE =1.

Fig. 12.4 shows how the total address space (1MB) of 8086 is physically implemented

by segregating it into low and high banks. It also shows that CS signal of the high bank is connected to BHE while the CS signal of the low bank is connected to A0.

11. Show the profiles of low and high order memory banks.

Ans. The low and high order memory banks correspond to even and odd banks respectively.

The CS signal of low order memory bank is selected when CS = 0. Since A0 (lowest address bus line) is connected to CS , hence A0 must have be to low for the low order bank

to be selected. That is why the low order bank corresponds to even bank. Similarly the

high order bank is selected when A0 = 1. Hence, the higher order bank is called odd bank.

The profile of the low and high order banks are shown below in Fig. 12.5

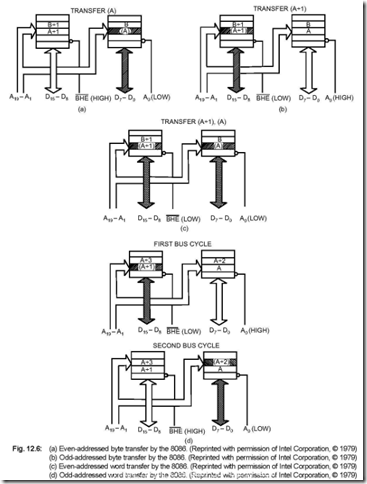

12. Draw the diagrams of (a) even-addressed byte transfer (b) odd-addressed byte transfer (c) even-addressed word transfer and (d) odd-addressed word transfer.

Ans. Fig. 12.6 shows the above four cases. A, B are representing the addresses while (A), (B) represent the content of address locations A and B respectively.

Figures (a) and (b) correspond to byte transfers for even and odd-addressed memory locations respectively. The shaded memory location indicates that the content of that particular memory location comes out either via higher byte data bus (D15–D8) or lower byte data bus (D7–D0) respectively.

Figures (a), (b) and (c) complete the data transfer in one bus cycle only.

For Figure (a), BHE = 1, A0 = 0

For Figure (b), BHE = 0, A0 = 1

For Figure (c), BHE = 0, A0 = 0

Figure (d) corresponds to an odd-addressed word transfer and it takes two bus cycles

to complete this transfer.

This odd-addressed word is an unaligned one and the LSB of the address is in the high memory bank.

The odd byte of the word is at address location A + 1 and is selected by making

![]() BHE = 0 and A0. Thus in the first bus cycle, data to transferred on D15 – D8.

BHE = 0 and A0. Thus in the first bus cycle, data to transferred on D15 – D8.

In the second bus cycle, 8086 automatically increments the address. Hence A0

becomes 0, representing even address A + 2. This is in the low bank and is accessed by

13. Which pins identify the segment registers used for 20-bit physical address generation?

Ans. Pins A16 and A17 become S3 and S4 from the second bus cycle. This 2-bit combination of S3 and S4 indicate the segment register used for physical address generation and is shown in Table 12.2

Table 12.2: Identifying the segment register used for 20-bit physical address generation

|

S4 |

S3 |

Segment Register |

|

0 |

0 |

Extra |

|

0 |

1 |

Stack |

|

1 |

0 |

Code/none |

|

1 |

1 |

Data |

The two status codes are output both in the maximum and minimum mode.

14. What is the maximum size of the memory that can be accessed by 8086?

Ans. The two status codes S4 and S3 together point to the segment register used for 20-bit physical address generation and can be examined by external circuitry to enable separate 1 MB address space for each of CS, ES, DS, and SS. This would enable memory address

to be expanded to a maximum of 4MB for 8086 µP.

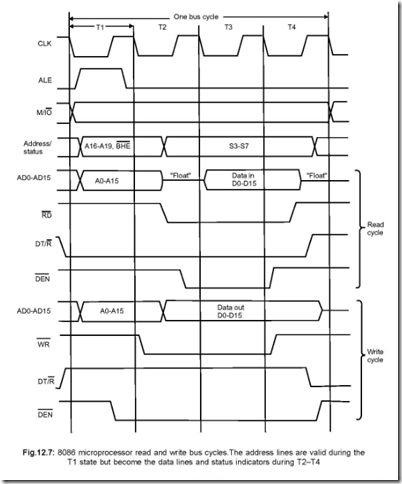

15. Draw the Read and Write bus cycles for 8086 µP in Minimum mode.

Ans. Fig. 12.7 shows the Read and Write bus cycles for 8086 µP in the Minimum mode.

The bus cycle consists of 4T states. ALE signal stays high for T1 state at the end of which it goes low which is utilised by latches to latch the address. Hence, during

T2 – T4 states, AD15 – AD0 lines act as data lines. The M/ IO , RD and WR signals can be combined to generate individual IOR, IOW and MEMR, MEMW signals.

The Read and Write cycles show that data are made available during T3 and T2 states respectively.