8254: Programmable Interval Timer

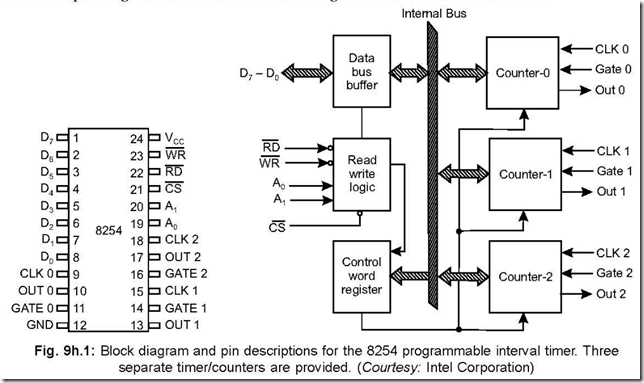

1. Draw the pin diagram and functional block diagram of 8254.

Ans. The pin diagram and functional block diagram of 8254 are shown below:

2. How many counters are there in 8254?

Ans. There are three 16-bit counter registers, each of which can be programmed as a timer or an event counter. The counters are named as COUNTER 0, COUNTER 1 and COUNTER 2.

3. How programming is done in 8254?

Ans. The programming is done by writing a control word in the Control Word Register.

4. In how many modes can 8254 operate?

Ans. 8254 can operate in six possible operating Modes—Mode 0 to Mode 5.

5. What kind of outputs are available from the different operating modes.

Ans. From the six different operating modes, the outputs which are available are: event counter, one-shot, square-wave generator, divide-by-N counter, hardware triggered strobe and software triggered strobe.

6. What happens when the Terminal Count (TC) of a counter is reached?

Ans. The counters operate in count down mode. When a counter counts down to zero, it is called ‘Terminal Count’. When TC for a particular counter occurs, the following may occur:

z an interrupt can be requested

z a one-shot pulse can be terminated

z a strobe pulse can be generated

z the logic level of a square wave can be toggled.

7. What are the differences between timers 8253 and 8254?

Ans. Timer 8254 is actually a “Superset” of timer 8253 and is pin compatible with the latter.

There are two differences between the two, which are

z 8254 has read back mode facility—which means that the status of a particular mode can be read after programming. This facility is not available with 8253.

z The maximum clock frequency of 8254 is 10 MHz, whereas that of 8253 is 2 MHz.

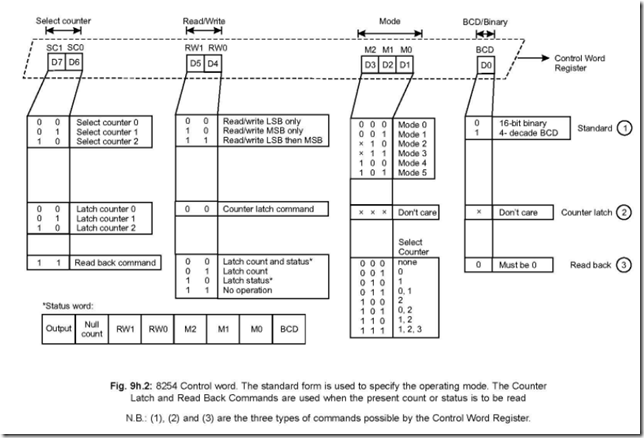

8. In how many forms can the control word register be used?

Ans. The control word can be used in three formats—Standard mode, counter latch mode and Read back mode.

9. How one of the Six Modes (Mode 0 to Mode 5) is selected?

Ans. The particular mode is selected by the standard form of the control word in the control word register.

10. Draw the control word register format and discuss.

Ans. The control word of the control word register is shown Fig. 9h.2.

The control word byte is divided into four parts D7 – D6, D5 – D4, D3 – D2 – D1 and D0. The different combinations of these eight bits give rise to ‘standard’ mode, ‘Counter latch’ mode or ‘Read back’ mode and are self evident from the figure.

11. Discuss the six different modes in which 8254 can operate.

Ans. The six different modes are Mode 0 to Mode 5. These are discussed below:

Mode 0: This is an ‘event counter’, when GATE = 1, the counter will start decrementing from its stored value on the falling edge of the second pulse of CLK input. OUT will go high when ‘terminal count’ is reached. This OUT signal can be utilised as an interrupt input to the microprocessor.

Mode 1: It is ‘hardware triggered one shot’, when the rising edge of the GATE pulse is received, OUT goes low and remains low till TC (terminal count) is reached. Then OUT goes high. This low one shot duration is equal to the stored value in the counter multiplied by the CLK period.

Mode 2: It is a ‘Divide-by-N’ counter, when GATE = 1, OUT goes low for one period of the CLK input after the stored count is decremented to 1. The initial (or stored) count will then automatically get reloaded and the cycle repeats.

Mode 3: It is a ‘square wave generator’. It is identical to Mode 2, but the duty cycle (= on time/period) here is 50%. In case, the initial count is an odd number, OUT then will be high for one more clock cycle then it is low.

Mode 4: It is a ‘software triggered mode’. If GATE = 1, OUT goes low for one period of the CLK input N clock cycles after, where N is the initial (or stored) number in the counter. For second strobing to be done, N must be reloaded in the counter.

Mode 5: It is a ‘Hardware triggered mode’. On the appearance of rising edge of the GATE input, the stored or initial count starts decrementing to 0. When TC occurs, OUT goes low for one period of the CLK input.

12.

|

How the three counters and the control word are selected? Ans. The combination of A1 A0 select the above and shown below:

13. Write down the port addresses of the three counters and the control word

ææ

register. The CS signal is derived on the basis of A7 – A4 = 1111 and A3 – A2 =

00.

Ans. The port addresses of the counters and the control word register are determined as follows:

|

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

Port address of |

|||

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

= |

F0 |

—> |

Counter 0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

= |

F1 |

—> |

Counter 1 |

|

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

= |

F2 |

—> |

Counter 2 |

|

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

= |

F3 |

—> |

Control Word Register. |

14. Write down the Control Word so that Counter 1 operates in Mode 0 in binary

sequence.

Ans. By having a look at the control word register, the control word will be as follows: 0 1 1 1 0 0 0 0 = 0111 0000 = 70

While writing the above control word, it is assumed that Counter 1 is to be loaded with a 2-byte count.