Each company has its own approach to the problem of circuit design and application for practical transistorized static control. This chapter will take up the details of the General Electric Company system. The material for this chapter was furnished by the General Electric Company.1 Other systems will be cov ered in Chaps. 12 and 13.

11·1 THEORY OF OPERATION

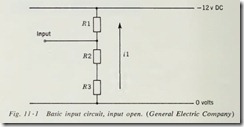

Basic transistor circuits are used throughout the system. Figure 11·1 shows a circuit with –12 volts d-e connected to the system bus, and with three resistors connected between the bus. Current il will flow through the resistors as shown, since a potential difference exists across each resistor. Because of the particular resistors used in this circuit, the input connection point will be at -4 volts.

1 SOURCE: General Electric Company publication GET 3551.

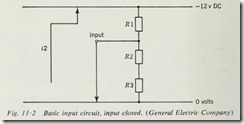

If the input terminal is now connected to the zero-volt bus (see Fig. 11·2 ), current will flow from the zero-volt bus through resistor R 1 to the -12-volt bus. Since the connection between resistors R 1 and R2 is at zero volts, no current will pass through resistors R2 and R3 because no potential difference exists across them .

If a transistor and appropriate load resistors R4, R5, and R6 (with the same values as R1, R2, and R3, respectively) are connected between the two buses (see Fig. 11 ·3), the output connection will be at -4 volts unless there is conduction through the transistor.

The silicon-type PNP transistor shown in Fig. 11 ·3 h asthree connection points called the emitter, the base, and the collector. If there is adequate current flowing from emitter to base, a much larger current will flow from emitter to collector. With no current flowing from the emitter to the base, no current will flow from the emitter to the collector. The transistor is saturated when additional emitter-to-base current flow causes no increase in emitter-to-collector current flow. As the transistor is driven to saturation, its emitter-to-collector resistance changes from a very high value to a very low value, essentially acting as a switch in the circuit.

The circuit shown in Fig. 11·4 is obtained by combining Figs.11·1 and 11·3. With the input connection at –4 volts, current will flow from emitter to base of the PNP transistor, resulting in current flow from the emitter to the collector through load resistor R4. This action results in the output connection becom ing essentially zero volts becau se of the very low resistance of the transistor during saturation .

In contrast, if the input terminal were connected to the zero volt bus (dotted line), no emitter-to-base current would flow because the emitter and base would be the same voltage-zero volts. This would result in no emitter-to-collector current flow because of the very high emitter-to-collector resistance, since the transistor is not in saturation. The voltage at the output

terminal is therefore -4 volts, as determined by resistors R4 , R5, and R6. In this static control system, a signal of 0 volts d-e is an ON signal, and a signal -4 volts d-e is an OFF signal. The term “0 volts” means a load short, not the absence of voltage.

Figure 11·4 is a basic NOT circuit. An ON input produces an OFF output. Conversely, an OF F input produces an ON output.

In Fig. 11·5 and succeeding circuits, the final output of the device does not have resistor s R 4, R5, and R6, since the output will be con nected to the inputs it drives of logic elements such as AND, OR, etc. The input circuits act the same as resistors R4, R5, an d R6. The NOT circuit is shown in Fig. 11·6. This is identical to Fig. 11·5, except -12 volts d-e is indicated by P -, and zero volts d-e is indicated by P+. The input and output are repre sented by typical pin connections, numbered 1 and 4 or 5 and 8, respectively. The output terminal can drive up to 12 inputs.

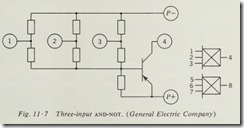

If additional parallel input circuits are added (Fig. 11·7), input terminals 1 and 2 and 3 must all be connected to zero volts (an ON signal) in order not to have current flow from

emitter to base to the P- bus. No emitter-to-base current flow will cause output terminal 4 to be at -4 volts or OFF, as a result of its connection to the next element’s input resistors. This device is functionally an AND-NOT. Terminals 1 and 2 and 3 must all have an ON signal present not to have an output.

Whenever it is stated that “there is an input” or “an output exists,” the meaning is that a zero-volt ON signal is present at the terminal point being discussed.

A seven-input AND-NOT element is also available which re quires an ON signal to exist at terminals 1 to 7 in order to cause the logic function not to have an ON signal at terminal

8. The output terminal of the AND-NOT can drive up to 12 other inputs. This transistorized static control system is sometimes called an AND-NOT system, since the basic internal circuits uti lized actually perform that function. A single-input AND-NOT is more simply expressed as a NOT, since no “AND situation” exists with a single-input device.

If a NOT is followed in a circuit by another NOT (Fig. 11·8), the input signal (OFF or ON) to the first NOT function is the

same as the output of the second NOT function. For example, if the input signal to the first NOT is OFF, its output is in the ON condition; therefore, the input to the second NOT is ON and the output is OFF. To obtain the AND function, a NOT circuit is added to the output of an AND-NOT (Fig. 11·9).

If all three inputs to the AND-NOT are present, there will not be an output; that is, an OFF signal is present. With this OFF signal to the input of the NOT , an ON signal will be produced as an output. Thus, a three-input AND is developed and is manu factured as a complete logic unit (Fig. 11·10).

An additional output, the built-in NOT of the standard output, is available in this AND-NOT system and is a very useful feature. lt is an inversion of the standard output and exists at the input connection to the last portion of the function (refer to Fig. 11·9). Figure 11·11 shows that one input connection is eliminated from the basic AND (Fig. 11·10) to gain a terminal for

the additional built-in NOT output.

A six-input AND with an additional built-in NOT output is available with input terminals 1 to 6, standard output at terminal 8, and NOT output at terminal 7. Also a seven-input AND, with input terminals 1 to 7 and output at terminal 8, is available to complete the family of AND logic functions. Each output from an AND unit can drive up to 12 other input terminals.

The OR logic function will produce an ON signal at its output terminal with an ON signal present at any one of its input terminals. The OR element circuitry differs from the AND function in that each input circuit is brought in through an isolating diode to prevent interaction between input signals (see Fig. 11·12). Two additional diodes, D4 and D 5, are also added to offset the forward voltage drop across D 1, D2, or D3 when one or more input signals are present.

In Fig. 11·12, each input is at -4 volts, and point a is also at -4 volts. When an ON signal, 0 volts, is applied to any of the three input terminals, point a swings to about -0.6 volts, and no current flows from emitter to base of the first transistor. There fore the collector of the first transistor is at -4 volts, and the second transistor goes into saturation, producing an ON signal (0 volts) at the output terminal. Additional ON signals applied to the input terminals continue an ON signal at the output ter minal. Removal of all ON input signals swings point a back to

-4 volts, which puts the first transistor into saturation and turns off the second transistor. The output terminal then reverts to its previous OFF signal, -4 volts (as supplied by the resistor input configuration of the following logic element to which it is connected). The output of the OR can drive up to 12 subsequent units. The OR function also comes in a two-input form with NOT output and a six-input form with NOT output.

The OR-NOT logic function (Fig. 11·13) will not have an ON signal at its output terminal with an ON signal at any of its input terminals. With no ON signal at the input terminals, both sides of the isolating diodes will be at -4 volts. The PNP transistor can then have emitter-to-base current flow, causing it to be saturated and to have an ON signal at the output terminal.

If an ON signal is applied to any input terminal, approximately 0 volts will appear at the cathode side of the isolating diodes. Since at least 1 volt is required to break down the forward drop of the two diodes in series, no current will flow through them with a voltage near zero volts applied at point X. This causes the PNP transistor to drop out of saturation, and an OFF signal appears at the output terminal. Removing the ON signal to the

input terminals will again cause conduction of the PNP, as the voltage at point X will again be -4 volts. The output of the OR-NOT can provide a maximum of 12 other input signals to subsequent logic functions in the logic control.

The off-return MEMORY operation can best be understood by breaking its logic down to its simplest terms as shown in Fig.11·14.

Assume initially that power has just been applied, and that neither push button is actuated. The unit reset, which is discussed later, provides a delayed ON signal.

As soon as power is applied, the A 1 and B 1 AND-NOT elements produce an output immediately, but the unit reset delays its output long enough to assure that AND-NOT B2 turns on . With AND-NOT 82 and AND-NOT A 1 both driving AND-NOT A2 with ON signals, AND-NOT A2 cannot turn on, and therefore the stan dard output is left in the OFF condition.

When the ON push button is actuated, AND-NOT A 1 loses its output, causing AND-NOT A2 to turn on and put the third ON input to AND-NOT 82, which then loses its output. The loss of this output removes the other input from AND-NOT A2, assuring an output at terminal 8 regardless of the condition of AND-NOT A 1, which might again have an output because of the releasing of the ON push button. Actuating the OFF push button will turn off AND-NOT B 1, resulting in the turning on of AND-NOT B2, which will turn off AND-NOT A2.

The first push button actuated will take precedence as long as it is being actuated. For example, actuating the ON push but ton removes the output from AND-NOT A 1, which in turn re moves an input to AND-NOT B 1. Once the input from AND-NOT B 1 is removed, actuating the OFF push button has no effect. The first input signal locks out the effect of the second while the first is being maintained. Each output of the off-return MEMORY can drive 12 other inputs.

The retentive MEMORY logic function is a modification of the off-return MEMORY, with the difference being what occurs upon restoration of system power. The retentive MEMORY will resume its previous output condition, whereas the off-return MEMORY returns to the OFF condition. As evident from Fig. 11·15, the output condition the flip-flop assumes depends upon where the unit reset is connected.

With the unit reset connected to AND-NOT B2, the retentive MEMORY will return to the OFF condition, and an ON signal will be present at terminal 7 when system power is established. With the unit reset connected to AND-NOT A2, the M EMORY will return to the ON condition, and an output will exist at termi nal 8 when system power is established.

A completely sealed single-pole double-throw reed switch is used to perform this switching function. Referring to Fig. 11·15, we see that permanent-type bias magnets hold the movable pole to its respective side of the switch, depending on which way the coil around the switch caused the movable reed to position itself. The coil, connected between terminals 7 and 8, creates sufficient flux to override the bias magnets. Current will flow in either direction through the coil, depending upon which out put terminal is at zero volts and which is at -4 volts.

The reed switch has essentially an infinite mechanical life, and in this application switches no current when the movable reed moves. Current is carried, but not switched, during a brief

period that system power is applied, that is, during the period when the unit reset delays its continuous ON signal. Thus the mechanical and electrical life of the reed switch in the retentive MEMORY is very compatible with the reliability of the transis torized static system.

The speed of operation of the retentive MEMORY is not dependent upon the speed of the reed switch. The flip-flop can switch at its maximum rate, and the reed switch can follow at a slower rate, as the last position the reed switch is in when power is lost determines its retentive position. The slow decay of 12-volt d-e power upon loss of 115-volt a-c system power is quite adequate to switch the reed to its proper position.

Because of the loading of the output terminals by the coil, the driving capability of the retentive MEMORY is 7 units, com pared with the normal rating of 12 units of load.

A unique three-input AND can be formed by combining three AND-NOTS as in Fig. 11·16. This element, called a sealed AND, requires inputs to be present at terminals 1 and 2 and 3 to cause an output at terminal 8, and then inputs at terminals 1 and 2 can be removed without affecting the output condition . The NOT of the standard output is available at terminal 7, and an auxiliary connection is required at terminal 5 to a unit reset which supplies a delayed ON signal upon application of system power.

To analyze the internal operation of the sealed AND (Fig. · 11·16), assume power has just been applied to the 12-volt bus and no inputs exist at terminals, 1, 2, or 3. Terminal 4 has been connected to terminal 3, which will cause identical effects in AND-NOT Bl. AND-NOT A 1 produces an output immediately upon applying system power, since NOT inputs are present to this AND-NOT. The unit reset always delays its output to assure that AND-NOT B 1 will momentarily be lacking one input, which results in an output from AND-NOT B 1. With AND-NOTS A 1 and B1 providing an input to AND-NOT A2 with both inputs, no output will exist at terminal 8; this causes another input to be missing to AND-NOT B 1. This continues an output from AND-NOT B 1 when the unit reset gains an output, and thereafter remains in the ON condition.

When an ON signal is applied to terminal 3, no change in output occurs in AND-NOTS A 1 or B 1, since each continues not to have all inputs present. Inputs must simultaneously be present at input terminals 1 and 2 and 3 to turn off the output of AND-NOT A 1. This removes an input from AND-NOT A 2, which results in an output at terminal 8 and also a loss of an output at terminal 7, since all inputs are now present to AND-NOT B 1. With AND-NOT BI not providing an input to AND-NOT A2 , inputs to terminals 1 and/or 2 can be removed without effecting AND-NOT A2. Only removing the input to terminal 3 will cause a change; AND-NOT B 1 gains an output, which removes the out put from terminal 8 because all inputs are again present to AND-NOT A2 .

The combination of AND-NOTS A2 and B 1 is called a flip-flop, and with terminal 4 connected to terminal 3, inputs at terminal 1 and 2 become “sealed” after all three inputs are simultaneou sly present and the flip-flop yields an output at terminal 8. The line between terminals 8 and 1 and 2 is not a wire; it is a symbol representing the sealing action. But the line from termi nal 4 to terminal 3 is a wire. With terminal 4 connected to terminal 2, only terminal 1 is sealed (refer to Fig. 11 ·17).

This arrangement in the same element still requires all three inputs to be present to gain an output at terminal 8, but now loss of input at terminals 2 or 3 will cause AND-NOT B 1 to have an output at terminal 7 and subsequent loss of output at terminal 8. The sealed AND is then not “picked up,” an ON signal being present at the built-in NOT, at terminal 7. Each output terminal of the sealed AND can drive 12 other outputs.

The DELAY element provides time delay upon energizing with a variety of individual timing ranges. Timing occurs when an RC network is being charged and results in the firing of a uni junction transistor. The RC time constant is variable by an adjustable linear potentiometer. A unijunction transistor is a unique semiconductor having three leads-an emitter and two bases. Fig. 11·18 depicts a unijunction transistor in a typical timing circuit. With the switch closed (no emitter voltage), there is no conduction between base 1 and base 2, and Vb 1b2 is close to 12 volts (R1 and R2 have low values) . When the switch is opened, the capacitor starts to charge. When the emitter voltage reaches approximately 75 percent of Vb1b2, conduction occurs. At this point, the impedance between base 1 to base 2 drops, and a significant current flows through R2, producing an output signal. The timing period is initiated when charging current is permitted to flow into the RC network, and the length of time is determined by adjustment of R3.

When an ON signal is applied to terminal 1 (Fig. 11 ·19), the instantaneous NOT output at terminal 2 turns off, and the tran sistor in the following NOT goes into conduction . This conduction establishes a base-to-base voltage difference at the unijunction transistor and simultaneously permits charging current to flow into the RC network. As voltage in the RC network builds up, a time delay upon energizing results. The unijunction triggers when the RC network’s voltage rises sufficient ly, and a pulse is introduced in the flip-flop. Terminal 8 turns on, and this causes terminal 7 to turn off, setting the flip-flop. Only loss of an input to terminal 1 will reset the flip-flop and completely discharge the RC network by removing the base-to-ba se voltage difference on the umjunction transistor.

Terminal 7 is the NOT of terminal 8 and can be considered equivalent to the normally closed time opening contact on a time-delay-on-energizing pneumatic timer. Terminal 8 is equiv alent to the normally open time closing contact; terminal 2, the NOT of the DELAY input signal at terminal 1, is equivalent to the instantaneous normally closed contact; and terminal 1 is equivalent to the instantaneous normally open contact when compared to a conventional pneumatic timing relay. The remote time-adjusting potentiometer, an optional form of the basic DELAY, would be connected to terminals 3 and 4.

The repeatability over the operating range of the DELAY is -+- 5 percent of the time setting of the device, or -+-1 percent if ambient temperature is held constant. The recommended mini mum reset time for the above repeatability is 0.5 percent of the maximum time setting of the individual DELAY .

A TDOD (time-delay-on-deenergization) form of the DELAY is also available (see Fig. 11·20). This comes in ranges of 0.4 to 12 seconds and 8 to 300 seconds. The internal circuitry effectively is that shown in Fig. 11·20. An ON signal at the input causes an immediate output at pin 8. Loss of the ON signal at pin 1 results in loss of the ON signal at pin 8 x seconds later.