Input/Output Pins, Ports, and Circuits

One major feature of a microcontroller is the versatility built into the input/output (110) circuits that connect the 8051 to the outside world. As noted in Chapter I, microprocessor designs must add additional chips to interface with external circuitry; this ability is built into the microcontroller.

To be commercially viable, the 8051 had to incorporate as many functions as were technically and economically feasible. The main constraint that limits numerous functions is the number of pins available to the 8051 circuit designers. The DIP has 40 pins, and the success of the design in the marketplace was determined by the flexibility built into the use of these pins.

For this reason, 24 of the pins may each be used for one of two entirely different functions, yielding a total pin configuration of 64. The function a pin performs at any given instant depends, first, upon what is physically connected to it and, then, upon what software commands are used to "program" the pin. Both of these factors are under the complete control of the 805 J programmer and circuit designer.

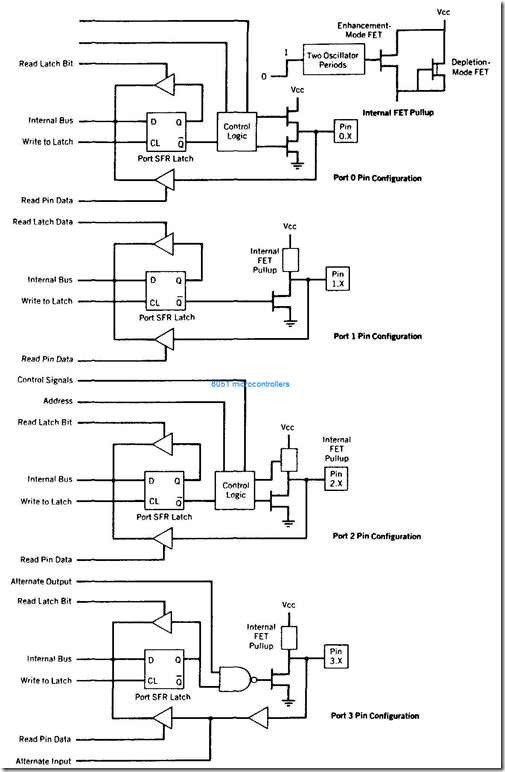

Given this pin flexibility, the 8051 may be applied simply as a single component with 1/0 only, or it may be expanded to include additional memory, parallel ports, and serial data communication by using the alternate pin assignments. The key to programming an alternate pin function is the port pin circuitry shown in Figure 7.

Each port has a D-type output latch for each pin. The SFR for each port is made up of these eight latches, which can be addressed at the SFR address for that port. For instance, the eight latches for port 0 are addressed at location 80h; port 0 pin 3 is bit 2 of the P0 SFR. The port latches should not be confused with the port pins; the data on the latches does not have to be the same as that on the pins.

The two data paths are shown in Figure 7 by the circuits that read the latch or pin data using two entirely separate buffers. The top buffer is enabled when latch data is read, and the lower buffer, when the pin state is read. The status of each latch may be read from a latch buffer, while an input buffer is connected directly to each pin so that the pin status may be read independently of the latch state.

Different opcodes access the latch or pin states as appropriate. Port operations are determined by the manner in which the 8051 is connected to external circuitry.

Programmable port pins have completely different alternate functions. The configuration of the control circuitry between the output latch and the port pin determines the nature of any particular port pin function. An inspection of Figure 7 reveals that only port I cannot have alternate functions; ports 0, 2, and 3 can be programmed.

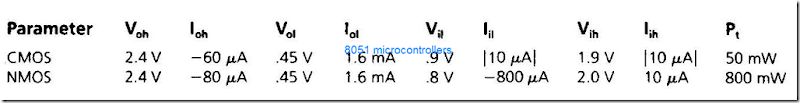

The ports are not capable of driving loads that require currents in the tens of milliamperes (mA). As previously mentioned, the 8051 has many family members, and many are fabricated in varying technologies. An example range of logic-level currents, voltages, and total device power requirements is given in the following table:

These figures tell us that driving more than two LSTTL inputs degrades the noise immunity of the ports and that careful attention must be paid to buffering the ports when they must drive currents in excess of those listed. Again, one must refer to the manufacturers’ data books when designing a "real" application.

Port 0

Port 0 pins may serve as inputs, outputs, or, when used together, as a bi-directional low order address and data bus for external memory. For example, when a pin is to be used as an input, a I must be written to the corresponding port 0 latch by the program, thus turning both of the output transistors off, which in turn causes the pin to "float" in a high impedance state, and the pin is essentially connected to the input buffer .

When used as an output, the pin latches that are programmed to a 0 will turn on the lower FET, grounding the pin. All latches that are programmed to a I still float; thus, external pull up resistors will be needed to supply a logic high when using port 0 as an output.

When port 0 is used as an address bus to external memory, internal control signals switch the address lines to the gates of the Field Effect Transistories (FETs). A logic I on an address bit will turn the upper FET on and the lower FET off to provide a logic high at the pin. When the address bit is a zero, the lower FET is on and the upper FET off to provide a logic low at the pin. After the address has been formed and latched into external circuits by the Address Latch Enable (ALE) pulse, the bus is turned around to become a data bus. Port 0 now reads data from the external memory and must be configured as an input, so a logic I is automatically written by internal control logic to all port 0 latches.

Port 1

Port 1 pins have no dual functions. Therefore, the output latch is connected directly to the gate of the lower FET. which has an FET circuit labeled Internal FET Pullup as an active pullup load.

Used as an input. a I is written to the latch. turning the lower FET off; the pin and the input to the pin buffer are pulled high by the FET load. An external circuit can overcome the high impedance pullup and drive the pin low to input a 0 or leave the input high for a 1 .

If used as an output. the latches containing a 1 can drive the input of an external circuit high through the pullup. If a 0 is written to the latch. the lower FET is on. the pullup is off. and the pin can drive the input of the external circuit low.

To aid in speeding up switching times when the pin is used as an output. the internal FET pull up has another FET in parallel with it. The second FET is turned on for two oscillator time periods during a low-to-high transition on the pin. as shown in Figure 7. This arrangement provides a low impedance path to the positive voltage supply to help reduce rise times in charging any parasitic capacitances in the external circuitry.

Port 2

Port 2 may be used as an input/output port similar in operation to port 1. The alternate use of port 2 is to supply a high-order address byte in conjunction with the port 0 low-order byte to address external memory.

Port 2 pins are momentarily changed by the address control signals when supplying the high byte of a 16-bit address. Port 2 latches remain stable when external memory is addressed, as they do not have to be turned around (set to 1) for data input as is the case for port 0 .

Port 3

Port 3 is an input/output port similar to port 1 . The input and output functions can be programmed under the control of the P3 latches or under the control of various other special function registers. The port 3 alternate uses are shown in the following table:

|

PIN |

ALTERNATE USE |

SFR |

|

P3.0-RXD |

Serial data input |

SBUF |

|

P3.1- TXD |

Serial data output |

SBUF |

|

P3.2-INTO |

External interrupt 0 |

TCON.l |

|

P3.3-INT1 |

External interrupt 1 |

TCON.3 |

|

P3.4- TO |

External timer 0 input |

TMOD |

|

P3.5- T1 |

External timer 1 input |

TMOD |

|

P3.6-WR |

External memory write pulse |

– |

|

P3.7-RD |

External memory read pulse |

– |

Unlike ports 0 and 2. which can have external addressing functions and change all eight port bits when in alternate use. each pin of port 3 may be individually programmed to be used either as 110 or as one of the alternate functions.