8.3 NUMERIC DATA PROCESSOR 8087

The numeric data processor is a coprocessor which has been designed to work under the control of the 8086 processor. It offers additional numeric processing capabilities. It is available in 5 MHz, 8 MHz and 10 MHz versions 8086 will perform the opcode fetch cycles and identify the instructions for 8087. Once the instruction is identified by 8086, it is allotted to 8087 for further execution.

8086-8087 couplet implements instruction level master-slave configuration. After the completion of the 8087 execution cycle, the results may be referred back to the CPU. The 8087 instructions may lie interleaved in the 8086 program as if they belong to the 8086 instruction set. It is the task of 8086 to identify the 8087 instructions from the

program, send it to the 8087 for execution and get back the results. The 8087 adds 68 new instructions to the instruction set of 8086.

8.3.1 Architecture of 8087

Fig. 8.10 8087 Architecture

8087 is divided internally into two sections namely Control unit and Numeric Extension Unit. The numeric extension unit executes all the numeric processor instructions. The control unit receives, decodes instructions, reads and writes memory operands executes the 8087 control instructions. The control unit is responsible for establishing communication between the CPU and memory and also for coordinating the data bus to check for the 8087 instructions.

The 8087 control unit internally maintains a parallel queue, identical to the status queue of the main CPU. The control unit automatically monitors the BHE / S7 line to detect the CPU type and accordingly adjusts the queue length. The 8087 uses the QS0 and QS1 pins to obtain and identify the instructions fetched by the host CPU (8086). 8086 identifies the coprocessor instructions using the ESCAPE code bits in them. Once the CPU recognizes the ESCAPE code, it triggers the execution of the numeric processor instruction in 8087.

The Numeric Extension Unit (NEU) executes all the instructions including arithmetic, logical, transcendental, and data transfer instructions. The internal data bus is 84 bits wide including 68 bit fraction, 15 bit exponent and a sign bit. When the NEU begins the execution, it pulls up the BUSY signal. This BUSY signal is connected to the TEST input of 8086. 8086 waits till the BUSY pin of 8087 goes low. i.e. 8086 waits till the 8087 executes instruction completely.

The microcode control unit generates the control signals required for execution of instructions. 8087 contains a programmable shifter which is responsible for shifting the operands during the execution of instructions like FMUL and FDIV. The data bus interface connects the internal data bus of 8087 with the CPU system data bus.

8.3.2 Signal Descriptions of 8087

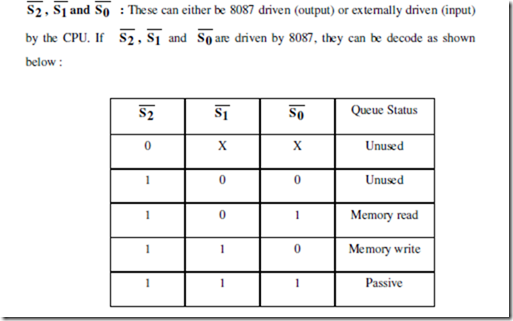

Fig. 8.11 Pin Diagram of 8087

AD0 – AD15 : These are the time multiplexed address / data lines. These lines carry addresses during T1 and data during T2, T3, Tw and T4 states.

A19 / S6 – A16/S3 : These lines are the time multiplexed address / status lines. These function in a similar way to the corresponding pins of 8086. The S6, S4 and S3 are permanently high, while the S5 is permanently low.

BHE / S7 : During T1, the BHE / S7 is used to enable data on to the higher byte of the 8086 data bus. During T2, T3, Tw and T4 this is a status line S7.

QS1 , QS0 : The queue status input signals QS1 and QS0 enable 8087 to keep track of the instruction prefetch queue status of the CPU, to maintain synchronism with it.

|

QS1 |

QS0 |

Queue Status |

|

0 |

0 |

No operation |

|

0 |

1 |

First byte of opcode from queue |

|

1 |

0 |

Empty queue |

|

1 |

1 |

Subsequent byte from queue |

INT : The interrupt output is used by 8087 to indicate that an unmasked exception has been received during execution. This is usually handled by 8259.

BUSY : This output signal, when high, indicates to the CPU that it is busy with the execution of allotted instruction. This is usually connected to the TEST pin of 8086.

READY : This input signal may be used to inform the coprocessor that the addressed device with complete the data the transfer from inside and the bus is likely to be free for the next cycle.

RESET : This input signal is used to abandon the internal activities of the coprocessor and prepare it for further execution whenever asked by the main CPU.

CLK : The CLK input provides the basic timings for the processor operation.

VCC : A +5 V supply line required for operation of the circuit.

GND : A return line for the power supply.

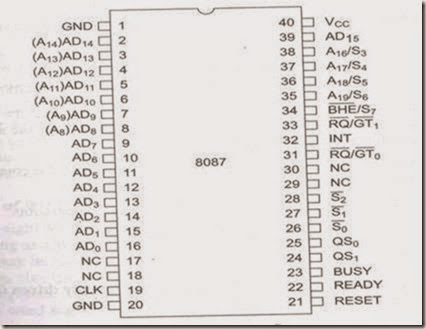

S2 , S1 and S0 becomes active during T4 (of previous bus cycle) and becomes suspended during T3 of the next bus cycle S2 , S1 and S0 acts as input signals if the CPU is executing a task.

RQ / GT0 : The Request / Grant pin is used by the 8087 to gain control of the bus from the host 8086 / 8088 for operand transfers. It must be connected to the one of the request / grant pin of the host.An active low pulse of one clock duration is generated by 8087 for the host to inform that it wants to gain control of the local bus for itself or for other coprocessor connected to RQ / GT1 pin of the 8087. When 8087 receives a grant pulse, it either initiates a bus cycle if the request is for itself or else, it passes the grant pulse to RQ / GT1, if the request is for the other coprocessor.

RQ / GT1 : This bidirectional pin is used by the other bus masters to convey their need of the local bus access to 8087. This request is conveyed to the host CPU using RQ / GT0 pin. The requesting bus master gains the control of the bus till it needs. At the end, the requesting bus master issues an active low pulse to 8087, to indicate that the task is over and 8087 may regain the control of the bus.

8.3.3 Register Set of 8087

The 8087 has a set of eight 80-bit registers that can be used be used as a stack or a set of general registers. When operating as a stack, it operates from the top on one or two registers. When operating as a register set, they may be used only with the instructions designed for them. Registers of 8087 are divided into three fields namely : sign (1-bit) , exponent (15-bits) and significand (64 bits).

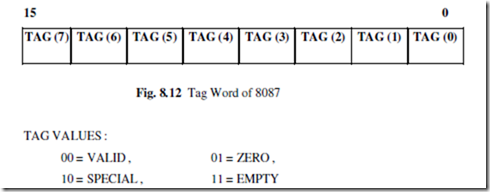

Corresponding to each of the 8 registers, there is a two bit TAG field to indicate the status of contents as shown below:

The TAG word register presents all the TAG fields to CPU. The instructions may address data registers either implicitly or explicitly. An internal status register field, ‘TOP’ is used to address any one of the 8 registers implicitly. While explicitly addressing the registers, they may be addressed relative to ‘TOP’.

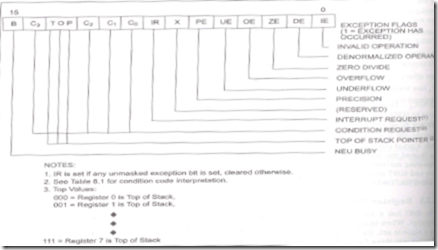

Status word of 8087

Fig. 8.13 Status word of 8087

The bit definitions of status field are as follows :

B0 – B5 : These bits indicate that an exception has been detected. These 6 bits are used to indicate the 6 types of previously generated exceptions.

B7 : This bit is set if any unmasked exception has been detected ; otherwise this is cleared.

B8 – B10 and B14 : These 4 condition code bits reflect the status of the results calculated by the 8087.

B15 : The BUSY bit shows the status of NEU (Numeric Execution Unit).

Instruction and Data Pointers

The instruction and data pointers are used to enable the programmers to write their own exception handling subroutines. Before executing a mathematical instruction, the instruction pointer and the data pointer contain the current address of the instruction and the corresponding data.

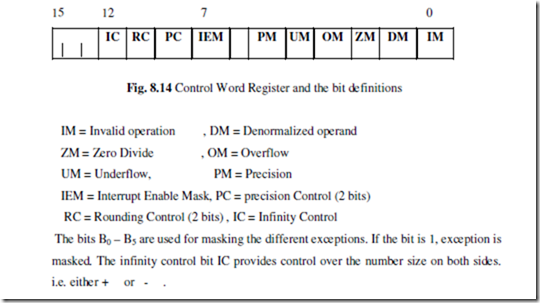

Control Word Register

The control word register of 8087 allows the programmer to select the required processing options out of available ones. In other words, the 16-bit control word register is used to control the operation of the 8087.

8.3.4 Exception Handling

The 8087, while executing an instruction, may generate 6 different exceptions. Any of these exceptions, if generated, causes an interrupt to the CPU provided it is not masked. The CPU will respond if the interrupt flag of the CPU is set.

Invalid Operation : These are the exceptions generated due to stack overflow, or stack underflow, indeterminate form as result, or, non-number as operand.

Overflow : A too big result to fit in the format generates this exception.

Underflow : If a small (in magnitude) result is generated, to fit in the specified format, 8087 generates this exception.

Zero Divide : If any non-zero finite operand is divided by zero, this exception is generated.

Denormalized Operand : This exception is generated, if at least one of the operands is denormalized.

Inexact Result : if it is impossible to fit the actual result in the specified format, this exception is generated.

8.3.5 Instruction Set of 8087

The 8087 adds 68 instructions to the instruction set of 8086, all of which may lie interleaved in an 8086 ALP. The 8087 instructions are fetched by 8086 but are executed by 8087. Whenever the 8086 comes across 8087 instruction, it executes the ESCAPE instruction code to pass over the instruction opcode and control of the local bus to 8087. The additional instructions supported by 8087 can categorized into the following types:

1. Data Transfer Instructions.

2. Arithmetic Instructions.

3. Comparison Instructions.

4. Transcendental Operations.

5. Constant Operations.

6. Coprocessor Control Operations.

Data Transfer Instructions

Depending upon the data types handled, these are further grouped into 3 types.

• Floating Point Data Transfer.

• Integer Data Transfer.

• BCD Data Transfer.

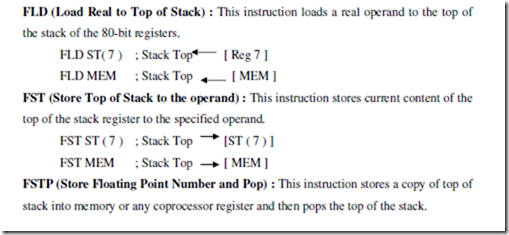

Floating Point Data Transfer Instructions

FXCH (Exchange with Top of Stack) : This instruction exchanges the contents of the top of stack with the specified operand register.

Integer Data Transfer Instructions

FILD (Load Integer to Stack Top : This instruction loads the specified integer data operand to the top of stack.

FIST / FISTP : Both the instructions work in an exactly similar manner as FST / FSTP except the fact that the operands are integer operands.

BCD Data Transfer Instructions

The 8087 instruction set has two instructions of this type, namely, FBLD and FBSTP. Both the instructions work in an exactly similar as FLD and FSTP except for the operand type BCD.

Arithmetic Instructions

The 8087 instruction set contains 11 instructions that can either be directly used to perform arithmetic operations or supporting operations like scaling, rounding, negation, absolute value, etc.

FADD

The instruction FADD performs real or integer addition of the specified operand with the stack top. The results are stored in destination operand controlled by the D-bit. The operand may be any of the stack registers or a memory location.

FSQRT : This instruction finds out the square root of the content of the stack top and stores the result on stack top again.

FSUB : The instruction FSUB performs real or integer subtraction of the specified operand from the stack top.

FMUL : This instruction performs real or integer multiplication of the specified operand with stack top.

FDIV : This instruction performs real or integer division.

FSCAL : This instruction multiplies the content of the stack top by 2n, where n is the integer part of ST (1) and stores the result in ST.

FPREM : This instruction divides the stack top by ST (1) and stores the remainder to stack top.

FRNDINT : This instruction rounds the contents of ST (0) to its integer value. The rounding is controlled by the RC field of the control word.

FXTRACT : This instruction extracts the exponent and fraction of the stack top and stores them in the stack registers.

FABS : This instruction replaces the content of the stack top by its absolute value (magnitude).

FCSH ; This instruction changes the sign of the content of the stack top.

Transcendental Instructions

The 8087 provides 5 instructions for transcendental calculations. The operands are usually ST (0) and ST (1) or only ST (0).

FPTAN : This instruction calculates the partial tangent of an angle θ, where θ must be in the range from 0 ≤ θ < 900 .

FPATAN : This instruction calculates the arctangent (inverse tangent) of a ratio ST / ST (1).

F2XMI : This instruction calculates the expression (2x-1). The value of x is stored at the top of the stack. The result is stored back at the top of the stack.

FLY2X : This instruction calculates the expression ST(1)*log2 ST. A pop operation is carried out on the top of Stack. The ST must be in the range 0 to +∞, while the ST(1) must be in the range – ∞ to +∞.

FLY2XPI : This instruction is used to calculate the expression ‘ST(1) *log2 [(ST)+1]’. The result is stored back on the stack top after a pop operation. The value of |ST| must lie between 0 and (1-21/2/2) and the value of ST(1) must be between -∞ to +∞.

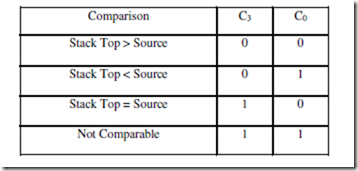

Comparison Instructions : All the comparison instructions Compare the operands and modify condition code flags as shown below :

FCOM :

This instruction compares real or integer operands specified by stack registers or memory. This instruction has the top of stack as an implicit operand. The content of the top of stack is compared either with the contents of a memory location or with the contents of another stack register. The conditional code flags bits (C3 and C0) are accordingly modified.

FCOMP and FCOMPP:

These instructions also work in an exactly similar manner as FCOM does. But the FCOMP instruction carries out one pop operation after the execution of the FCOM instruction. FCOMPP carries out two pop operations after the execution of the FCOM instruction. The FCOMP and FCOMPP instructions have the top of the stack as an implicit operand.

FIST : This instruction tests if the contents of the stack top is zero. Here, the contents of the stack top is compared with zero and the condition code flags are accordingly modified. The zero is considered as the source operand.

FXAM : This instruction examines the contents of the stack top and modifies the contents of the condition flags.

Constant Returning Instructions : These instructions load the specific constants to the top of the register stack. The stack top is an implicit operand in this type of instructions. FLDZ : Load +0.0 to stack top.

FLDI : Load +1.0 to stack top.

FLDPI : Load π to stack top.

FLD2T : Load the constant log2 10 to stack top. FLDL2E : Load the constant log2 e to stack top. FLDLG2 : Load the constant log10 2 to stack top. FLDLN2 : Load the constant loge 2 to stack top. Coprocessor Control Instructions

The coprocessor control instructions are either used to program the numeric processor. These are also used to handle the functions like exception handling, flags manipulations, processor environment maintenance and preparation.

FINIT : This instruction prepares the 8087 for further execution. It performs the same function as the hardware reset. All flags are cleared and stack top is initialized at ST(0). FENI : This instruction enables the interrupt structure and response mechanism of 8087.

i.e. The interrupt mask flag is cleared.

FDISI : This instruction sets the interrupt mask flag to disable the interrupt response mechanism of 8087.

FLDCW : This instruction loads the control word of 8087 from the specified source operand. Any addressing mode allowed in 8086 may be used to refer the memory operand.

FSTCW : This instruction may be used to store the contents of the 8087 control word register to a memory location, addressed using any of the 8086 addressing modes. FSTSW : This instruction stores the current contents of the status word register to a memory location, addressed using any of the 8086 addressing modes.

FCLEX : This instruction clears all the previously set exception flags in the status register. This also clears the BUSY and IR flags of the status word.

FINCSTP : This instruction modifies the TOP bits of the status register so as to point to the next stack register.

FDECSTP : This instruction updates the TOP bits of the stack register so as to point to the previous register in stack.

FFREE : This instruction marks the TAG field of the operand stack register to be empty. FNOP : This is a NOP instruction of the coprocessor. No internal status or control flag bits change. This requires up to 16 clock cycles for execution.

FWAIT : This instruction is used by 8087 to make 8086 wait till it completes the current operation. The BUSY pin of 8087 is tied high by 8087 to inform the host CPU that the allotted task is still under execution.

FSTENV : This instruction is used to store the environment of the coprocessor to a destination memory location specified in the instruction using any of the 8086 addressing modes.

FLDENV : This instruction loads the environment (that may be previously stored in the memory using FSTENV instruction) of the coprocessor into it.

FSAVE : This instruction saves the complete processor status into the memory, at the address specified by the destination operand. The complete status of the processor requires 94 bytes of memory.

FRSTOR : Using this instruction it is possible to restore the previous status of the coprocessor from a source memory operand.

8.3.6 Interfacing 8087 with 8086 / 8088

Fig. 8.15 Interfacing 8087 with 8086 / 8088

8087 can be connected to 8086 / 8088 only in their maximum mode of operation. In the maximum mode, all the control signals are derived using a separate chip called as a bus controller. The 8288 is a bus controller compatible with 8086 / 8088. The BUSY pin of 8087 is connected to the TEST pin of the CPU. The QS0 and QS1 lines may be directly connected to the corresponding pins in the case of 8086 /8088 based systems.

The clock pin of 8087 is connected to clock input of CPU. The interrupt output of 8087 is connected to the CPU through a Programmable Interrupt Controller 8259. The pins AD0 – AD15, BHE / S7, RESET, A19 / S6 – A16 / S3 of 8087 are connected to corresponding pins of the CPU.

Addressing Modes and Data Types

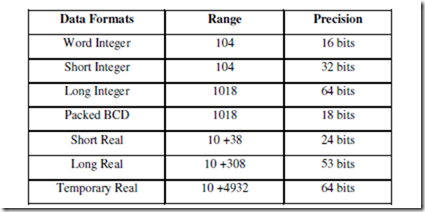

8087 supports all the addressing modes supported by 8086. The data types supported by 8087 are :

Write a procedure to calculate the volume of a sphere.

This procedure utilizes service of the register stack of 8087 to store the data temporarily

.8087

DATA SEGMENT

RADIUS DD 5.0233

CONS EQU 1.333

VOLUME DD 1 DUP (?)

DATA ENDS

ASSUME CS:CODE, DS:DATA

VOL PROC NEAR

CODE SEGMENT

START : MOV AX,DATA

MOV DS,AX ; Initialize Data Segment

FINIT ; Initialize 8087

FLD RADIUS ; Read radius into stack top

FST ST(4) ; Store stack top

FMUL ST(4)

FMUL ST(4)

FLD CONST ; Get constant 1.333

FMUL ; Multiply with (r3)

FLDPI ; Get PI (p)

FMUL ; Multiply with PI

FST VOLUME ; Store volume in VOLUME

RETP

RETP

VOL ENDP

CODE ENDS

END START