QUESTIONS AND PROBLEMS

11.1 Discuss the typical features of 32-bit and 64-bit microprocessors.

11.2

(a) What is the basic difference between the 80386 and 80386SX?

(b) What is the basic difference between the 80386 and 80486?

11.3 What is the difference between the 80386 protected, real-address, and virtual 8086 modes?

11.4 Discuss the basic features of the 80486.

11.5 Assume the following 80386 register contents

(EBX) = 00001000H

(ECX)=04000002H

(EDX) = 20005000H

prior to execution of each of the following 80386 instructions. Determine the contents of the affected registers and/or memory locations after execution of each of the following instructions and identify the addressing modes:

(a) MOV [EBX * 4] [ECX], EDX

(b) MOV [EBX * 2] [ECX + 2020H], EDX

11.6 Determine the effect of each of the following 80386 instructions:

(a) MOVZX EAX, CH

Prior to execution of this MOVZX instruction, assume

(EAX) = 80001234H

(ECX) = 00008080H

(b) MOVSX EDX, BL

Prior to execution of this MOVSX assume

(EDX) = FFFFFFFFH

(EBX) = 05218888H

11.7 Write an 80386 assembly program to add a 64-bit number in ECX: EDX with another 64-bit number in EAX: EBX. Store the result in EAX: EBX.

11.8 Write an 80386 assembly program to divide a signed 32-bit number in DX:AX by an 8-bit signed number in BH. Store the 16-bit quotient and 16-bit remainder in AX and DX respectively.

11.9 Write an 80386 assembly program to compute

where N = I 000 and the X;’s are signed 32-bit numbers.

Assume that LX? can be stored as a 32-bit number.

11.10 Discuss 80386 I/O.

11.11 Compare the on-chip hardware features of the 80486 and Pentium micro processors.

11.12 What are the sizes of the address and data buses of the 80486 and the Pentium?

11.13 Identify the main differences between the 80486 and the Pentium.

11.14 What are the clock speed, pipeline model, number of on-chip transistors, and number of pins on the 80486 and Pentium processors?

11.15 Discuss typical applications of Pentium.

11.16 Identify the main differences between the Intel80386 and 80486.

11.17 What is meant by the 80486 BUS BACKOFF feature?

11.18 How many pipeline stages are in Pentium and Pentium Pro?

11.19 How many new instructions are added to the 80486 beyond those of the 80386?

11.20 Given the following register contents,

(EBX) = 7F271 08AH

(ECX) = 2A157241H

what is the content of ECX after execution of the following 80486 instruction sequence:

MOV EBX,ECX

BSWAP ECX

BSWAP ECX

BSWAP ECX

BSWAP ECX

11.21 If (EBX) = 0123A212H and (EDX) = 46B12310H, then what are the contents of EBX and EDX after execution of the 80486 instruction XADD EBX, EDX?

11.22 If (BX) = 271AH, (AX)= 712EH, and (CX) = 1234H, what are the contents of AX after execution of the 80486 instruction CMPXCHG ex, BX?

11.23 What are three modes of the Pentium processor? Discuss them briefly.

11.24 What is meant by the statement, "The Pentium processor is based on a superscalar design"?

11.25 What are the purposes of the U pipe and V pipe of the Pentium processor?

11.26 What are the sizes of the data and instruction caches in the Pentium?

11.27 Summarize the basic differences among Pentium, Pentium Pro, and Pentium II, Ce1eron, Pentium II Xeon, Pentium III, and Pentium III Xeon processors.

11.28 Why are the Pentium Pro’s complete capabilities not used by the Windows 95 operating system?

11.29 Summarize the basic features of the Intel/Hewlett-Packard "Merced" microprocessor.

11.30 Summarize the basic differences between the 68000, 68020, 68030, 68040 and 68060.

11.31 What is the unique feature of the Power PC microprocessor family?

11.32 Name three new 68020 instructions that are not provided with the 68000.

11.33 Find the contents of the affected registers and memory locations after execution of the 68020 instruction MOVE ( $10 0 0 , AS , D 3 .w * 4 ) , D 1.Assume the following data prior to execution of this MOVE:

[AS]= $0000F210, [$ 00014218] = $4567

[D3] = $00001002, [$ 0001421A] = $2345

[Dl] = $F125012A

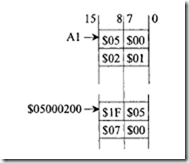

11.34 Assume the following 68020 memory configuration:

Find the contents of the affected memory locations after execution of MOVE .W #$1234, ( [Al]).

11.35 Find the 68020 compare instruction with the appropriate addressing mode to replace the following 68000 instruction sequence:

ASL. L #l, D5

CMP. L 0 (AO I D5. L) I D0

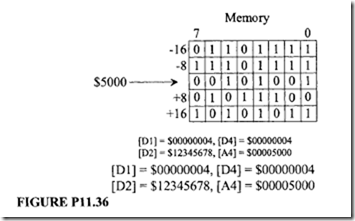

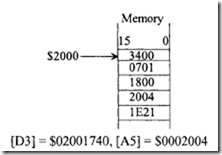

11.36 Find the contents of D I, D2, A4, and CCR and the memory locations after execution of each of the following 68020 instructions:

11.37 Identify the following 68020 instructions as valid or invalid. Justify your answers.

(a) DIVS A0, Dl

(b) CHK.B D0, (A0)

(c) MOVE.L D0, (A0)

It is given that [A0] = $1025671A prior to execution of the MOVE.

11.38 Determine the values of the Z and C flags after execution of each of the following 68020 instructions:

(a) CHK2. W (A5), D3

(b) CMP2. L $2001 I A5

Assume the following data prior to execution of each of these instructions:

11.39 Write a 68020 assembly program to add two 64-bit numbers in D1D0 with another 64-bit number in D2D3. Store the result in D1D0.

11.40 Write a 68020 assembly program to multiply a 32-bit signed number in D5 by another 16-bit signed number in D 1. Store the 64-bit result in D5B 1.

11.41 Write a subroutine in 68020 assembly language to compute ![]()

Assume the X1 ‘s are signed 32-bit numbers and the array starts at $50000021. Neglect overflow.

11.42 Write a program in 68020 assembly language to find the first one in a bit field which is greater than or equal to 16 bits and less than or equal to 512 bits. Assume that the number of bits to be checked is divisible by 16. If no ones are found, store zero in D3; otherwise store the offset of the first set bit in D3, and then stop. Assume A2 contains the starting address of the array, and D2 contains the number of bits in the array.

11.43 Write a program in 68020 assembly language to multiply a signed byte by a 32-bit signed number to obtain a 64-bit result. Assume that the numbers are respectively pointed to by the addresses that are passed on to the user stack by a subroutine pointed to by (A7+6) and (A7+8). Store the 64-bit result in D2:Dl.

11.44 What is meant by 68020 dynamic bus sizing?

11.45 Consider the 68020 instruction MOVE .B D 1,$ 0 0 0 0 0 0 16. Find the 68020 data pins over which data will be transferred if DSACK 1 DSACKO = 00. What are the 68020 data pins if DSACK l DSACKO = 10?

11.46 If a 32-bit data is transferred using 68020 MOVE. L DO, $50 6 0 7 011 instruction to a 32-bit memory with [DO]= $81F2756l, how many bus cycles are needed to perform the transfer? What are A 1A0 equal to during each cycle? What is the SIZ 1 SIZO code during each cycle? What bytes of data are transferred during each bus cycle?

11.47 Discuss 68020 I/O.

11.48 What do you mean by the unified cache of the 601? What is its size?

11.49 List the user-level and general-purpose registers of the 601.

11.50 Name one supervisor-level register in the 601. What is its purpose?

11.51 How does the 601 MSR indicate the following:

(a) The 601 executes both the user- and supervisor- level instructions.

(b) The 601 executes only the user-level instructions.

11.52 Explain the operation performed by each of the following 601 instructions:

(a) add. r1,r2,r3

(b) divwu r2,r3,r4

(c) extsb r1,r2

11.53 Discuss briefly the exceptions included in the PowerPC 601.

11.54 Compare the basic features of the 601 with the 620. Discuss PowerPC 64-bit MP’s.

11.55 Summarize the basic features of Motorola’s state-of-the-art microprocessors.