MOTOROLA MC68000

This chapter describes the basic features of Motorola’s MC68000 (16-bit microprocessor). The addressing modes, instruction set, I/O, and system design concepts of the MC68000 are covered in detail.

Motorola’s original MC68000 was designed using HMOS technology. Motorola’s MC68000 is replaced it by a lower power MC68HC000, which is designed using HCMOS technology. The MC68HC000 is equivalent to the MC68000 in all aspects except that the MC68HC000 is designed using HCMOS whereas the MC68000 was designed using HMOS technology. This means that unlike the MC68000, the unused inputs of the MC68HC000 should not be kept floating, they should be connected to +5 V, ground, or outputs of other chips as appropriate. Also, note that an HCMOS output can drive l 0 LSTTL inputs. However, an LSTTL output is not guaranteed to provide HCMOS input voltage. Hence, the HCT gates may be required when driving HC inputs. The MC 68HC000 has the same registers, addressing modes, instruction set, pins and signals, and I/O capabilities as the MC68000. The term "MC68000" will be used interchangeably with the term "MC68HC000" throughout this chapter.

The MC68HC000, implemented in HCMOS, is applicable to designs for which the following considerations are relevant:

-

The MC68HC000 completely satisfies the input/output drive requirements ofHCMOS logic devices.

-

The· MC68HC000 provides an order of magnitude reduction in power dissipation when compared to the HMOS MC68000.

-

The minimum operating frequency of the MC68HC000 is 4 MHz.

Although the MC68HC000 is implemented with input protection diodes, care should be exercised to ensure that the maximum input voltage specification (-0.3 V to +6.5 V) is not exceeded.

10.1 Introduction

The MC68000 is Motorola’s first 16-bit microprocessor. Its address and data registers are all 32 bits wide, and its ALU is 16 bits wide. The 68000 requires a single 5-V supply. The processor can be operated from a maximum internal clock frequency of 25 MHz. The 68000 is available in several frequencies, including 4, 6, 8, 10, 12.5, 16.67, and 25 MHz. The 68000 does not have on-chip clock circuitly and therefore, requires an external crystal oscillator or clock generator/driver circuit to generate the clock.

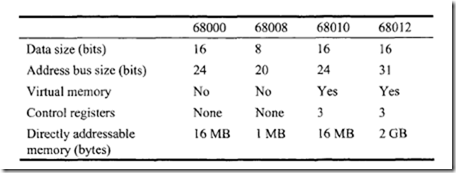

The 68000 has several different versions, which include the 68008, 68010, and 68012. The 68000 and 68010 are packaged either in a 64-pin DIP (dual in-line package)

with all pins assigned or in a 68-pin quad pack or PGA (pin grid array) with some unused pins. The 68000 is also packaged in 68-terminal chip carrier. The 68008 is packed in a 48- pin dual in-line package, whereas the 68012 is packed in an 84-pin grid array. The 68008 provides the basic 68000 capabilities with inexpensive packaging. It has an 8-bit data bus, which facilitates the interfacing of this chip to inexpensive 8-bit peripheral chips. The 680 I 0 provides hardware-based virtual memory support and efficient l00ping instructions. Like the 68000, it has a 16-bit data bus and a 24-bit address bus. The 68012 includes all the 68010 features with a 31-bit address bus. The clock frequencies of the 68008, 68010, and 68012 are the same as those of the 68000. The following table summarizes the basic differences among the 68000 family members:

To implement operating systems and protection features, the 68000 can be operated in two modes: supervisor and user. The supervisor mode is also called the "operating system mode." In this mode, the 68000 can execute all instructions. The 68000 operates in one of these modes based on the S bit of the status register. When the S bit is 1, the 68000 operates in the supervisor mode; when the S bit is 0, the 68000 operates in the user mode.

To implement operating systems and protection features, the 68000 can be operated in two modes: supervisor and user. The supervisor mode is also called the "operating system mode." In this mode, the 68000 can execute all instructions. The 68000 operates in one of these modes based on the S bit of the status register. When the S bit is 1, the 68000 operates in the supervisor mode; when the S bit is 0, the 68000 operates in the user mode.

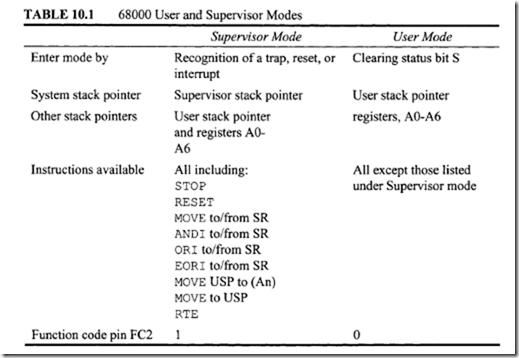

Table 10.1 lists the basic differences between the 68000 user and supervisor modes. From Table I 0.1, it can be seen that the 68000 executing a program in the supervisor mode can enter the user mode by modifying the S bit of the status register to 0 via an instruction. Instructions such as MOVE to SR, ANDI to SR, and EORI to SR can be used to accomplish this. On the other hand, the 68000 executing a program in the user mode can enter the supervisor mode only via recognition of a trap, reset, or interrupt. Note that, upon hardware reset, the 68000 operates in the supervisor mode and can execute all instructions. An attempt to execute privileged instructions (instructions that can only be execut.ed in the supervisor mode) in the user mode will automatically generate an internal interrupt (trap) by the 68000.

The logical level in the 68000 function code pin (FC2) indicates to the external devices whether the 68000 is currently operating in the user or supervisor mode. The 68000 has three function code pins (FC2, FC1, and FCO), which indicate to the external devices whether the 68000 is accessing supervisor program/data or user program/data or performing an interrupt acknowledge cycle.

The 68000 can operate on five different data types: bits, 4-bit binary-coded decimal (BCD) digits, bytes, 16-bit words, and 32-bit long words. The 68000 instruction set includes 56 basic instruction types. With 14 addressing modes, 56 instructions, and 5 data types, the 68000 contains over I 000 op-codes. The fastest instruction is one that copies the contents of one register into another register. It is executed in 500 ns at an 8- MHz clock rate. The slowest instruction is 32-bit by 16-bit divide, which in executed in 1.25 JlS at 8 MHz. The 68000 has no I/O instructions. Thus, the I/O is memory mapped.

Hence, MOVE instructions between a register and a memory address are also used as I/O instructions. The MC68000 is a general-purpose register-based microprocessor. Although the 68000 PC is 32 bits wide, only the low-order 24 bits are used. Because this is a byte-

addressable machine, it follows that the 68000 microprocessor can directly address 16 MB of memory. Note that symbol [ ] is used in the examples throughout this chapter to indicate the contents of a 68000 register or a memory location.

10.2 68000 Registers

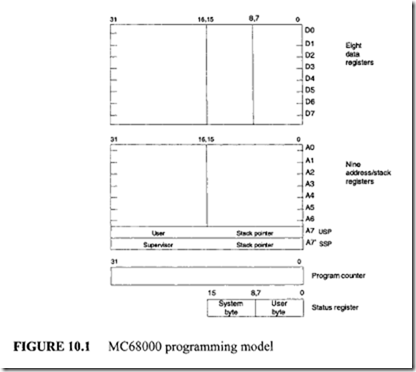

Figure 10.1 shows the 68000 registers. This microprocessor includes eight 32-bit data registers (DO-D7) and nine 32-bit address registers (AO-A 7 plus A 7′). Data registers normally hold data items such as 8-bit bytes, 16-bit words, and 32-bit long words. An address register usually holds the memory address of an operand; AO-A6 can be used as 16- or 32-bit. Because the 68000 uses 24-bit addresses, it discards the uppermost 8 bits (bits 24-31) while using the address registers to hold memory addresses. The 68000 uses A7 or A7′ as the user or supervisor stack pointer (USP or SSP), respectively, depending on the mode of operation.

The 68000 status register is composed of two bytes: a user byte and a system byte (Figure 10.2). The user byte includes typical condition codes such as C, V, N, Z, and X. The meaning of the C, V, N, and Z flags is obvious. Let us explain the meaning of the X bit. Note that the 68000 does not have any ADDC or SUBC instructions; rather, it has ADDX and sUBX instructions.

Because the flags C and X are usually affected in an identical manner, one can use ADDX or SUBX to reflect the carries or borrows in multiprecision arithmetic. The contents of the system byte include a 3-bit interrupt mask (12, II, 10), a supervisor flag (S), and a trace flag (T). When the supervisor flag is 1, then the system operates in the supervisor mode; otherwise, the user mode of operation is assumed. When the trace flag is set to 1, the processor generates a trap (internal interrupt) after executing each instruction. A debugging routine can be written at the interrupt address vector to display registers and/or memory after execution of each instruction. Thus, this will provide a single-stepping facility. Note that the trace flag can be set to one in the supervisor mode by executing the instruction ORI# $8000, SR.

The interrupt mask bits (12, I I, 10) provide the status of the 68000 interrupt pins IPL2, IPLI and IPLO. 12 II 10 = 000 indicates that all interrupts are enabled. 12 II 10 = 111 indicates that all maskable interrupts except the nonrnaskable interrupt (Level 7) are disabled. The other combinations of 12, 11, and 10 provide the maskable interrupt levels. Note that the signals on the IPL2, IPLI and IPL0 pins are inverted internally and then compared with 12, II, and 10, respectively.

10.3 68000 Memory Addressing

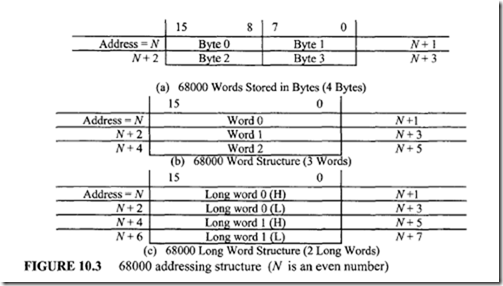

The MC68000 supports bytes (8 bits), words (16 bits), and long words (32 bits) as shown in Figure I 0.3. Byte addressing includes both odd and even addresses (0, I, 2, 3, …), word addressing includes only even addresses in increments of 2 (0, 2, 4, …), and long word addressing contains even addresses in increments of 4 (0, 4, 8, …). As an example of 68000 addressing structure, consider MOVE • L D 0 , $50 6 0 8 0 . If [DO] == $07F 12481, then after this MOVE, [$506080] == $07, [$50608I] = $Fl, [$506082] = $24, and [$506083)

= $81. In the 68000, all instructions must be located at even addresses for byte, word, and

long word instructions; otherwise, the 68000 generates an internal interrupt. The size of each 68000 instruction is even multiples of a byte. This means that once the programmer writes a program starting at an even address, all instructions are located at even addresses after assembling the program. For byte instructions, data can be located at even or odd addresses. On the other hand, data for word and long word instruction must be located at even addresses; otherwise the 68000 generates an internal interrupt.

Note that in 68000 for word and long word data, the low-order address stores the high-order byte of a number. This is called Big-endian byte ordering.

10.4 68000 Addressing Modes

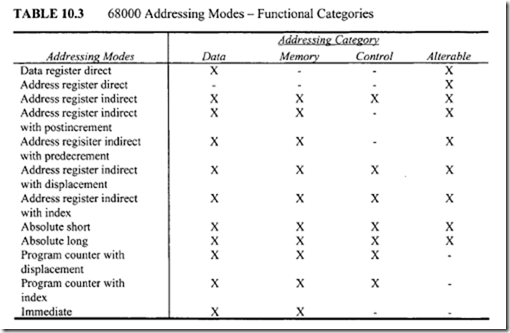

The 14 addressing modes of the 68000 shown in Table 10.2 can be divided into 6 basic groups: register direct, address register indirect, absolute, program counter relative, immediate, and implied.

As mentioned, the 68000 has three types of instructions: no operand, single operand, and double operand. The single-operand instructions contain the effective address (EA) in the operand field. The EA for these instructions is calculated by the 68000 using the addressing mode used for this operand. In the case of two-operand instructions, one of the operands usually contains the EA and the other operand is usually a register or memory location. The EA in these instructions is calculated by the 68000 based on the addressing

mode used for the EA.

Some two-operand instructions have the EA in both operands. This means that the operands in these instructions use two addressing modes. Note that the 68000 address registers do not support byte-sized operands. Therefore, when an address register is used as a source operand, either the low-order word or the entire long word operand is used, depending on the operation size. When an address register is used as the destination operand, the entire register is affected regardless of operation size. If the operation size is a word, an address register in the destination operand is sign-extended to 32 bits after the operation is performed. Data registers, on t!1e Jther hand, support data operands of byte, word, or long word size.

To identify the operand size of an instruction, the following notation is placed after a 68000 mnemonic: .B for byte, .W or none (default) for word, and .L for long word. For example,

10.4.1 Register Direct Addressing

In this mode, the eight data registers (DO-D7) or seven address registers (AO-A6) contain the data operand. For example, consider ADD. W $ 0 0 50 0 0, DO. The destination operand of this instruction is in data register direct mode. Now, if [005000] = 000216 and [DO.W] = 000316, then after execution of ADD $005000, DO, the contents ofDO.W = 0002 + 0003 = 0005. Note that in this instruction, the$ symbol is used by Motorola to represent hexadecimal numbers. Also note that instructions are not available for byte operations using address registers.

10.4.2 Address Register Indirect Addressing

There are five different types of address register indirect mode. In this mode, an address register contains the effective address. For example, consider CLR. W (Al). If [Al. L]=$00003000, then, after execution of CLR. W (Al) , the 16-bit contents of memory location $003000 will be cleared to zero.

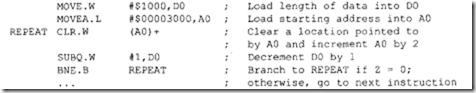

The postincrement address register indirect mode increments an address register by 1 for byte, 2 for word, and 4 for long word after it is used. For example, consider CLR. L (AO) +. If[AO] = 00005000 16, then after execution ofCLR. L (AO) +,the 16-bit contents of each of the memory locations 005000 16 and 005002 16 are cleared to zero and [AO] = 00005000 + 4 = 00005004. The postincrement mode is typically used with memory arrays stored from LOW to HIGH memory locations. For example, to clear I 00016 words starting at memory location 003000 16 and above, the following instruction sequence can be used:

Note that the symbol# in the above is used by the Motorola assember to indicate the immediate mode. This will be discussed later in this section. Also, note that CLR. W (AO) + automatically points to the next location by incrementing AO by 2 after clearing a memory location.

Note that the symbol# in the above is used by the Motorola assember to indicate the immediate mode. This will be discussed later in this section. Also, note that CLR. W (AO) + automatically points to the next location by incrementing AO by 2 after clearing a memory location.

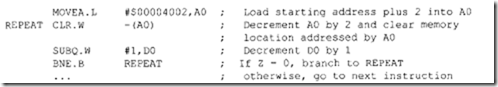

The predecrement address register indirect mode, on the other hand, decrements an address register by 1 for byte, 2 for word, and 4 for long word before using a register. For example, consider CLR. W – (AO). If [AO] = $00002004, then the content of AO is first decremented by 2-that is, [AO] = 00002002 16. The content of memory location 002002 is then cleared to zero. The predecrement mode is used with arrays stored from HIGH to LOW memory locations. For example, to clear I 00016 words starting at memory location 004000 16 and below, the following instruction sequence can be used:

In this instruction sequence, CLR. w – (A0) first decrements A0 by 2 and then clears the location. Because the starting address is 004000 16, A0 must initially be loaded with 00004002 16• It should be pointed out that the predecrement and postincrement modes can be combined in a single instruction. A typical example is MOVE. W (AS)+ 1- (A3).

The two other address register modes provide accessing of the tables by allowing offsets and indexes to be included with an indirect address pointer. The address register indirect with offset mode determines the effective address by adding a 16-bit signed integer to the contents of an address register. For example, consider MOVE. W $10 (AS) 1 D3 in which the source operand is in address register indirect with offset mode. If [A5] = 00002000 16 and [002010]16 = 0014 16, then, after execution of MOVE. W $10 (AS), D3, register D3.W will contain 001416•

The indexed register indirect with offset mode determines the effective address by adding an 8-bit signed integer and the contents of a register (data or address register) to the contents of an address (base) register. This mode is usually used when the offset from the base address register needs to be varied during program execution. The size of the index register can be a signed 16-bit integer or an unsigned 32-bit value. As an example, consider MOVE. W $10 (A4 1 D3. W) 1 D4 in which the source is in the indexed register indirect with offset mode. Note that in this instruction A4 is the base register and D3.W is the 16-bit index register (sign-extended to 32 bits). This register can be specified as 32 bits by using D3 .L in the instruction, and I 016 is the 8-bit offset that is sign-extended to 32 bits. If [A4] = 00003000 16, [D3.W] = 0200 16, and [00321016] = 002416, then this MOVE instruction will load 0024 16 into the low 16 bits of register D4.

The address register indirect with offset mode can be used to access a single table. The offset (maximum 16 bits) can be the starting address of the table (fixed number), and the address register can hold the index number in the table to be accessed. Note that the starting address plus the index number provides the address of the element to be accessed in the table. For example, consider MOVE .W $34 0 0 (AS) 1 D1. If A5 contains 04, then this MOVE instruction transfers the contents of 3404 (i.e. the fifth element, 0 being the first element) into the low 16 bits of D 1. The indexed register indirect with offset mode, on the other hand, can be used to access multiple tables. Here, the offset (maximum 8 bits) can be the element number to be accessed. The address register pointer can be used to hold the starting address of the table containing the lowest starting address, and the index register can be used to hold the difference between the starting address of the table being accessed and the table with the lowest starting address. For example, consider three tables, with table I starting at 002000 16, table 2 at 003000 16, and table 3 at 004000 16. To transfer

the seventh element (0 being the first element) in table 2 to the low 16 bits of register D0,

the instruction MOVE .W $ 0 6 ( A2 , D1.W) 1 D0 can be used, where [A2] = the starting address of the table with the lowest address(= 002000 16 in this case) and [D How 16 bits =the difference between the starting address of the table being accessed and the starting address of the table with the lowest address= 003000 16 – 002000 16 = l 00016• Therefore, this MOVE instruction will transfer the contents of address 003006 16 (the seventh element in table 2) to register DO. The indexed register indirect with offset mode can also be used to access two-dimensional arrays such as matrices.

10.4.3 Absolute Addressing

In this mode, the effective address is part of the instruction. The 68000 has two modes: absolute short addressing, in which a 16-bit address is used (the address is sign-extended to 24 bits before use), and absolute long addressing, in which a 24-bit address is used. For example, consider ADD $2 0 0 0, D2 as an example of the absolute short mode. If [$002000] = 001216 and [D2.W] = 001016,then, after executing ADD $2 0 0 0, D2, register D2.W will contain 002216• The absolute long addressing mode is used when the address size is more than 16 bits. For example, MOVE • W $2 4 0 0 0 0 , D 5 loads the 16-bit contents of memory location 240000 16 into the low 16 bits ofD5. The absolute short mode includes an address ADDR in the range of O s ADDR s $7FFF or $FF8000 s ADDR s $FFFFFF. Note that a single instruction may use both short and long absolute modes, depending on whether the source or destination address is less than, equal to, or greater than the 16-bit address. A typical example is MOVE .w $50 0 0 0 2 , $10 0 0. Also, note that the absolute long mode must be used for MOVE to or from address $008000. For example, MOVE. W $8000,D1 will move the 16-bit contents of location $FF8000 to D1 while MOVE. W $008000,D 1 will transfer the 16-bit contents of address $008000 to D 1.

10.4.4 Program Counter Relative Addressing

The 68000 has two program counter relative addressing modes: relative with offset and relative with index and offset. In the relative with offset mode, the effective address is obtained by adding the contents of the current PC with a signed 16-bit displacement. This mode can be used when the displacement needs to be fixed during program execution. Typical branch instructions such as BEQ, BRA, and BLE use the relative with offset mode. This mode can also be used by some other instructions. For example, consider ADD $30 (PC) , D5, in which the source operand is in the relative with offset mode. Now suppose that the current PC contents is $002000, the content of 002030 16 is 0005, and the low 16 bits of D5 contain 001016• Then, after execution of this ADD instruction, D5 will contain 001516•

In the relative with index and offset mode, the effective address is obtained by adding the contents of the current PC, a signed 8-bit displacement (sign-extended to 32 bits), and the contents of an index register (address or data register). The size of the index register can be 16 or 32 bits wide. For example, consider ADD. W $4 (PC, DO. W), D2. If [D2] = 00000012 16, [PC]= 002000 16, [D0]10w 16 bits = 001016,and [002014] = 000216, then, after this ADD, [D2]1ow 16 bits= 001416• This mode is used when the displacement needs to be changed during program execution by modifying the content of the Index register.

An advantage of the relative mode is that the destination address is specified relative to the address of the instruction after the instruction. Since the 68000 instructions with relative mode do not contain an absolute address, the program can be placed anywhere in memory which can still be excuted properly by the 68000. A program which can be placed anywhere in memory, and can still run correctly is called a "relocatable" program. It is a good practice to write relocatable programs.

10.4.5 Immediate Data Addressing

Two immediate modes are available with the 68000: immediate and quick immediate modes. In immediate mode, the operand data is constant data, which is part of the instruction. For example, consider ADDI. w #$0005, D0. If [DO.W] = 000216, then, after this ADDI instruction, [DO.W] = 0002 16 + 000516 = 000716• Note that the# symbol is used by Motorola to indicate the immediate mode. Quick immediate (ADD or SUBTRACT) mode allows

one to increment or decrement a register or a memory location (.B, .W, .L) by a number from 0 to 7. For example, ADDQ. B #1, D0 increments the low 8-bit contents of D0 by 1. Note that immediate data, 1 is inherent in the instruction. That is, data 0 to 7 is contained in the three bits of the instruction. Note that ADDQ.B #0, Dn is similar to NOP instruction.

10.4.6 Implied Addressing

The instructions using implied addressing mode do not require any operand, and registers such as PC, SP, or SR are referenced in these instructions. For example, RTS returns to the main program from a subroutine by placing the return address into PC using the PC implicitly.

It should be pointed out that in the 68000 the first operand of a two-operand instruction is the source and the second operand is the destination. Recall that in the case of the 8086, the first operand is the destination and the second operand is the source.