QUESTIONS AND PROBLEMS

8.1 What is the basic difference between main memory and secondary memory?

8.2 Compare the basic features of hard disk, floppy disk and Zip disk.

8.3 What are the main differences between CD and DVD memories?

8.4 Name the methods used in main memory array design. What are the advantages and disadvantages of each.

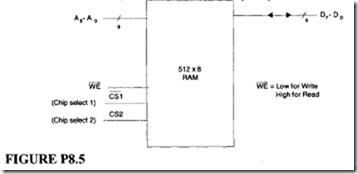

8.5 The block diagram of a 512 x 8 RAM chip is shown in Figure P8.5. In this arrangement, the memory chip is enabled only when CS 1 = L and CS2 = H. Design a 1K x 8 RAM system using this chip as the building block. Draw a neat logic diagram of your implementation. Assume that the microprocessor can directly address 64K with a RIW and 8 data pins. Using linear decoding and don’t care conditions as 1’s, determine the memory map in hex.

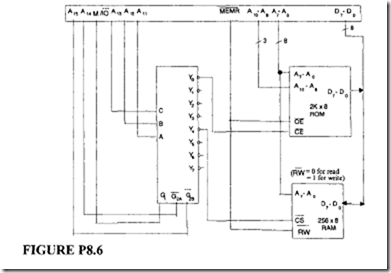

8.6 Consider the hardware schematic shown in Figure P8.6.

8.6 Consider the hardware schematic shown in Figure P8.6.

(a) Determine the address map of this system. Note: MEMR=O for read, MEMR=l for write and, M/10=0 for I/O and MI/O=l for memory.

(b) Is there any possibility of bus conflict in this organization? Clearly justify your answer.

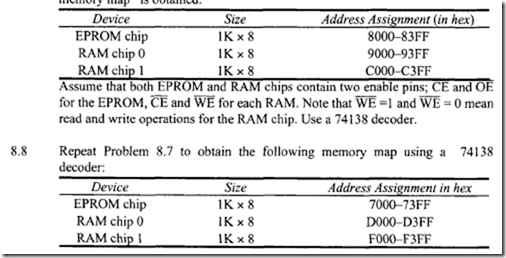

8.7 Interface a microprocessor with 16-bit address pins and 8-bit data pins and a RIW pin to a lK x 8 EPROM chip and two lK x 8 RAM chips such that the following memory map is obtained:

8.9 What is meant by "foldback" in linear decoding?

8.9 What is meant by "foldback" in linear decoding?

8.10 Comment on the importance of the following features in an operating system implementation:

(a) Address translation

(b) Protection

8.11 Explain briefly the differences between segmentation and paging.

8.12 Draw a block diagram showing the address and data lines for the 2716, 2732, and 2764 EPROM chips.

8.13 How many address and data lines are required for a 1M x 16 memory chip.

8.14 A microprocessor with 24 address pins and 8 data pins is connected to a 1K x 8 memory chip with one-chip enable. How many unused address bits of the microprocessor are available for interfacing other lK x 8 memory chips. What is the maximum directly addressable memory available with this microprocessor?

8.15 Design a direct mapped virtual memory system with the following specifications:

-

Size of the virtual address space= 64K

-

Size of the physical address space = 8K

-

Page size = 512 words

-

Total length of a page table entry = 24 bits

8.16 A virtual memory system has the following specifications:

-

Size of the virtual address space= 64K

-

Size of the physical address space= 4K

-

Page size= 512

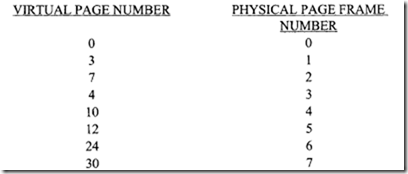

From the page table the following mapping is recognized:

(a) Find all virtual addresses that will generate a page fault.

(a) Find all virtual addresses that will generate a page fault.

(b) Compute the main memory address for the following virtual addresses:

24, 3784, 10250, 30780

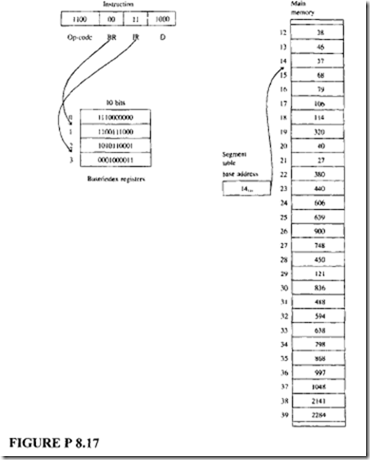

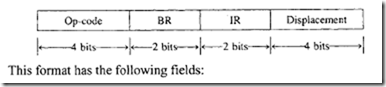

8.17 Assume a computer has a segmented memory with paged segments. (Fig. P8.17) The instruction format of this machine is as shown:

This format has the following fields:

This format has the following fields:

-

Op-code field

-

2-bit base register field BR

-

2-bit index register field IR

-

4-bit displacement field

The contents of the specified base and index registers are added with the displacement to produce a virtual address whose format is shown next:

The virtual address is translated into a physical address by means of segment and page tables, which are stored in the main memory. The segment table entry contains the starting address of its page table and the page table entry contains the address of the location which holds the page frame number. The segment table base address register contains the start address of the segment table. The final physical address is the sum of the page table entry and the offset from the virtual address. Consider the following situation:

(a) Compute the physical address needed by the given situation

(b) Howmany two-operand summations are required to compute one physical address?

8.18 Assume a main memory has 4 page frames and initially all page frames are empty.

Consider the following stream of references;

1, 2, 3, 4, 5, 1, 2, 6, 1, 2, 3, 4, 5, 6, 5

Calculate the hit ratio if the replacement policy used is as follows.

(a) FIFO

(b) LRU

8.19 Repeat Problem 8.18 when the main memory has 5 page frames instead of 4. Comment on your results.

8.20 Consider the stream of references given in Problem 8.18. Plot a graph between the hit ratio and the number of frames (f) in the main memory after computing the hit ratio for all valuesfin the range of 1 to 8. Assume LRU policy is used. (Hint: Use the stack algorithm.)

8.21 What is the size of a decoder with one chip enable (CE) to obtain a 64K x 32 memory from the 4K x 8 chips? Where are the inputs and outputs of the decoder connected?

8.22 What is the advantage of having a cache memory? Name a 32-bit microprocessor that does not contain an on-chip cache.

8.23 Discuss the various cache-mapping techniques.

8.24 A microprocessor has a main memory of 8K x 32 and a cache memory of 4K x 32. Using direct mapping, determine the sizes of the tag field, index field, and each word of the cache.

8.25 A microprocessor has a main memory of 4K x 32. Using a cache memory address of 8 bits and set-associative mapping with a set size of 2, determine the size of the cache memory.

8.26 A microprocessor can directly address one megabyte of memory with a 16- bit word size. Determine the size of each cache memory word for associative mapping.

8.27 A typical computer system has a 32K main memory and a 4K fully associative cache memory. The cache block size is 8 words. The access time for the main memory is 10 times that of the cache memory.

(a) How many hardware comparators are needed?

(b) What is the size of the tag field?

(c) If a direct mapping scheme were used instead, what would be the size of the tag field?

(d) Suppose the access efficiency is defined as the ratio of the average access time with a cache to the average access time without a cache, determine the access efficiency assuming a cache hit ratio h of0.9.

(e) If the cache access time is 200 nanoseconds, what hit ratio would be required to achieve an average access time equal to 500 nanoseconds?

8.28 A set associative cache has a total of 64 blocks divided into sets of 4 blocks each.

(a) Main memory has 1024 blocks with 16 words per block. How many bits are

needed in each of the tag, set, and word fields of the main memory address?

(b) A computer system has 32K words of main memory and a set associative cache. The block size is 16 words and the TAG field of the main memory address is 5-bit wide. If the same cache were direct mapped, the main memory will have a 3-bit TAG field. How many words are there in the cache? How many blocks are there in a cache set?

8.29 Under what condition does the set associative mapping method become one of the following?

(a) Direct mapping

(b) Fully associative mapping

8.30 Discuss the main features of Motorola 68020 on-chip cache.

8.31 What is the basic difference between:

(a) Standard I/O and memory-mapped I/O?

(b) Programmed I/O and virtual I/O?

(c) Polled I/O and interrupt I/O?

(d) A subroutine and interrupt I/O?

(e) Cycle-stealing, block transfer, and interleaved DMA?

(f) Maskable and nonmaskable interrupts?

(g) Internal and external interrupts?

(h) Memory mapping in a microprocessor and memory-mapped I/O?

8.32 Explain the significance of interleaved memory organization in pipelined computers.

8.33 Discuss the basic differences between SISD and SIMD.

8.34 The Cray- I computer has one CPU, and 12 functional units. Up to a maximum of 8 functional units can be cascaded to form a chain. Each functional unit is pipelined and the number of pipeline segments vary from l to 14. Each functional unit is capable of manipulating 64-bit data. Is it possible to describe this machine using Flynn’s approach? Explain.

8.35 Consider a processor array with 4 floating-point processors (FPP). Suppose that each FPP takes 4 time units to produce one result, how long it would take to carry out 100 floating point operations? Is there any performance improvement if the same 100 floating-point operations are carried out using a 4-segment pipelined processor in which each segment takes 1 time unit to produce the result (Ignore latch delay)?

8.36 Explain the significance of masking in array processors.

8.37 Consider the floating-point pipeline discussed in section 8.4.2. Assume:

-

T1 = 40 ns

-

T3 = 180 ns

-

T1 = 20 ns

-

T2 =100ns

-

T4 = 60 ns

(a) Determine the pipeline clock rate.

(b) Find the time taken to add 1000 pairs of floating-point numbers using this pipeline.

(c) What is the efficiency of the pipeline when 2000 pairs of floating-point

numbers are added?

8.38 Design a pipeline multiplier using carry/save adders (CSA) and carry-look-ahead adders to multiply a stream of input numbers X0, X1, X2, by a fixed number Y. Assume all Xs and Ys are 6-bit numbers. The output should be a stream of 12-bit products YX0, YX1, YX2. Draw a neat schematic diagram ofyour design.

8.39 Consider the execution of 1000 instructions using a 6-segment pipeline.

(a) What is the average number of instructions executed per instruction cycle when C = 0.2?

(b) What must be the value of C so execution of at least 4 instructions per

instruction cycle is always allowed.

8.40 Describe the methods used to handle branches in a pipeline instruction execution unit.

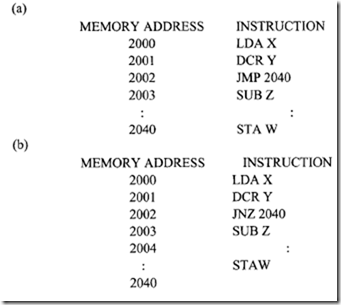

8.41 Modify each of the following programs so the data flow in the 2-segment pipeline (Figure 8.52) is properly regularized: