Counters and Timers

Many microcontroller applications require the counting of external events, such as the frequency of a pulse train, or the generation of precise internal time delays between computer actions. Both of these tasks can be accomplished using software techniques, but software loops for counting or timing keep the processor occupied so that other, perhaps more important, functions are not done. To relieve the processor of this burden, two 16-bit up counters, named T0 and T1, are provided for the general use of the programmer. Each counter may be programmed to count internal clock pulses, acting as a timer, or programmed to count external pulses as a counter.

|

Bit |

Symbol |

Function |

|

0 |

IT0 |

External interrupt 0 signal type control bit. Set to 1 by program to enable external interrupt 0 to be triggered by a falling edge signal. Set to 0 by program to enable a low level signal on external interrupt 0 to generate an interrupt. |

bit addressable as TCON.0 to TCON.7

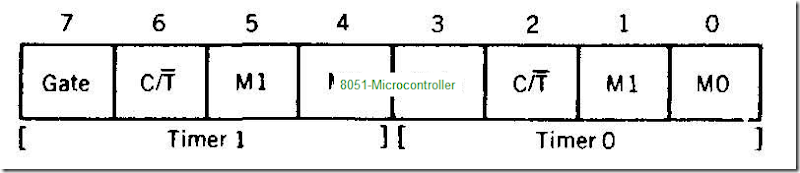

THE TIMER MODE CONTROL (TMOD) SPECIAL FUNCTION REGISTER

|

Bit |

Symbol |

Function |

|

7/3 |

Gate |

OR gate enable bit which controls RUN/STOP of timer 1/0. Set to 1 by program to enable timer to run if bit TR1/0 in TCON is set and signal on external interrupt (INT1)’/0 pin is high. Cleared to a by program to enable timer to run if bit TRI/a in TCON is set. |

|

6/2 |

C/(T)’ |

Set to 1 by program to make timer 1/0 act as a counter by counting pulses from external input pins 3.5 (T1) or 3.4 (T0). Cleared to 0 by program to make timer act as a timer by counting internal frequency. |

|

5/1 |

Ml |

Timer/counter operating mode select bit 1. Set/cleared by program to select mode. |

|

4/0 |

M0 |

Timer/counter operating mode select bit o. Set/cleared by program to select mode. |

|

M1 |

MC |

Mode |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

2 |

|

1 |

1 |

3 |

TMOD is not bit addressable

The counters are divided into two 8-bit registers called the timer low (TLO. TL I) and high (THO. TH I) bytes. All counter action is controlled by bit states in the timer mode control register (TMOD). the timer/counter control register (TCON). and certain program instructions.

TMOD is dedicated solely to the two timers and can be considered to be two duplicate 4-bit registers. each of which controls the action of one of the timers. TCON has control bits and Hags for the timers in the upper nibble. and control bits and Hags for the external interrupts in the lower nibble. Figure 10 shows the bit assignments for TMOD and TCON.

Timer Counter Interrupts

The counters have been included on the chip to relieve the processor of timing and counting chores. When the program wishes to count a certain number of internal pulses or external events, a number is placed in one of the counters. The number represents the maximum count less the desired count, plus one. The counter increments from the initial number to the maximum and then rolls over to zero on the final pulse and also sets a timer Hag. The Hag condition may be tested by an instruction to tell the program that the count has been accomplished, or the Hag may be used to interrupt the program.

figure 11 timer/counter control logic

Timing

If a counter is programmed to be a timer, it will count the internal clock frequency of the R051 oscillator divided by 12d. As an example, if the crystal frequency is 6.0 megahertz, then the timer clock will have a frequency of 500 kilohertz.

The resultant timer clock is gated to the timer by means of the circuit shown in Figure 11. In order for oscillator clock pulses to reach the timer, the CIT bit in the TMOD register must be set to 0 (timer operation). Bit TRX in the TCON register must be set to 1 (timer run), and the gate bit in the TMOD register must be 0, or external pin (INTX)’ must he a 1 . In other words, the counter is configured as a timer, then the timer pulses are gated to the counter by the run bit and the gate bit or the external input bits (INTX)’.

Timer Modes of Operation

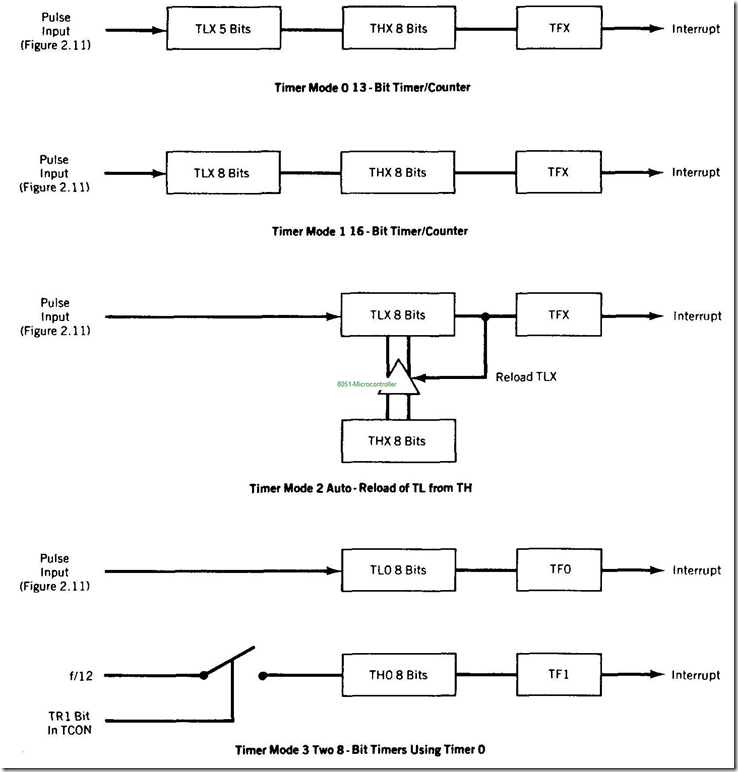

The timers may operate in anyone of four modes that are determined by the mode bits, M I and MO, in the TMOD register. Figure 12 shows the four timer modes.

Timer Mode 0

Setting timer X mode bits to 00b in the TMOD register results in using the THX register as an 8-bit counter and TLX as a 5-bit counter; the pulse input is divided by 32d in TL so that TH counts the original oscillator frequency reduced by a total 384d. As an example, the 6 megahertz oscillator frequency would result in a final frequency to TH of 15625 hertz. The timer flag is set whenever THX goes from FFh to 00h, or in .0164 seconds for a 6 megahertz crystal if THX starts at 00h.

Timer Mode 1

Mode 1 is similar to mode 0 except TLX is configured as a full 8-bit counter when the mode bits are set to 0lb in TMOD. The timer flag would be set in .1311 seconds using a 6 megahertz crystal.

FIGURE 12 Timer 1 and Timer a Operation Modes

Timer Mode 2

Setting the mode bits to l0b in TMOD configures the timer to use only the TLX counter as an 8-bit counter. THX is used to hold a value that is loaded into TLX every time TLX overflows from FFh to 00h. The timer flag is also set when TLX overflows.

This mode exhibits an auto-reload feature: TLX will count up from the number in THX. overflow. and be initialized again with the contents of THX. For example. Placing 9Ch in THX will result in a delay of exactly .0002 seconds before the overflow flag is set if a 6 megahertz crystal is used.

Timer Mode 3

Timers 0 and 1 may be programmed to be in mode 0, 1, or 2 independently of a similar mode for the other timer. This is not true for mode 3; the timers do not operate independently if mode 3 is chosen for timer 0. Placing timer I in mode 3 causes it to stop counting; the control bit TRI and the timer I flag TFI are then used by timer 0.

Timer 0 in mode 3 becomes two completely separate 8-bit counters. TL0 is controlled by the gate arrangement of Figure 11 and sets timer flag TF0 whenever it overflows from FFh to 00h. TH0 receives the timer clock (the oscillator divided by 12) under the control of TR 1 only and sets the TF1 flag when it overflows.

Timer 1 may still be used in modes 0, 1, and 2, while timer 0 is in mode 3 with one important exception: No interrupts will be generated by timer I while timer 0 is using the TF1 overflow flag. Switching timer I to mode 3 will stop it (and hold whatever count is in timer 1). Timer 1 can be used for baud rate generation for the serial port, or any other mode 0, 1, or 2 function that does not depend upon an interrupt (or any other use of the TF1 flag) for proper operation.

Counting

The only difference between counting and timing is the source of the clock pulses to the counters. When used as a timer, the clock pulses are sourced from the oscillator through the divide-by-12d circuit. When used as a counter, pin T0 (P3.4) supplies pulses to counter 0. and pin T1 (P3.5) to counter 1 . The C/(T)’ bit in TMOD must be set to 1 to enable pulses from the TX pin to reach the control circuit shown in Figure 11.

The input pulse on TX is sampled during P2 of state 5 every machine cycle. A change on the input from high to low between samples will increment the counter. Each high and low state of the input pulse must thus be held constant for at least one machine cycle to ensure reliable counting. Since this takes 24 pulses, the maximum input frequency that can be accurately counted is the oscillator frequency divided by 24. for our 6 megahertz crystal. the calculation yields a maximum external frequency of 250 kilohertz.

good

nice

It's brief enough, thank you.

nice