Analogue to digital conversions

The conversion of analogue signals into digital form is the essential first step in any system that will use digital methods for counting, display or logic actions. For some purposes it is necessary to distinguish between conversion and modulation in this context. Conversion means the processing of an analogue signal into a set of digital signals, and modulation means the change from the original digital signal into a type of digital signal that can be stored or transmitted by an error-free method. The two are, however, bound up with each other because many forms of conversion are also forms of modulation. The more modern methods of analogue to digital conversion are mainly based on a modulation system called pulse code modulation, in which the digital pulses represent in binary or other coded form the amplitude of a sample of the analogue signal. This has replaced older methods based on pulse amplitude or frequency, because its output is a stream of digital numbers that can be processed using familiar computing techniques.

The first point to settle about an AD conversion is how many bits should be used for a number. The use of eight bits permits the system to distinguish 256 different amplitude levels, and this may be quite sufficient for many applications – the fewer the number of bits in the conversion, the faster and more easily the signals can be handled. Much depends on the range of signal amplitudes that need to be coded. If, for example, the signal amplitude range is 90 dB, this corresponds to a signal amplitude range of about 32 000 : 1. Using just 256 steps of signal amplitude would make the size of each step about 123 units, too much of a change. This size of step is sometimes referred to as the quantum, and the process as quantization. In these terms, the use of 256 steps is too coarse a quantization for such an amplitude range. If we move to the use of 16 bits, allowing 32 767 steps, we can see that this allows a number of steps that is well matched to the amplitude range of 90 dB or 32 000:1. This is the level of quantization that is used in CD systems.

The choice of the number of bits has wider implications, however. Ideally, the amplitude of a signal at each sample would be proportional to a number in the 16-bit range. Inevitably, this will not be exact, and the difference between the actual amplitude and the amplitude that we can encode as a 16-bit number (or whatever is used) represents an error, the quantization noise. The greater the number of bits that are used to encode an amplitude, the lower the quantization noise will be. What is less obvious is the effect on low-amplitude signals. For low-amplitude signals, the amount of quantization noise is virtually proportional to the amplitude of signal, so that when the digital signal is re-converted to analogue the low-amplitude signals appear to be distorted.

The greater the number of digital bits used for encoding, the worse this effect gets, and the cure, by a strange paradox, is to add noise. Adding white noise – noise whose amplitude range is fairly constant over a large frequency range – to very low-amplitude signals helps to break the connection between the quantization noise and the signal amplitude and so greatly reduces the effects that sound so like distortion. This added noise is called dither, and is another very important part of a conversion process for signals with a wide range of amplitude. For many A-D conversions of industrial significance such refinements will be completely unnecessary. The noise level is very low, corresponding to a one-digit number.

SAMPLING RATE

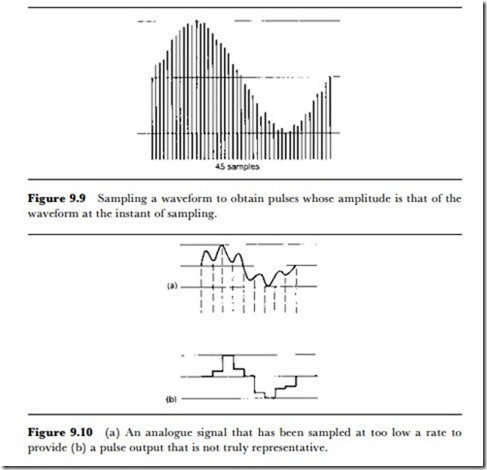

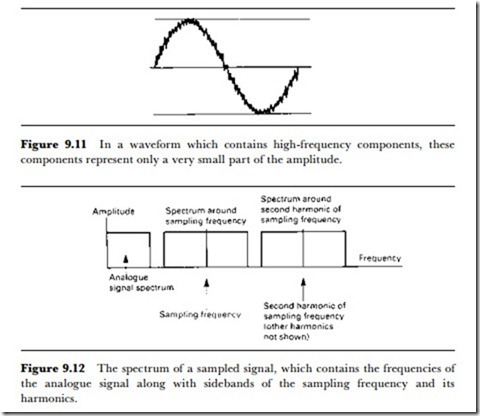

All A-D conversion starts with sampling. Sampling means that the amplitude of the audio analogue signal is measured and stored in a short interval of time, and if sampling is to be used as a part of the process of converting from analogue to digital signals, it has to be repeated at regular intervals. The principles of the process are illustrated in Figure 9.9, from which you can see that if an analogue waveform is to be converted into a digital form with any degree of fidelity, a large number of samples must be taken in the course of one cycle. If too few samples are taken, the digital

version of the signal (Figure 9.10) will look quite unlike the analogue version. On the other hand, if too many samples are taken per cycle, the system will be working with a lot of redundant information, wasting processing time and memory space. Whatever sampling rate is used must be a reasonable compromise between efficiency and precision and, as it happens, the theory of sampling is by no means new.

In 1948, C. E. Shannon published his classic paper A mathematical theory of communications on which the whole of digital conversion is based. The essence of Shannon’s work is that if the sampling rate is twice the highest frequency component in an audio signal, the balance between precision and excessive bandwidth is correctly struck. Note that this pivots around the highest frequency component in a mixture of frequencies – it does not imply that for a 1 kHz sine wave a sampling rate of 2 kHz would be adequate unless your reverse conversion was arranged always to regenerate a sine wave output. What Shannon’s theory is about is non-sinusoidal waves which can be analysed into a fundamental frequency and a set of

harmonics. What this boils down to is that if we look ata typical waveshape (Figure 9.11), the highest frequency component is responsible for a small part of the waveform, whose shape looks nothing like a sine wave and which could equally well be represented by a sawtooth.

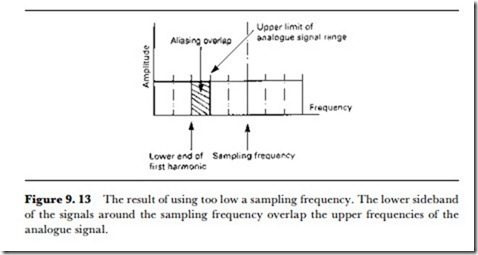

Sampling the highest harmonic, then, at twice the frequency of that harmonic will provide a good digital representation of the overall shape of the complete wave, all other things being equal. Sampling under these con- ditions provides a set of pulses whose amplitude is proportional to the amplitude of the wave at each sampled point. A spectrum analyser will then reveal something like the illustration of Figure 9.12. This consists of the range of frequencies that were present in the analogue signal (the funda- mentals) plus a set of harmonics centred around the sampling frequency and its harmonics. This is not a problem when the pulse amplitudes are being converted into digital form, but when the pulses are recovered a filter will be needed to separate out the wanted part, which is the lowest range of frequencies – the frequencies of the original signal.

The existence of these harmonics makes it important to ensure that the sampling rate is high enough. If the analogue signal had an 18 kHz bandwidth and a sampling rate of 30 kHz were used, the harmonics

around the 30 kHz sampling frequency would extend down to 30 – 18 = 12 kHz and up to 30 + 18 = 48 kHz, but the lower sideband of this set will overlap the 18 kHz of the original sound (Figure 9.13). This is an effect called aliasing, meaning that over a range of frequencies in the original range there will be a set of ‘aliases’ from the lower sidebands of the sampling frequency.

Even if the sampling frequency is made twice the highest audio frequency, difficulties still arise because there may be harmonics in the audio signal that extend to higher than half of the sampling frequency. This can be dealt with by using an anti-aliasing filter that is a steep-cut filter that will remove frequencies above the upper limit of the audio range. If the sampling frequency were too low, this filter would need to have an impossibly perfect performance. The sampling frequency must therefore be high enough to permit an effective anti-aliasing filter to be constructed. As before, such methods are needed only for signals whose amplitude and frequency ranges are large, such as audio signals, and in many instrumentation systems, using signals at DC or low-frequency AC, such methods are unnecessary.

SAMPLING AND CONVERSION METHODS

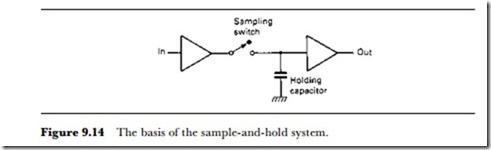

The process of sampling involves the use of a sample-and-hold circuit. As the name suggests, this is a circuit in which the amplitude of a waveform is sampled and held in memory while the amplitude size can be converted into digital form. The outline of a sample-and-hold circuit is shown in Figure 9.14, with a capacitor representing the holding part of the process. While the switch is closed, the voltage across the capacitor is the analogue

voltage, maintained by the buffer amplifier that has a low output impedance. No conversion into digital form takes place in this interval.

When the switch is opened, the amplitude of the analogue signal at the instant of opening is the voltage across the capacitor, and this amplitude controls the output of the second buffer stage. This, in turn, is the signal that will be converted to digital form. The instant of sampling can be very short, but the time that is available for conversion to digital form is the time between sampling pulses. The ‘switch’ that is shown will invariably be a semiconductor switch, and the capacitor can be a semiconductor memory, although for a fast sampling rate a capacitor is perfectly accept- able when its only loading is the input impedance of a MOS buffer stage.

The effect of sampling is only to quantize the signal. The signal is still an analogue signal in which the variation of amplitude with time carries the information of the signal, and the change that has come about as a result of sampling is the substitution of a set of pulses for the original varying signal. The signal is now an amplitude-modulated set of pulses at the sampling frequency, but this is not a digital signal. The actual conversion from analogue to digital form is the crucial part of the whole encoding process. There is more than one method of achieving this conversion, and not all methods are equally applicable to all uses. There are two main methods and the following is an outline of the problems that each of them presents.

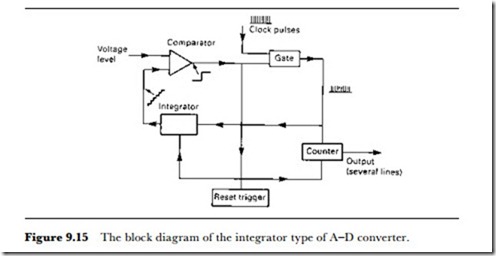

The integrator type of A-D converter is used widely in digital voltmeters. The principle is simple enough (Figure 9.15). The central part of the circuit is a comparator, which has two inputs and one output. While one input remains below the level of the other, the output remains at one logic level, but the logic level at the output switches over when the input levels are reversed. The change at the inputs that is needed to achieve this can be very small, a matter of millivolts, so that the action is that the output switches over when the input levels are equal. If one input is the signal being converted, this signal will be held at a steady level (by the sample- and-hold circuit) during the time that is needed for the conversion. A series of clock pulses are applied both to a counter and to an integrating circuit. The output of the integrating circuit is a series of equal steps of voltage, rising by one step at each clock pulse, and this waveform is applied to the other input of the comparator.

When the two inputs are at the same level (or the step waveform input just exceeds the sample input), the comparator switches over and this switch-over action can be used to interrupt the clock pulses, leaving the counter storing the number of pulses that arrived. Suppose, for example, that the steps of voltage were 1 mV, and that the sample voltage was 3.145 V. With the output of the integrator rising by 1 mV in each step, 3145 steps would be needed to achieve equality and so stop the count, and the count would be of the number 3145 in digital form, a digital number that represents the amplitude of the voltage at the sampled input. The switch-over of the comparator can be used to store this number into a register as well as stopping the clock pulses. A master clock pulse can then reset the integrator output to zero and terminate the conversion ready to start again when a new sample has been taken.

These numbers are, of course, for illustrative purposes only, but they demonstrate well how a signal level can be converted into a digital number by this method. Note that even with this comparatively crude example, the number of steps is well in excess of the 256 that would be available using an 8-bit digital number. Note also that the time that is needed to achieve the conversion depends on how fast a count rate is used. This will obviously need to be much faster than the sampling rate, since the conversion of each pulse should be completed by the time the next pulse is sampled. The quality of conversion by this method depends very heavily on how well the integrator performs. An integrator is a form of digital to analogue (D-A) converter, so that this presents the paradox of using a D-A converter as an essential part of the A-D conversion process, rather like the problem of the chicken and the egg. The very simple forms of integrator, like charging a capacitor through a resistor, are unsuitable because their linearity is not good enough. The height of each step must be equal, and in a capacitor charging system the height of each step is less than that of the

step previous to it. The integrator is therefore very often a full-blown D-A converter in integrated form.

For low-frequency analogue signals there are few problems attached to this method, but for wide ranges of amplitude and frequency the circuits may not be able to cope with the speed that will have to be used. This speed value depends on the time that is available between samples and the number of steps in the conversion. For example, if a time of 20 f.s is available to deal with a maximum level of 65 536 steps, then the clock rate

for the step pulses must be:

which gives a frequency of 3.8 GHz (not MHz), well above the limits of conventional digital equipment. This makes the simple form of integrator conversion impossible for the high sampling rates and large numbers of bits, such as are used for audio signals. Many of the recent advances in D-A and A-D conversion are due to the research that has been triggered by the use of CD technology and digital tape equipment.

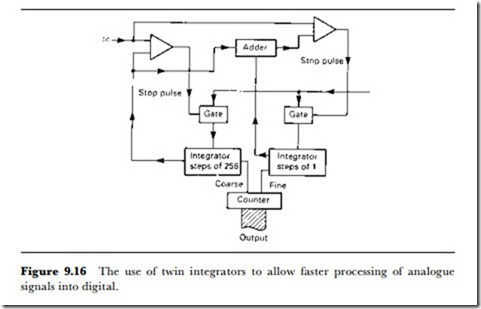

One solution, retaining the integrator type of converter, is to split the action between two converters, each working with part of the voltage. The idea here is that one counter works in the range 0-255, and the other in units that are 256 times the steps of the first. The voltage is therefore measured as two 8-bit numbers, each of which requires only 255 steps, so that the counting rate can be considerably lower. Since the counters work in succession, with the smaller range of counter operating only after the coarser step counter has finished (Figure 9.16), the total number of steps is 2 x 255 = 510, and the step rate is now, still assuming a 20 f.s time interval:

– a rate of 25.5 MHz. This is well within the range of modern digital circuitry in IC form.

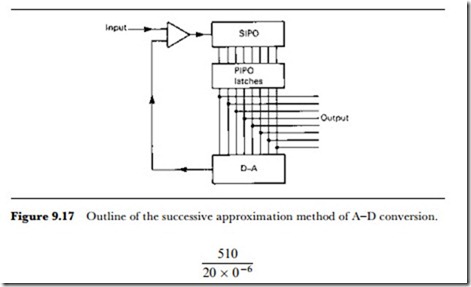

Another form of A-D converter is known as the successive approximation type. The outline of the method is shown in Figure 9.17, consisting of a serial input parallel output (SIPO) register, a set of latches or PIPO register, a D-A converter and a comparator whose output is used to operate the register. To understand the action, imagine that the output from the D-A converter is zero and therefore less than the input signal at the time of the sample. The resultant of these two inputs to the comparator is to make the output of the comparator high, and the first clock pulse arriving at the SIPO register will switch on the first flip-flop of the PIPO register, making its output high to match the high input from the compara- tor. This first PIPO output is connected to the highest bit input of the D-A converter, which for a 16-bit register corresponds to 32 767 steps of amplitude.

Now what happens next depends on whether the input signal level is more than or less than the level of output from the D-A converter for this input number. If the input signal is less than this, the output of the comparator changes to zero, and this will in turn make the output of the SIPO register zero and the output of the PIPO register zero for this bit. If the input signal is greater than the output from the D-A circuit, the 1 bit remains in the first place of the register. The clock pulse will then pass this pulse down to the next PIPO input – this does not, however, affect the first PIPO input which will remain set at the level it had attained.

Another comparison is now made, this time between the input signal and the output of the D-A converter with another input bit. The D-A output will be either greater than or less than the input signal level, and as a result, the second bit in the PIPO register will be set to 1 or reset to 0. This second bit represents 16 384 steps if its level is 1, zero if its level is 0. The process is repeated for all 16 stages in the register until the digital number that is connected from the PIPO outputs to the D-A inputs makes the output of the D-A circuit equal to the level of the input signal. Using this method, only 16 comparisons have to be made in the sampling period, giving a maximum time of 1.25 f.s for each operation. This time, however, includes the time needed for shifting bits along the registers, and it requires a fast performance from the D-A converter, faster than is easily obtained from most designs. Speed is the problem with most digital circuits, which is why there is a constant effort made to improve methods of manufacturing ICs, even to the use of alternative semiconductor materials (such as gallium arsenide) that could allow faster operation.