ON-CHIP MEMORY

Context

● You are developing an embedded application using one or more members of the 8051 family of microcontrollers.

● You are designing an appropriate hardware foundation for your application.

Problem

How do you create an 8051-based circuit that uses only internal memory?

Background

Some general background material on memory is presented in this section.

Direct vs. indirect addressing

You will often see the terms ‘indirect addressing’ and ‘direct addressing’ used in discussions about microcontroller memory. Although these terms often cause confusion, they are not difficult to understand.

You will recall that whatever language you write in (for example, C or assembly), your code must ultimately be translated into machine code instructions that can be executed by your chosen microcontroller. This set of possible machine instructions is defined by the hardware manufacturer. Through this process, even complex state- ments in a high-level language are eventually broken down into basic operations, such as ‘Copy this piece of data from one memory location to another’. These, in turn, are implemented by machine instructions that take the form ‘Move the con- tents of memory address X to register Y’.

There are essentially two ways in which such fundamental ‘Move’ instructions may be implemented in microcontrollers and microprocessors:

● Using direct addressing, the address of the memory location (that is, memory address X in the last example) is specifically given as part of the instruction.

● Using indirect addressing, the address of the memory location is not explicitly included as part of the instruction: instead the address (of another memory location or another register) that contains memory address X is included in the instruction.

Since the use of indirect addressing means that two steps are required to find the address of the required memory location it may appear to be slower than direct addressing. However, universal use of direct addressing in an 8-bit architecture (with a 16-bit address space) would mean that all ‘Move’ instructions would need to include two bytes of address information, and would therefore take more time to fetch from memory. A compromise is thus often made in devices (including the 8051) where a small area of memory can be directly addressed and most other memory areas must be indirectly addressed.

Note that the distinction between direct and indirect addressing also has other uses. For example, within members of the 8051 family, there is an area of ‘special function register’ memory and another area of general purpose memory. Both blocks of memory are the same size (128 bytes) and both blocks share the same address range. On the surface, having two areas of memory with the same address makes no sense; however, in this case, there is no problem. One block of memory can only be accessed indirectly, the other block can only be accessed directly. As a result, when our compiler translates a particular ‘C’ statement, appropriate machine-level instruc- tions are selected to ensure that the correct memory area is accessed: in most circumstances, this process is completely hidden from the programmer.

Types of memory

On the desktop, most designers and programmers can safely ignore the type of memory they are using. This is seldom the case in embedded environments and we therefore briefly review some of the different types of memory.

First, a short history lesson, to explain the roots of an important acronym. On early mainframe and desktop computer systems, long-term data storage was carried out using computer tapes. Reading or writing to the tape took varying amounts of time, depending whether it involved, for example, rewinding the entire tape or simply rewinding a couple of centimetres. In this context, new memory devices appeared that could be used to store data while the computer was running, but which lost these data when the power was removed. These read-write memory devices were referred to as ‘random access memory’ (RAM) devices, because – unlike tape-based systems – access- ing any element of memory ‘chosen at random’ took the same amount of time.

Tapes have now largely disappeared, but the acronym RAM has not and is still used to refer to memory devices that can be both read from and written to. However, since RAM was first introduced, new forms of memory devices have appeared, including various forms of ROM (read-only memory). Since these ROM devices are also ‘random access’ in nature, the acronym RAM is now best translated as ‘read-write memory’.

Dynamic RAM (DRAM)

Dynamic RAM is a read-write memory technology that uses a small capacitor to store information. As the capacitor will discharge quite rapidly, it must be frequently refreshed to maintain the required information: circuitry on the chip takes care of this refresh activity. Like most current forms of RAM, the information is lost when power is removed from the chip.

In general, dynamic RAM is simple and comparatively cheap.

Static RAM (SRAM)

Static RAM is a read-write memory technology that uses a form of electronic flip-flop to store the information. No refreshing is required, but the circuitry is more complex and costs can be several times that of the corresponding size of DRAM. However, access times may be a third those of DRAM.

Mask read-only memory (ROM)

A true read-only memory (ROM) would be useless. The most basic kind of practical ROM is, from the designer’s perspective, read only: however, the manufacturer is able to write to the memory, at the time the chip is manufactured, according to a ‘mask’ provided by the company for which the chips are being produced. Such devices are therefore some- times referred to as ‘factory-programmed ROM’ or ‘mask ROM’. Factory or mask programming is not cheap and is not a low-volume option: as a result, mistakes can be very expensive and providing code for your first mask can be a character-building process. Access times are often slower than RAM: roughly 1.5 times that of DRAM.

It should be noted that mask ROMs retain their contents even in environments with high levels of electromagnetic activity. This behaviour is in contrast to some of the erasable devices in which there is a risk that data corruption may occur due, for example, to high UV levels (UV–EPROMs: see later in this section) or strong electrical fields (EEPROMs: see later in this section).

Many members of the 8051 family are available with on-board mask-programmable ROM.

Programmable read-only memory (PROM)

The name PROM sounds like a contradiction and it is. This is, in fact, a form of write- once, read-many (WORM) or ‘one-time programmable’ (OTP) memory. Basically, we use a PROM programmer to blow tiny ‘fuses’ in the device. Once blown, these fuses cannot be repaired; however, the devices themselves are cheap.

Many modern members of the 8051 family are available with OTP ROM.

UV-erasable programmable read-only memory (UV-EPROM)

Like PROMs, UV-EPROMs are programmed electrically. Unlike PROMs, they also have a quartz window which allows the memory to be erased by exposing the internals of the device to UV light. The erasure process can take several minutes and, after erasure, the quartz window will be covered with a UV-opaque label. This form of EPROM can withstand thousands of program / erase cycles.

More flexible than PROMs and once very common, UV-EPROMs now seem rather primitive compared with EEPROMs. They can be useful for prototyping but are pro- hibitively expensive for use in production.

Many older members of the 8051 family are available with on-board UV-EPROM.

Electrically erasable programmable read-only memory (EEPROM, E2PROM)

EEPROMs are a more user-friendly form of EPROM that can be both programmed and erased electrically. This does not mean they can simply be used in place of RAM for all purposes, not least because writing to the EEPROM is a very slow process and there is a limit to the number of write operations that may be performed.

Many members of the 8051 family are available with on-board EEPROM.

Flash ROM

Flash ROM is not only a relief from increasingly long and irrelevent acronyms, it is also the most civilized form of ROM currently available. As the name suggests, it can usually be programmed much more rapidly than an EEPROM. In addition, while many EEPROMs often require high (12V) programming voltages, Flash ROM devices can usually be programmed at standard (3V/5V) levels.

Members of the 8051 family are now available with on-board flash ROM.

Solution

The memory map of the 8051 family is illustrated in Figure 6.1.

In order to make best use of the internal memory, or to select an appropriate device for your application, you need to understand the meaning of the different memory areas. These are now discussed.

The CODE area

As the name suggests, the main rôle that CODE memory plays in your 8051 application is to store the program (executable) code. This happens automatically with all C compilers. Note that the code is executed ‘in place’ in ROM: it is not copied to RAM for execution.

In addition to code, it can be useful to store (read-only) data, such as lookup tables, in the CODE area. This is often an excellent idea: many 8051 devices have compara- tively large amounts of ROM available (64 kbytes is no longer uncommon), but only small amounts of available RAM (usually no more than 4 kbytes; frequently no more than 256 bytes). Placing read-only data in ROM when possible usually makes good sense.

Using ROM for data tables can also make sense on performance grounds. For exam- ple, if your code requires calculation of sines or cosines, this can require a large number of CPU operations on most systems (typically more than 3000 CPU oper- ations). If you are able to include the relevant results in an array (lookup table), this can reduce the CPU load by a factor of around 1,000.

Placing data in ROM is easy to do. For example, using the Keil C51 compiler and the code keyword, we can store a large array in ROM as follows:

The DATA, BDATA and IDATA areas

Up to 256 bytes of internal data memory are available depending on the particular 8051 device that is used. Access to internal data memory is generally very fast because it can be carried out using an 8-bit address.

The internal data area is split into three overlapping areas: DATA, IDATA and BDATA. We now discuss each of these areas.

Using the DATA area

The DATA area refers to the first 128 bytes of internal data memory. Variables stored here are accessed very quickly using direct addressing.

Using the DATA area is the default with the C51 compiler, if – as recommended by Keil – the small memory model is used. Alternatively, the data keyword may be used to explicitly specify that a variable should be stored in the DATA area. For example:

char data Input1;

unsigned int data Loop_Control;

Using the IDATA area

The IDATA area refers to all 256 bytes of internal data memory (including the 128 bytes of the data area, with which it overlaps). Variables stored here are accessed less rapidly than DATA variables, using indirect addressing. The idata keyword may be used to explicitly state that variables are to be stored in the IDATA area, as follows:

char idata Input2;

unsigned int idata Loop_Control2;

Note, however, that the IDATA area is usually most useful as a stack area: in general, it is better to leave this area free for use by the compiler.

Using the BDATA area

The BDATA area overlaps with the DATA area. Specifically, it refers to 16 bytes of bit- addressable memory in the internal DATA area (addresses 0x0020 to 0x002F).

Use of the bit, bdata and sbit keywords allows you to make use of this area and to declare data types that can be accessed at the bit level. Consider the following examples:

As shown in Figure 6.1, all 8051s provide up to 128 bytes of memory for special func- tion registers (SFRs). SFRs are bit, byte or word-size (2-byte) registers that are used to control timers, counters, serial I/O, port I/O and various peripherals. The port SFRs are discussed in the pattern PORT I / O [page 162].

Note that – as briefly mentioned in ‘Background’ – the IDATA locations 128 to 255 and the SFR area share the same address space. However, memory locations in these two areas are accessed using different addressing modes. IDATA locations 128 to 255 are only indirectly addressable and the special function registers are only directly addressable.

External data memory

There may be up to 64 kbytes of external data memory. Compared to the internal memory areas, access to external memory is slow.

The external data memory can be divided into two areas. The XDATA area refers to any location within the (64-kbyte) data address space. The PDATA area represents the first 256 bytes of this address space. If programmed appropriately, access to PDATA variables is faster than access to those in the rest of the external data space.

Internal ‘external’ memory

Although it is mapped into the XDATA area, it should be noted that not all XDATA memory need be physically located outside the microcontroller. In fact, many modern devices include on-chip XDATA RAM. For example, the Dallas 83C520 includes 1 kbyte of such ‘XRAM’, while the Infineon C509 includes 3 kbytes of XRAM. These areas of RAM are used in the same way as external memory, as we dis- cuss in the section ‘Controlling access to internal and external memory’ below.

Avoiding confusion between the various CODE and DATA areas

Note that many 8-bit microcontrollers have a single (64K) memory area, shared by code and data. In the case of the 8051, we have up to 64 kbytes of code and 64 kbytes of data available. Because both of these areas share the same address space, the chip (and compiler) need a means of accessing the correct area.

The main way of distinguishing between code and data access is using the /RD, /WR and /PSEN pins. The /RD and /WR pins are used only when accessing (external) data memory, while the /PSEN pin is used only when accessing (external) code memory.

As with direct and indirect addressing, this process is generally hidden from the programmer working in a high-level language.

Most members of the 8051 family operate in one of two modes determined at reset by the state of the ‘external access’ (/EA) pin. If /EA is held low, on-chip instruction (but not data) memory is disabled and the entire 64KB of instruction space is accessed externally. If /EA is held high, on-chip instruction memory is enabled. In these circumstances, external access to (code) memory will only occur if the pro- gram attempts to access an address beyond the range of the on-chip memory.

Forgetting to pull the /EA pin high is a very common error in single-chip designs created by developers new to the 8051 family.

Controlling access to internal and external memory

Note that, unlike CODE memory, the state of the /EA pin at reset does not affect on- chip data RAM which is always enabled and accessible. Another difference is related to the way the presence of on-chip RAM affects the external data memory space. For CPUs with up to 256 bytes of on-chip (IDATA) RAM, the full 64KB external data space is also available. Where devices have on-chip XDATA memory, this will overlap with any external memory. Note that the address at which any on-chip XDATA memory is mapped into the address space varies between devices. Most chips map this memory at address 0x00, but some use different values.

Note that these comments do not apply to the Small 8051 devices, which do not support external memory and, therefore, do not require an /EA pin. In addition, some members of the 8051 family (notably the 8031 and derivatives, and some Extended 8051s) have no on-chip ROM, so always require the use of external (CODE) memory.

Different internal memory available on different 8051 devices Examples of the various memory components on a range of 8051 devices is given in Table 6.1.

Hardware resource implications

On-chip memory is a net provider of hardware (memory) resources.

Reliability and safety implications

Suppose that we have two identical applications, using (almost) identical software, but one using internal memory (only), and one using external memory (for code and/or data). Everything else being equal, it is likely that the ‘internal’ application will prove more reliable. This is partly because the use of internal memory reduces the opportunities for wiring or design errors, partly because of the reduction in external wires (‘aerials’) makes the system less vulnerable to EMI, and partly because (in the external version) each of the soldered joints has a risk of failure in the presence of vibration and/or high humidity.

In addition, the ALE pin can be a source of EMI. This pin is required for external memory access but its operation can (in some devices) be disabled, if internal memory is being used. This can reduce the likelihood that your application will induce an error in some other part of the application.

As (in almost all cases) the ‘internal’ solution will also be both cheaper to produce and physically smaller, the message is clear: use internal memory if at all possible.

Portability

In general, the most portable 8051 code assumes only the presence of a small amount of CODE memory (some kind of ROM, say 4 kbytes) and 128 bytes of RAM. This combination is available even in most of the smallest 8051s.

Further memory (typically 256 bytes of RAM) will be available in many modern 8051s. Some modern devices also have on-chip XRAM. However, the more of these facilities you use, the less easy it will be to port your code to another microcontroller in the 8051 family.

Overall strengths and weaknesses

Use of internal memory (in place of external memory) can have the following implications:

Lower application cost. Increased hardware reliability.

Reduced EM emissions (where you are able to disable ALE activity).

In most cases, the available data memory will be restricted.

Related patterns and alternative solutions

See OFF – CHIP DA T A MEMOR Y [page 94] and OFF – CHIP CODE MEMOR Y [page 100].

Example: Internal memory on the Philips 8XC552

As an example of the memory options available, we will consider the Philips 8XC552.

The 8XC552 contains 8 kbytes of on-chip program memory which can be extended to 64 kbytes through the use of external memory. When the EA pin is held high, the 8XC552 fetches instructions from internal ROM unless the address exceeds 1FFFH. Locations 2000H to FFFFH are fetched from external program memory. When the EA pin is held low, all instruction fetches are from external memory. ROM loca- tions 0003H to 0073H are used by interrupt service routines.

The internal data memory is divided into three sections: the lower 128 bytes of RAM, the upper 128 bytes of RAM and the 128-byte special function register areas. The lower 128 bytes of RAM are directly and indirectly addressable. While RAM loca- tions 128 to 255 and the special function register area share the same address space, they are accessed through different addressing modes. RAM locations 128 to 255 are only indirectly addressable and the special function registers are only directly address- able. All other aspects of the internal RAM are identical to the 8051. The stack may be located anywhere in the internal RAM by loading the 8-bit stack pointer. Stack depth is 256 bytes maximum.

The special function registers (directly addressable only) contain all the 8XC552 registers except the program counter and the four register banks. Most of the 56 spe- cial function registers are used to control the on-chip peripheral hardware. Other registers include arithmetic registers (ACC, B, PSW), stack pointer (SP) and data pointer registers (DHP, DPL). Sixteen of the SFRs contain 128 directly addressable bit locations.

Example: Comparing speed of access to different memory areas

Typical access times for data stored in the various memory areas (measured in instruc- tion cycles) are as follows:

● Access to DATA area takes one cycle [direct access]

● Access to IDATA area takes two cycles

[8-bit copy of address to register (1 cycle), then 1-cycle move]

● Access to PDATA area takes three cycles

[8-bit copy of address to register (1 cycle), then 2-cycle move instruction]

● Access to XDATA area takes four cycles

[16-bit copy of address to register (2 cycles), 2-cycle move instruction]

● Access to CODE area takes four cycles

[16-bit copy of address to register (2 cycles), 2-cycle move instruction]

Although these figures are typical, it is difficult to predict precisely how access times to variables in different memory areas will compare, partly because the results vary depending on different compiler options used.

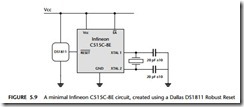

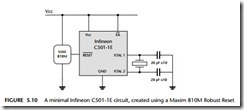

Example: Making use of internal XRAM memory on the Infineon C515C

The Infineon C515C is a powerful (extended) 8051 device that we have used in a range of different applications, particularly because of its good performance and on- chip CAN component.

In addition to the standard (256 bytes) of IDATA RAM, the C515C has 2 kbytes of on-chip XRAM.

To use this memory, you need to be aware that (unlike the Dallas 520, for exam- ple), this memory is not mapped from address 0×0000. Instead, the starting address of this memory is 0xF800.

If you are using the Keil compiler, you need to provide this information to the linker, via the ‘Size / Location’ menu item. You should enter the address (start of XDATA) as ‘0F800’: omitting the initial ‘0’ causes problems with current versions of the compiler.