File Register Set

All the file registers are 8 bits wide. They are divided into two main blocks: the special function registers (SFRs), which are reserved for specific purposes, and the general purpose registers (GPRs), which can be used for temporary storage of any data byte. The basic file register set (16F84A) is shown in Figure 5.2.

The registers in Bank 0 (file addresses 00e4F) can be directly addressed, and it is suggested that the register labels given in Figure 5.2, which match the data sheet, are used

as the register labels. These labels are also used by default in MPLAB, and standard header files can be included in your programs, which define all the register names using these labels.

Special instructions are available to access the Bank 1 registers. For simplicity, we have already used the instruction TRIS to access the data direction registers TRISA and TRISB. Similarly, we will use the instruction OPTION to access the option register, which will be used later to set up the hardware timer. Alternatively, a register bank select bit in the status register can be used to access Bank 1 file registers. This operation is most easily implemented by using a special instruction BANKSEL (see Program 1.1); this is the preferred method once the basics of programming have been established.

Special Function Registers

The operation of the 16F84A SFRs is summarized below, describing the operation of those that are used most frequently. The functions of all the registers are detailed in each chip data sheet. The shaded registers in Figure 5.2 either do not exist, or are repeated at addresses 80eCF (page 1).

PCL Program Counter Low Byte File Register Number ¼ 02

The program counter contains the address of (points to) the instruction currently being executed, and counts from 000 to 3FF, unless there is a jump (GOTO or CALL). The PCL register contains only the low 8 bits (00eFF) of the whole program counter, with the high stored in the PCLATH register (address 0A). We only need to worry about the high bits if the program is longer than 255 instructions in total, which is not the case for any of the demonstration programs, and then only if the program counter is being modified directly. The PC is automatically incremented during the instruction execution cycle, or the contents replaced for a jump.

PORTA Port A Data Register

File Register Number ¼ 05

Port A has five I/O bits, RA0eRA4. Before use, the data direction for each pin must be set up by loading the TRISA register with a data direction code (see below). If a bit is set to output, data moved to this register appears at the output pins of the chip. If set as input, data presented to the pins can be acted on immediately, or stored for later use by moving the data to a spare register. Examples of this have already been seen in earlier chapters. In the 16F84A, RA4 can alternatively be used as an input to the counter timer register (TMR0) for counting applications. The use of the hardware timer will be covered in Chapter 6. The PORTA register bit allocation is shown in Table 5.1. In other PIC chips, most port pins will have at least two different functions, selected by setting up the relevant SFRs.

All registers are read and written as an 8-bit word, so we sometimes need to know what will happen with unused bits. When the port A data register is read within a program (using MOVF), the 3 unused bits will be seen as ‘0’. When writing to the port, the high 3 bits are simply ignored. An equivalent circuit for each port pin is given in the 16F84A data sheet, Section 5. The components of this block diagram are explained in Appendix B.

TRISA Port A Data Direction Register File Register Number ¼ 85 The data direction of the port pins can be set bit by bit by loading this register with a suitable binary code, or the hex equivalent. A ‘1’ sets the corresponding port bit to input, while a ‘0’ sets it to output. Thus, to select all bits as inputs, the data direction code is 1111 1111 (FFh), and for all outputs is 0000 0000 (00h). Any combination of inputs and outputs can be set by loading the TRIS register with the appropriate binary code.

When the chip first is powered up, these bits default to ‘1’, so it is not necessary to initialize for input, only for output. This makes sense, because if the pin is incorrectly wired up, it is more

easily damaged if set to output. For instance, if the pin is accidentally grounded, and then driven to a high state by the program, the short-circuit current is likely to damage the output circuit. If the pin is set as an input, no damage will be done.

The data direction register TRISA is loaded by placing the required code in W and then using the instruction TRIS 05 or TRIS 06 for port A and port B, respectively. Alternatively, all file registers with addresses 80eCF can be addressed directly, using the BANKSEL command, and this option will be used in later programs.

PORTB Port B Data Register

File Register Number ¼ 06

Port B has the full set of eight I/O bits, RB0eRB7. If a bit is set to output, data moved to this register appears at the output pins of the chip. If set as input, data presented to the pins can be read at this address. The data direction is set in TRISB, using the TRIS or BANKSEL command, and all bits default to input on power up. The PORTB register bit allocation is shown in Table 5.1.

Bit 0 of port B has an alternative function; it can be initialized, using the interrupt control register (INTCON), to allow the processor to respond to a change at this input with an interrupt sequence. In this case, the processor is forced to jump to a predefined interrupt service routine

(ISR) upon completion of the current instruction (see Section 6.3). The processor can also be initialized to provide the same response to a change on any of the bits RB4eRB7.

TRISB Port B Data Direction Register File Register Number ¼ 86 As in port A, the data direction can be set bit by bit by loading this register with a suitable binary code, or the hex equivalent, where ‘1’ (default) sets an input and ‘0’ sets an output (initialization required). The command TRIS 06 moves the data direction code from W to TRISB register; the command BANKSEL allows direct access to bank 1 and the data direction registers.

STATUS Status (or Flag) register File Register Number ¼ 03

Individual bits in the status register record information about the result of the previous instruction. Probably the most commonly used is the zero flag, bit 2; when the result of any operation is zero, this zero flag bit is set to ‘1’. It is used by the Decrement/Increment and Skip if Zero instructions, and can be used by the Bit Test & Skip instructions, to implement conditional branching of the program flow. The status register bit functions are shown in Table 5.2, where the function of the other bits is indicated.

TMR0 Timer Zero Register

File Register Number ¼ 01

A timer/counter register counts the number of pulses applied to a clock input; the binary count can be read from the register when the count is finished. TMR0, an 8-bit register, can count up to 255 pulses. For external inputs, the pulses are applied at pin RA4. When used as a timer, the internal instruction clock is used to supply the pulses. If the processor clock frequency is

Table 5.3: OPTION register bit functions

Bit Label Name Function

0 PS0 Prescaler Rate Select Bit 0 3-bit code to select one of eight prescale values

1 PS1 Prescaler Rate Select Bit 1

2 PS2 Prescaler Rate Select Bit 2

3 PSA Prescaler Assignment Assigns prescaler to WTD or TMR0

4 T0SE Timer Zero Source Edge Select Select rising or falling edge trigger for T0CKI input at RA4

5 T0CS Timer Zero Clock Source Select Selects timer/counter input as RA4 or internal clock

6 INTEDG Interrupt Edge Select Selects rising or falling edge trigger for RB0 interrupt input

7 RBPU Port B Pull-up Enable Enables pull-ups on port B pins so input data defaults to ‘1’

known, the time taken to reach a given count can be calculated. When the counter rolls over from FF to 00, an interrupt flag (see INTCON below) is set, if enabled. This allows the processor to check if the count is complete, or to be alerted via an interrupt when a set time interval has elapsed. The timer register can be read and written directly, so a count can be started at a preset value to generate a known interval. The ‘Timer Zero’ label refers to the fact that other PICs have more than one timer/counter register, but the 16F84A has only the one. More details on using the TMR0 are given in Chapter 6.

OPTION Option Register

File Register Number ¼ 81

Table 5.3 details the option register bit functions. The TMRO counter/timer operation is controlled by bits 0e5. When used as a timer (T0CS ¼ 0), the processor instruction clock signal increments the counter register. Prescaling can be selected (PSA ¼ 0) to increase the maximum time interval. Bits PS2, PS1 and PS0 control the prescale factor, which can be set to divide the clock frequency by 2 (000), 4 (001), 8 (010), 16 (011), 32 (100), 64 (101), 128 (110) or 256 (111). If the O 256 option is selected, the maximum count will be (256 x 256) –

1 ¼ 65 535 cycles. As is the case with the TRISA and TRISB registers, the option register is accessed using a special instruction, OPTION, or by bank selection. There is more on using the timer in the next chapter. The option register is labeled OPTION_REG in more recent processors, to avoid confusion.

INTCON Interrupt Control Register File Register Number ¼ 0B

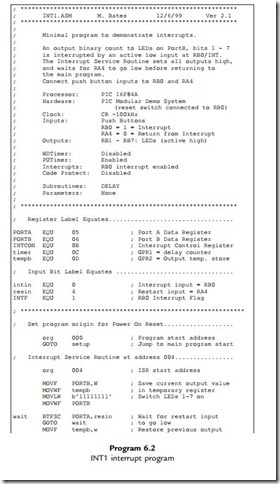

The INTCON bit functions are given in Table 5.4. An interrupt is a signal that causes the current program execution to be suspended, and an ISR carried out. An interrupt can be generated by an external device, via port B, or from the timer. In all cases, the ISR must start at address 004 in the program memory. If interrupts are in use, an unconditional jump from address zero, the program start address, to a higher start address, is needed. The INTCON register contains three interrupt flags and five interrupt enable bits, and these must be set up as

required during the program initialization by writing a suitable code to the INTCON register. Program 6.2 in Chapter 6 demonstrates the use of interrupts. The precise function of the INTCON bits varies in different PIC chips.

required during the program initialization by writing a suitable code to the INTCON register. Program 6.2 in Chapter 6 demonstrates the use of interrupts. The precise function of the INTCON bits varies in different PIC chips.

Other SFRs

More SFRs are listed in Table 5.5. EEDATA, EEADR, EECON1 and EECON2 are used to access the non-volatile ROM data area. PCLATH acts as a holding register for the high bits (12:8) of the program counter. The file select register (FSR) acts as a pointer to the file registers. It is used with IND0, which provides indirect access to the file register selected by FSR. This is useful for a block read or write to the GPRs, for example, for saving a set of data read in at a port at intervals. More information on this is given in Chapter 6, Section 6.4.3. Larger chips have more SFRs, which are required to control the additional peripheral blocks: timers, analogue converters, serial ports and so on. These will be described later.

General Purpose Registers

The GPRs are numbered 0Ce4F in the 16F84A, 68 in all, and larger chips have more. They are also referred to as random access memory (RAM) registers, because they can be used as a small block of static RAM for storing blocks of data. We have already seen an example of using the

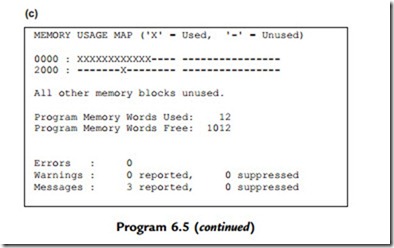

GPR1 (address 0C) as a counter register in a delay loop. The register was labeled ‘timer’, preloaded with a value and decremented until it reached zero. This is a common type of operation, and not only used for timing loops. For example, a counting loop can be used for repeating an output operation a certain number of times, such as when performing multiplication by successive addition. We could have used any of the GPRs for this function because they are all operationally identical. When using more than one, a different label is needed for each, declared using the EQU directive.

2. In the PIC 16F84A data sheet, Section 4.0, a block diagram of the internal circuit connected to pin RA0 is shown. Refer to Appendices B and C if necessary, and complete the tasks below. The FETs at the output form a complementary pair of switches, a P-type and an N-type. The PFET is on when its gate is low. The NFET is on when its gate is high. For the port pin to operate as an output, the TRIS latch is loaded with the data direction bit 0, and the data is loaded into the data latch from the internal data bus.

(a) Construct a logic table to represent the operation of the output logic when the TRIS latch is clear (Q ¼ 0), that is, the pin is set as an output. Prove that the output pin follows the latched output data.

(b) Extend the logic table and prove that P and N are both off when the pin is initialized for input.

(c) Describe how a data bit is read onto the data bus when the pin is set for input.

(d) What is the function of the output FETs in the operation of the I/O pin?