DIRECT MEMORY ACCESS AND DMA-CONTROLLED I/O

INTRODUCTION

In previous chapters, we discussed basic and interrupt-processed I/O. Now we turn to the final form of I/O called direct memory access (DMA). The DMA I/O technique provides direct access to the memory while the microprocessor is temporarily disabled. This allows data to be transferred between memory and the I/O device at a rate that is limited only by the speed of the memory components in the system or the DMA controller. The DMA transfer speed can approach 33 to 150 M-byte transfer rates with today’s high-speed RAM memory components.

DMA transfers are used for many purposes, but more common are DRAM refresh, video displays for refreshing the screen, and disk memory system reads and writes. The DMA transfer is also used to do high-speed memory-to-memory transfers.

This chapter also explains the operation of disk memory systems and video systems that are often DMA-processed. Disk memory includes floppy, fixed, and optical disk storage. Video systems include digital and analog monitors.

CHAPTER OBJECTIVES

Upon completion of this chapter, you will be able to:

1. Describe a DMA transfer.

2. Explain the operation of the HOLD and HLDA direct memory access control signals.

3. Explain the function of the 8237 DMA controller when used for DMA transfers.

4. Program the 8237 to accomplish DMA transfers.

5. Describe the disk standards found in personal computer systems.

6. Describe the various video interface standards that are found in the personal computer.

BASIC DMA OPERATION

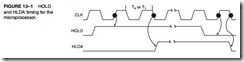

Two control signals are used to request and acknowledge a direct memory access (DMA) transfer in the microprocessor-based system. The HOLD pin is an input that is used to request a DMA action and the HLDA pin is an output that acknowledges the DMA action. Figure 13–1 shows the timing that is typically found on these two DMA control pins.

Whenever the HOLD input is placed at a logic 1 level, a DMA action (hold) is requested. The microprocessor responds, within a few clocks, by suspending the execution of the program and by placing its address, data, and control bus at their high-impedance states. The high-impedance state causes the microprocessor to appear as if it has been removed from its socket. This state allows external I/O devices or other microprocessors to gain access to the system buses so that memory can be accessed directly.

As the timing diagram indicates, HOLD is sampled in the middle of any clocking cycle. Thus, the hold can take effect any time during the operation of any instruction in the micro- processor’s instruction set. As soon as the microprocessor recognizes the hold, it stops executing software and enters hold cycles. Note that the HOLD input has a higher priority than the INTR or NMI interrupt inputs. Interrupts take effect at the end of an instruction, whereas a HOLD takes effect in the middle of an instruction. The only microprocessor pin that has a higher priority than a HOLD is the RESET pin. Note that the HOLD input may not be active during a RESET or the reset is not guaranteed.

The HLDA signal becomes active to indicate that the microprocessor has indeed placed its buses at their high-impedance state, as can be seen in the timing diagram. Note that there are a few clock cycles between the time that HOLD changes and until HLDA changes. The HLDA output is a signal to the external requesting device that the microprocessor has relinquished control of its memory and I/O space. You could call the HOLD input a DMA request input and the HLDA output a DMA grant signal.

Basic DMA Definitions

Direct memory accesses normally occur between an I/O device and memory without the use of the microprocessor. A DMA read transfers data from the memory to the I/O device. A DMA write transfers data from an I/O device to memory. In both operations, the memory and I/O are controlled simultaneously, which is why the system contains separate memory and I/O control signals. This special control bus structure of the microprocessor allows DMA transfers. A DMA read causes both the MRDC and IOWC signals to activate simultaneously, transferring data from the memory to the I/O device. A DMA write causes the MWTC and IORC signals to both acti- vate. These control bus signals are available to all microprocessors in the Intel family except the 8086/8088 system. The 8086/8088 require their generation with either a system controller or a circuit such as the one illustrated in Figure 13–2. The DMA controller provides the memory with its address and a signal from the controller (DACK) selects the I/O device during the DMA transfer.

The data transfer speed is determined by the speed of the memory device or a DMA controller that often controls DMA transfers. If the memory speed is 50 ns, DMA transfers occur at rates of up to 1/50 ns or 20 M bytes per second. If the DMA controller in a system functions at a maximum rate of 15 MHz and we still use 50 ns memory, the maximum transfer rate is 15 MHz because the DMA controller is slower than the memory. In many cases, the DMA controller slows the speed of the system when DMA transfers occur.

Because of the switch to serial data transfers in modern computer systems, DMA is becoming less important. The PCI Express bus, which is serial, transfers data at rates that exceed DMA transfers. Even the SATA (serial ATA) interface for disk drives uses serial transfers at the rate of 300 Mbps, which has replaced DMA transfers for hard disk drives. Serial transfers on main-boards (motherboards) between components that use serial techniques can approach 20 Gbps for the PCI Express connection.