SHARED-BUS OPERATION

Complex present-day computer systems have so many tasks to perform that some systems are using more than one microprocessor to accomplish the work. This is called a multiprocessing system. We also sometimes call this a distributed system. A system that performs more than one task is called a multitasking system. In systems that contain more than one microprocessor, some method of control must be developed and employed. In a distributed, multiprocessing, multitasking environment, each microprocessor accesses two buses: (1) the local bus and (2) the remote or shared bus.

This section of the text describes shared bus operation for the 8086 and 8088 microprocessors using the 8289 bus arbiter. The 80286 uses the 82289 bus arbiter and the 80386/80486 uses the 82389 bus arbiter. The Pentium–Pentium 4 directly support a multiuser environment, as described in Chapters 17, 18, and 19. These systems are much more complex and difficult to illustrate at this point in the text, but their terminology and operation is essentially the same as for the 8086/8088.

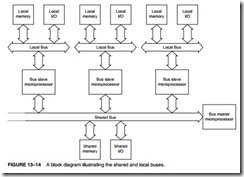

The local bus is connected to memory and I/O devices that are directly accessed by a single microprocessor without any special protocol or access rules. The remote (shared) bus contains memory and I/O that are accessed by any microprocessor in the system. Figure 13–14 illustrates this idea with a few microprocessors. Note that the personal computer is also configured in the same manner as the system in Figure 13–14. The bus master is the main microprocessor in the personal computer. What we call the local bus in the personal computer is the shared bus in this illustration. The ISA bus is operated as a slave to the personal computer’s microprocessor as well as any other devices attached to the shared bus. The PCI bus can operate as a slave or a master.

Types of Buses Defined

The local bus is the bus that is resident to the microprocessor. The local bus contains the resident or local memory and I/O. All microprocessors studied thus far in this text are considered to be local bus systems. The local memory and local I/O are accessed by the microprocessor that is directly connected to them.

A shared bus is one that is connected to all microprocessors in the system. The shared bus is used to exchange data between microprocessors in the system. A shared bus may contain memory

and I/O devices that are accessed by all microprocessors in the system. Access to the shared bus is controlled by some form or arbiter that allows only a single microprocessor to access the system’s shared bus space. As mentioned, the shared bus in the personal computer is what we often call the local bus in the personal computer because it is local to the microprocessor in the personal computer.

Figure 13–15 shows an 8088 microprocessor that is connected as a remote bus master. The term bus master applies to any device (microprocessor or otherwise) that can control a bus

containing memory and I/O. The 8237 DMA controller presented earlier in the chapter is an example of a remote bus master. The DMA controller gained access to the system memory and I/O space to cause a data transfer. Likewise, a remote bus master gains access to the shared bus for the same purpose. The difference is that the remote bus master microprocessor can execute variable software, whereas the DMA controller can only transfer data.

Access to the shared bus is accomplished by using the HOLD pin on the microprocessor for the DMA controller. Access to the shared bus for the remote bus master is accomplished via a bus arbiter, which functions to resolve priority between bus masters and allows only one device at a time to access the shared bus.

Notice in Figure 13–15 that the 8088 microprocessor has an interface to both a local, resident bus and the shared bus. This configuration allows the 8088 to access local memory and I/O or, through the bus arbiter and buffers, the shared bus. The task assigned to the microprocessor might be data communications. It may, after collecting a block of data from the communications interface, pass those data on to the shared bus and shared memory so that other microprocessors attached to the system can access the data. This allows many microprocessors to share common data. In the same manner, multiple microprocessors can be assigned various tasks in the system, drastically improving throughput.

The Bus Arbiter

Before Figure 13–15 can be fully understood, the operation of the bus arbiter must be grasped. The 8289 bus arbiter controls the interface of a bus master to a shared bus. Although the 8289 is not the only bus arbiter, it is designed to function with the 8086/8088 microprocessors, so it is presented here. Each bus master or microprocessor requires an arbiter for the interface to the shared bus, which Intel calls the Multibus and IBM calls the Micro Channel.

The shared bus is used only to pass information from one microprocessor to another; otherwise, the bus masters function in their own local bus modes by using their own local programs, memory, and I/O space. Microprocessors connected in this kind of system are often called parallel or distributed processors because they can execute software and perform tasks in parallel.

8289 Architecture. Figure 13–16 illustrates the pin-out and block diagram of the 8289 bus arbiter. The left side of the block diagram depicts the connections to the microprocessor. The right side denotes the 8289 connection to the shared (remote) bus or Multibus.

The 8289 controls the shared bus by causing the READY input to the microprocessor to become a logic 0 (not ready) if access to the shared bus is denied. The blocking occurs whenever another microprocessor is accessing the shared bus. As a result, the microprocessor requesting access is blocked by the logic 0 applied to its READY input. When the READY pin is a logic 0, the micro- processor and its software wait until access to the shared bus is granted by the arbiter. In this manner, one microprocessor at a time gains access to the shared bus. No special instructions are required for bus arbitration with the 8289 bus arbiter because arbitration is accomplished strictly by the hardware.

Pin Definitions

AEN

The address enable output causes the bus drivers in a system to switch to their three-state, high-impedance state.

ANYRQST The any request input is a strapping option that prevents a lower- priority microprocessor from gaining access to the shared bus. If tied to a logic 0, normal arbitration occurs and a lower priority microprocessor can gain access to the shared bus if CBRQ is also a logic O.

BCLK BPRN

The bus clock input synchronizes all shared-bus masters.

The bus priority input allows the 8289 to acquire the shared bus on the next falling edge of the BCLK signal.

The bus priority output is a signal that is used to resolve priority in a system that contains multiple bus masters.

The bus request output is used to request access to the shared bus.

The busy input/output indicates, as an output, that an 8289 has acquired the shared bus. As an input, BUSYis used to detect that another 8289 has acquired the shared bus.

The common bus request input/output is used when a lower priority microprocessor is asking for the use of the shared bus. As an output, CBRQ becomes a logic 0 whenever the 8289 requests the shared bus and remains low until the 8289 obtains access to the shared bus.

CLK The clock input is generated by the 8284A clock generator and provides the internal timing source to the 8289.

CRQLCK

INIT IOB

LOCK

The common request lock input prevents the 8289 from surrendering the shared bus to any of the 8289s in the system. This signal functions in conjunction with the CBRQ pin.

The initialization input resets the 8289 and is normally connected to the system RESET signal.

The I/O bus input selects whether the 8289 operates in a shared-bus system (if selected by RESB) with I/O (IOB 0) or with memory and I/O (IOB 1).

The lock input prevents the 8289 from allowing any other microprocessor from gaining access to the shared bus. An 8086/8088 instruction that contains a LOCK prefix will prevent other microprocessors from accessing the shared bus.

RESB The resident-bus input is a strapping connection that allows the 8289 to operate in systems that have either a shared-bus or resident-bus system.

If RESB is a logic 1, the 8289 is configured as a shared-bus master. If RESB is a logic 0, the 8289 is configured as a local-bus master. When configured as a shared-bus master, access is requested through the SYSB>RESB input pin.

S0, S1, and S2 The status inputs initiate shared-bus requests and surrenders. These pins connect to the 8288 system bus controller status pins.

SYSB>RESB The system bus/resident bus input selects the shared-bus system when placed at a logic 1 or the resident local bus when placed at a logic 0.

General 8289 Operation. As the pin descriptions demonstrate, the 8289 can be operated in three basic modes: (1) I/O peripheral-bus mode, (2) resident-bus mode, and (3) single-bus mode. See Table 13–2 for the connections required to operate the 8289 in these modes. In the I/O peripheral bus mode, all devices on the local bus are treated as I/O, including memory, and are accessed by all instructions. All memory references access the shared bus and all I/O access the resident-local bus. The resident-bus mode allows memory and I/O accesses on both the local and shared buses. Finally, the single-bus mode interfaces a microprocessor to a shared bus, but the microprocessor has no local memory or local I/O. In many systems, one microprocessor is set up as the shared-bus master (single-bus mode) to control the shared bus and become the shared-bus master. The shared-bus master controls the system through shared memory and I/O. Additional microprocessors are connected to the shared bus as resident- or I/O peripheral-bus masters. These additional bus masters usually perform independent tasks that are reported to the shared- bus master through the shared bus.

System Illustrating Single-Bus and Resident-Bus Connections. Single-bus operation inter- faces a microprocessor to a shared bus that contains both I/O and memory resources that are shared by other microprocessors. Figure 13–17 illustrates three 8088 microprocessors, each connected to a shared bus. Two of the three microprocessors operate in the resident-bus mode, while the third operates in the single-bus mode. Microprocessor A, in Figure 13–17, operates in the single-bus mode and has no local bus. This microprocessor accesses only the shared memory and I/O space. Microprocessor A is often referred to as the system-bus master because it is responsible for coordinating the main memory and I/O tasks. The remaining two microprocessors (B and C) are connected in the resident-bus mode, which allows them access to both the shared bus and their own local buses. These resident-bus microprocessors are used to perform tasks that are independent from the system-bus master. In fact, the only time that the system-bus master is interrupted from performing its tasks are when one of the two resident-bus microprocessors needs to transfer data between itself and the shared bus. This connection allows all three micro- processors to perform tasks simultaneously, yet data can be shared between microprocessors when needed.

In Figure 13–17, the bus master (A) allows the user to operate with a video terminal that allows the execution of programs and generally controls the system. Microprocessor B handles all telephone communications and passes this information to the shared memory in blocks. This means that microprocessor B waits for each character to be transmitted or received and controls the protocol used for the transfers. For example, suppose that a 1K-byte block of data is trans- mitted across the telephone interface at the rate of 100 characters per second. This means that the

transfer requires 10 seconds. Rather than tie up the bus master for 10 seconds, microprocessor B patiently performs the data transfer from its own local memory and the local communications interface. This frees the bus master for other tasks. The only time the microprocessor B interrupts the bus master is to transfer data between the shared memory and its local memory system. This data transfer between microprocessor B and the bus master requires only a few hundred microseconds.

Microprocessor C is used as a print spooler. Its only task is to print data on the printer. Whenever the bus master requires printed output, it transfers the task to microprocessor C. Microprocessor C then accesses the shared memory and captures the data to be printed and stores it in its own local memory. Data are then printed from the local memory, freeing the bus master to perform other tasks. This allows the system to execute a program with the bus master, transfer data through the communications interface with microprocessor B, and print information on the printer with microprocessor C. These tasks all execute simultaneously. There is no limit to the number of microprocessors connected to a system or the number of tasks performed simultaneously using this

technique. The only limit is that introduced by the system design and the designer’s ingenuity. Lawrence Livermore Labs in California has a system that contains 4096 Pentium microprocessors.