THE 80X87 ARCHITECTURE

The 80X87 is designed to operate concurrently with the microprocessor. Note that the 80486DX–Core2 microprocessors contain their own internal and fully compatible versions of the 80387. With other family members, the coprocessor is an external integrated circuit that parallels most of the connections on the microprocessor. The 80X87 executes 68 different instructions. The microprocessor executes all normal instructions and the 80X87 executes arithmetic coprocessor instructions. Both the microprocessor and coprocessor will execute their respective instructions simultaneously or concurrently. The numeric or arithmetic coprocessor is a special-purpose micro- processor that is especially designed to efficiently execute arithmetic and transcendental operations.

The microprocessor intercepts and executes the normal instruction set, and the coprocessor intercepts and executes only the coprocessor instructions. Recall that the coprocessor instructions are actually escape (ESC) instructions. These instructions are used by the microprocessor to generate a memory address for the coprocessor so that the coprocessor can execute a coprocessor instruction.

Internal Structure of the 80X87

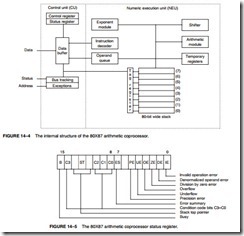

Figure 14–4 shows the internal structure of the arithmetic coprocessor. Notice that this device is divided into two major sections: the control unit and the numeric execution unit.

The control unit interfaces the coprocessor to the microprocessor-system data bus. Both the devices monitor the instruction stream. If the instruction is an ESCape (coprocessor) instruction, the coprocessor executes it; if not, the microprocessor executes it.

The numeric execution unit (NEU) is responsible for executing all coprocessor instructions. The NEU has an eight-register stack that holds operands for arithmetic instructions and the results of arithmetic instructions. Instructions either address data in specific stack data registers or use a push-and-pop mechanism to store and retrieve data on the top of the stack. Other registers in the NEU are status, control, tag, and exception pointers. A few instructions transfer data between the coprocessor and the AX register in the microprocessor. The FSTSW AX instruction is the only instruction available to the coprocessor that allows direct communications to the microprocessor through the AX register. Note that the 8087 does not contain the FSTSW AX instruction, but all newer coprocessors do contain it.

The stack within the coprocessor contains eight registers that are each 80 bits wide. These stack registers always contain an 80-bit extended-precision floating-point number. The only time that data appear as any other form is when they reside in the memory system. The coprocessor converts from signed integer, BCD, single-precision, or double-precision form as the data are moved between the memory and the coprocessor register stack.

Status Register. The status register (see Figure 14–5) reflects the overall operation of the coprocessor. The status register is accessed by executing the instruction (FSTSW), which stores the contents of the status register into a word of memory. The FSTSW AX instruction copies the status register directly into the microprocessor’s AX register on the 80187 or above coprocessor. Once status is stored in memory or the AX register, the bit positions of the

status register can be examined by normal software. The coprocessor/microprocessor communications are carried out through the I/O ports 00FAH–00FFH on the 80187 and 80287, and I/O ports 800000FAH–800000FFH on the 80386 through the Pentium 4. Never use these I/O ports for interfacing I/O devices to the microprocessor.

The newer coprocessors (80187 and above) use status bit position 6 (SF) to indicate a stack overflow or underflow error. Following is a list of the status bits, except for SF, and their applications:

B The busy bit indicates that the coprocessor is busy executing a task. Busy is tested by examining the status register or by using the FWAIT instruction. Newer coprocessors automatically synchronize with the microprocessor, so the busy flag need not be tested before performing additional coprocessor tasks.

C0–C3 The condition code bits indicate conditions about the coprocessor (see Table 14–2 for a complete listing of each combination of these bits and their functions). Note that these bits have different meanings for different instructions, as indicated in the table. The top of the stack is denoted as ST in this table.

TOP The top-of-stack (ST) bit indicates the current register addressed as the top-of-the- stack (ST). This is normally register ST(0).

ES The error summary bit is set if any unmasked error bit (PE, UE, OE, ZE, DE, or IE) is set. In the 8087 coprocessor, the error summary also caused a coprocessor interrupt. Since the 80187, the coprocessor interrupt has been absent from the family.

PE The precision error indicates that the result or operands exceed the selected precision.

UE An underflow error indicates a nonzero result that is too small to represent with the current precision selected by the control word.

OE An overflow error indicates a result that is too large to be represented. If this error is masked, the coprocessor generates infinity for an overflow error.

ZE A zero error indicates the divisor was zero while the dividend is a noninfinity or nonzero number.

DE A denormalized error indicates that at least one of the operands is denormalized.

IE An invalid error indicates a stack overflow or underflow, indeterminate form (0 ÷ 0, +∞, -∞, etc.), or the use of a NAN as an operand. This flag indicates errors such as those produced by taking the square root of a negative number, etc.

There are two ways to test the bits of the status register once they are moved into the AX register with the FSTSW AX instruction. One method uses the TEST instruction to test individual bits of the status register. The other uses the SAHF instruction to transfer the leftmost 8 bits of the status register into the microprocessor’s flag register. Both methods are illustrated in Example 14–6. This example uses the DIV instruction to divide the top of the stack by the contents of DATA1 and the FSQRT instruction to find the square root of the top of the stack. The example also uses the FCOM instruction to compare the contents of the stack top with DATA1. Note that the conditional jump instructions are used with the SAHF instruction to test for the condition listed in Table 14–3. Although SAHF and conditional jumps cannot test all possible operating conditions of the coprocessor, they can help to reduce the complexity of certain tested conditions. Note that SAHF places C0 into the carry flag, C2 into the parity flag, and C3 into the zero flag.

If the Pentium 4 or Core2 is operated in the 64-bit mode, the SAHF instruction does not function. In the 64-bit mode, another method of testing the coprocessor flags is needed, such as testing each bit of AX for C0, C2, and C3. (See Example 14–6.)

When the FXAM instruction and FSTSW AX are executed and followed by the SAHF instruction, the zero flag will contain C3. The FXAM instruction could be used to test a divisor before a division for a zero value by using the JZ instruction following FXAM, FSTSW AX, and SAHF.

Control Register. The control register is pictured in Figure 14–6. The control register selects the precision, rounding control, and infinity control. It also masks and unmasks the exception bits that correspond to the rightmost 6 bits of the status register. The FLDCW instruction is used to load a value into the control register.

Following is a description of each bit or grouping of bits found in the control register:

IC Infinity control selects either affine or projective infinity. Affine allows positive and negative infinity; projective assumes infinity is unsigned.

RC Rounding control determines the type of rounding, as defined in Figure 14–6. PC The precision control sets the precision of the result, as defined in Figure 14–6. Exception Determine whether the error indicated by the exception affects the error bit in masks the status register. If a logic 1 is placed in one of the exception control bits, the corresponding status register bit is masked off.

Tag Register. The tag register indicates the contents of each location in the coprocessor stack. Figure 14–7 illustrates the tag register and the status indicated by each tag. The tag indicates whether a register is valid; zero; invalid or infinity; or empty. The only way that a program can view the tag register is by storing the coprocessor environment using the FSTENV, FSAVE, or FRSTOR instructions. Each of these instructions stores the tag register along with other coprocessor data.