8088 AND 80188 (8-BIT) MEMORY INTERFACE

This text contains separate sections on memory interfacing for the 8088 and 80188 with their 8-bit data buses; the 8086, 80186, 80286, and 80386SX with their 16-bit data buses; the 80386DX and 80486 with their 32-bit data buses; the Pentium–Core2 with their 64-bit data buses. Separate sections are provided because the methods used to address the memory are slightly different in microprocessors that contain different data bus widths. Hardware engineers or technicians who wish to broaden their expertise in interfacing 16-bit, 32-bit, and 64-bit memory interface should cover all sections. This section is much more complete than the sections on the 16-, 32-, and 64-bit-wide memory interface, which cover material not explained in the 8088/80188 section.

In this section, we examine the memory interface to both RAM and ROM and explain the error-correction code (ECC), which is still is currently available to memory system designers. Many home computer systems do not use ECC because of the cost, but business machines often do use it.

Basic 8088/80188 Memory Interface

The 8088 and 80188 microprocessors have an 8-bit data bus, which makes them ideal to connect to the common 8-bit memory devices available today. The 8-bit memory size makes the 8088, and especially the 80188, ideal as a simple controller. For the 8088/80188 to function correctly with the memory, however, the memory system must decode the address to select a memory component. It must also use the RD, WR, and IO>M control signals provided by the 8088/80188 to control the memory system.

The minimum mode configuration is used in this section and is essentially the same as the maximum mode system for memory interface. The main difference is that, in maximum mode,the IO/M signal is combined with RD to generate the MRDC signal, and

IO/M is combined

with WR to generate the MWTC signal. The maximum mode control signals are developed inside the 8288 bus controller. In minimum mode, the memory sees the 8088 or the 80188 as a device with 20 address connections (A19–A0), eight data bus connections (AD7–AD0), and the control signals IO>M, RD, and WR.

Interfacing EPROM to the 8088. You will find this section very similar to Section 10–2 on decoders. The only difference is that, in this section, we discuss wait states and the use of the IO>M signal to enable the decoder.

Figure 10–20 illustrates an 8088/80188 microprocessor connected to three 27256 EPROMs, 32K × 8 memory devices. The 27256 has one more address input (A15) than the 27128 and twice the memory. The 74HCT138 decoder in this illustration decodes three 32K × 8 blocks of memory for a total of 96K × 8 bits of the physical address space for the 8088/80188.

The decoder (74HCT138) is connected a little differently than might be expected because the slower version of this type of EPROM has a memory access time of 450 ns. Recall from Chapter 9 that when the 8088 is operated with a 5 MHz clock, it allows 460 ns for the memory to access data. Because of the decoder’s added time delay (8 ns), it is impossible for this memory to function within 460 ns. In order to correct this problem, the output from the NAND gate can be used to generate a signal to enable the decoder and a signal for the wait state generator, covered in Chapter 9. (Note that the 80188 can internally insert from 0 to 15 wait states without any additional external hardware, so it does not require this NAND gate.) With a wait state inserted every time this section of the memory is accessed, the 8088 will allow 660 ns for the EPROM to access data. Recall that an extra wait state adds 200 ns (1 clock) to the access time. The 660 ns is ample time for a 450 ns memory component to access data, even with the delays introduced by the decoder and any buffers added to the data bus. The wait states are inserted in this system for memory locations C0000H–FFFFFH. If this creates a problem, a three-input OR gate can be added to the three outputs of the decoder to generate a wait signal only for the actual addresses for this system (E8000H–FFFFFH).

Notice that the decoder is selected for a memory address range that begins at location E8000H and continues through location FFFFFH—the upper 96K bytes of memory. This section of memory is an EPROM because FFFF0H is where the 8088 starts to execute instructions after a hardware reset. We often call location FFFF0H the cold-start location. The software stored in this section of memory would contain a JMP instruction at location FFFF0H that jumps to location E8000H so the remainder of the program can execute. In this circuit, U1 is decoded at addresses E8000H–EFFFFH, U2 is decoded at F0000H–F7FFFH, and U3 is decoded at F8000H–FFFFFH.

Interfacing RAM to the 8088. RAM is a little easier to interface than EPROM because most RAM memory components do not require wait states. An ideal section of the memory for the RAM is the very bottom, which contains vectors for interrupts. Interrupt vectors (discussed in more detail in Chapter 12) are often modified by software packages, so it is rather important to encode this section of the memory with RAM.

Figure 10–21 shows sixteen 62256, 32K × 8 static RAMs interfaced to the 8088, beginning at memory location 00000H. This circuit board uses two decoders to select the 16 different RAM memory components and a third to select the other decoders for the appropriate memory sections. Sixteen 32K RAMs fill memory from location 00000H through location 7FFFFH, for 512K bytes of memory.

The first decoder (U4) in this circuit selects the other two decoders. An address beginning with 00 selects decoder U3 and an address that begins with 01 selects decoder U9. Notice that extra pins remain at the output of decoder U4 for future expansion. These pins allow more 256K × 8 blocks of RAM for a total of 1M × 8, simply by adding the RAM and the additional secondary decoders.

Also notice from the circuit in Figure 10–21 that all the address inputs to this section of memory are buffered, as are the data bus connections and control signals RD and WR. Buffering is important when many devices appear on a single board or in a single system. Suppose that three other boards like this are plugged into a system. Without the buffers on each board, the load on the system address, data, and control buses would be enough to prevent proper operation. (Excessive loading causes the logic 0 output to rise above the 0.8 V maximum allowed in a sys- tem.) Buffers are normally used if the memory will contain additions at some future date. If the memory will never grow, then buffers may not be needed.

Interfacing Flash Memory

Flash memory (EEPROM) is becoming commonplace for storing setup information on video cards, as well as for storing the system BIOS in the personal computer. It even finds application in MP3 audio players and USB pen drives. Flash memory is also found in many other applications to store information that is only changed occasionally.

The only difference between a flash memory device and SRAM is that the flash memory device requires a 12V programming voltage to erase and write new data. The 12V can be avail- able either at the power supply or a 5V to 12V converter designed for use with flash memory can be obtained. The newest versions of flash memory are erased with a 5.0V or even a 3.3V signal so that a converter is not needed.

EEPROM is available as either a memory device with a parallel interface or as devices that are serial. The serial device is extremely small and is not suited for memory expansion, but as an I/O device it can store information such as in a flash drive. This section of the text details both memory types.

Figure 10–22 illustrates the 28F400 Intel flash memory device interfaced to the 8088 micro- processor using its parallel interface. The 28F400 can be used as either a 512K × 8 memory device or as a 256K × 16 memory device. Because it is interfaced to the 8088, its configuration is 512K × 8. Notice that the control connections on this device are identical to that of an SRAM: CE, OE, and WE. The only new pins are VPP, which is connected to 12V for erase and programming; PWD, which selects the power-down mode when a logic 0 and is also used for programming; and BYTE, which selects byte (0) or word (1) operation. Note that the pin DQ15 functions as the least significant address input when operated in the byte mode. Another difference is the amount of time required to accomplish a write operation. The SRAM can perform a write operation in as little as 10 ns, but the flash memory requires approximately 0.4 seconds to erase a byte. The topic of programming the flash memory device is covered in Chapter 11, along with I/O devices. The flash memory device has internal registers that are programmed by using I/O techniques not yet explained. This chapter concentrates on its interface to the microprocessor.

Notice in Figure 10–22 that the decoder chosen is the 74LS139 because only a simple decoder is needed for a flash memory device this large. The decoder uses address connection A19 and IO>M as inputs. The A15 signal selects the flash memory for locations 80000H through FFFFFH, and IO>M enables the decoder.

As mentioned, many newer flash memory devices use a serial interface to reduce the cost of the integrated circuit because of fewer pins and a smaller size. Serial flash memory is available in sizes to 4G bytes and has comparable speeds and erase times with the parallel flash devices. Most modern flash memory functions from 5V or 3.3V without the need for a higher programming voltage and has a life of 1,000,000 erases with a storage time of 200 years.

Figure 10–23 illustrates a small serial flash device (a 256K device, organized as a 32K × 8 memory). The three address pins are hardwired to allow more than one device to be placed on a serial bus. In the illustration U1 is wired at address 001 and U2 is wired at address 000. Not shown in the illustration is a pull-up resistor that is needed for the serial data connection. The pull-up may be located in the microprocessor or it may need to be connected externally, depending on the microprocessor and interface connected to the memory.

This memory interface has two signal lines. One is a serial clock (SCL) and the other is a bidirectional serial data line (SDA). The clock frequency can be anything up to 400 KHz, so this type of memory is not meant to replace the main memory in a system. It is fast enough for music or other low-speed data. The serial interface is explained in Chapter 11.

Figure 10–24 depicts the basic serial data format for the serial EEPROM. The serial data contains the address (the A0, A1, A2 pins) in the first byte as well as a device code of 1010, which represents the EEPROM. Other serial devices have different device codes. This is followed by the memory location and the data in additional bytes.

Error Correction

Error-correction schemes have been around for a long time, but integrated circuit manufacturers have only recently started to produce error-correcting circuits. One such circuit is the 74LS636, an 8-bit error correction and detection circuit that corrects any single-bit memory read error and flags any 2-bit error called SECDED (single error correction/double error correction). This device is found in high-end computer systems because of the cost of implementing a system that uses error correction.

The newest computer systems are now using DDR memory with ECC (error-correction code). The scheme to correct the errors that might occur in these memory devices is identical to the scheme discussed in this text.

The 74LS636 corrects errors by storing five parity bits with each byte of memory data. This does increase the amount of memory required, but it also provides automatic error correction for single-bit errors. If more than two bits are in error, this circuit may not detect it. Fortunately, this is rare, and the extra effort required to correct more than a single-bit error is very expensive and not worth the effort. Whenever a memory component fails completely, its bits are all high or all low. In this case, the circuit flags the processor with a multiple-bit error indication.

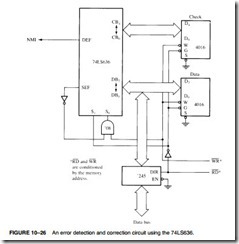

Figure 10–25 depicts the pin-out of the 74LS636. Notice that it has eight data I/O pins, five check bit I/O pins, two control inputs (SO and SI), and two error outputs: single-error flag (SEF) and double-error flag (DEF). The control inputs select the type of operation to be performed and are listed in the truth table of Table 10–1.

When a single error is detected, the 74LS636 goes through an error-correction cycle. It places a 01 on S0 and S1 by causing a wait and then a read following error correction.

Figure 10–26 illustrates a circuit used to correct single-bit errors with the 74LS636 and to interrupt the processor through the NMI pin for double-bit errors. To simplify the illustration, we depict only one 2K × 8 RAM and a second 2K × 8 RAM to store the 5-bit check code. The connection of this memory component is different from that of the previous example. Notice that the S or CS pin is grounded, and data bus buffers control the flow to the sys- tem bus. This is necessary if the data are to be accessed from the memory before the RD strobe goes low.

On the next negative edge of the clock after the RD signal, the 74LS636 checks the single- error flag (SEF) to determine whether an error has occurred. If it has, a correction cycle causes the single-error defect to be corrected. If a double error occurs, an interrupt request is generated by the double-error flag (DEF) output, which is connected to the NMI pin of the microprocessor.

Modern DDR error-correction memory (ECC) does not actually have logic circuitry on board that detects and corrects errors. Since the Pentium, the microprocessor incorporates the logic circuitry to detect/correct errors provided the memory can store the extra 8 bits required for storing the ECC code. ECC memory is 72-bits wide using the additional 8 bits to store the ECC code. If an error occurs, the microprocessor runs the correction cycle to correct the error. Some memory devices such as Samsung memory also perform an internal error check. The Samsung ECC uses 3 bytes to check every 256 bytes of memory, which is far more efficient. Additional information on the Samsung ECC algorithm is available at the Samsung website.