Test Schedule

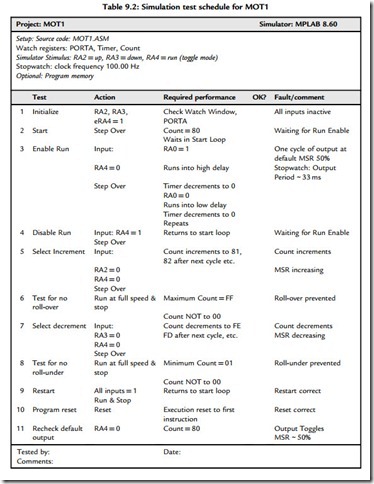

Using the simulator, the program function can be tested against the design requirements. The specification for MOT1 has been converted into a test procedure designed to exercise all its functions; we also need to anticipate incorrect input sequences that may cause a problem.

It is difficult to anticipate exactly what kinds of logical errors will arise, as they are generally the result of inexperience, but the following are typical:

• Port initialization: If a port does not appear to respond to output operations, check that the initialization is correct.

• Register operations: If a register is not responding as it should, ensure that the correct register is being modified, and the address label is correct. Check for correct bank selection during setup.

• Bit test & skip: Obtaining the correct sequence of operations in the program depends on these instructions. Make sure the skip condition logic is correct, as it is easy to get this wrong.

• Jump destinations: Make sure that the destination specified is correct, and the loop sequence includes all the necessary steps.

• Program structure: If the program gets lost during subroutine execution, check that call address labels are correct, and all subroutines are terminated with ‘return’ instructions.