INTRODUCTION

Whether simple or complex, every microprocessor-based system has a memory system. The Intel family of microprocessors is no different from any other in this respect. Almost all systems contain two main types of memory: read-only memory (ROM) and random access memory (RAM) or read/write memory. Read-only memory contains system software and permanent system data, while RAM contains temporary data and application software. This chapter explains how to interface both memory types to the Intel family of microprocessors. We demonstrate memory interface to an 8-, 16-, 32-, and 64-bit data bus by using various memory address sizes. This allows virtually any microprocessor to be interfaced to any memory system.

CHAPTER OBJECTIVES

Upon completion of this chapter, you will be able to:

1. Decode the memory address and use the outputs of the decoder to select various memory components.

2. Use programmable logic devices (PLDs) to decode memory addresses.

3. Explain how to interface both RAM and ROM to a microprocessor.

4. Explain how error correction code (ECC) is used with memory.

5. Interface memory to an 8-, 16-, 32-, and 64-bit data bus.

6. Explain the operation of a dynamic RAM controller.

7. Interface dynamic RAM to the microprocessor.

MEMORY DEVICES

Before attempting to interface memory to the microprocessor, it is essential to completely under- stand the operation of memory components. In this section, we explain the functions of the four common types of memory: read-only memory (ROM), flash memory (EEPROM), static random access memory (SRAM), and dynamic random access memory (DRAM).

Pin connections common to all memory devices are the address inputs, data outputs or input/ outputs, some type of selection input, and at least one control input used to select a read or write operation. See Figure 10–1 for ROM and RAM generic-memory devices.

Address Connections. All memory devices have address inputs that select a memory location within the memory device. Address inputs are almost always labeled from A0, the least significant address input, to An where subscript n can be any value but is always labeled as one less than the total number of address pins. For example, a memory device with 10 address pins has its address pins labeled from A0 to A9. The number of address pins found on a memory device is determined by the number of memory locations found within it.

Today, the more common memory devices have between 1K (1024) to 1G (1,073,741,824) memory locations, with 4G and larger memory location devices on the horizon. A 1K memory device has 10 address pins (A0–A9); therefore, 10 address inputs are required to select any of its 1024 memory locations. It takes a 10-bit binary number (1024 different combinations) to select any single location on a 1024-location device. If a memory device has 11 address connections (A0–A11), it has 2048 (2K) internal memory locations. The number of memory locations can thus be extrapolated from the number of address pins. For example, a 4K memory device has 12 address connections, an 8K device has 13, and so forth. A device that contains 1M locations requires a 20-bit address (A0–A19).

The number 400H represents a 1K-byte section of the memory system. If a memory device is decoded to begin at memory address 10000H and it is a 1K device, its last location is at address 103FFH—one location less than 400H. Another important hexadecimal number to remember is 1000H, because 1000H is 4K. A memory device that contains a starting address of 14000H that is 4K bytes long ends at location 14FFFH—one location less than 1000H. A third number is 64K, or 10000H. A memory that starts at location 30000H and ends at location 3FFFFH is a 64K-byte memory. Finally, because 1M of memory is common, a 1M memory contains 100000H memory locations.

Data Connections. All memory devices have a set of data outputs or input/outputs. The device illustrated in Figure 10–1 has a common set of input/output (I/O) connections. Today, many memory devices have bidirectional common I/O pins.

The data connections are the points at which data are entered for storage or extracted for reading. Data pins on memory devices are labeled D0 through D7 for an 8-bit-wide memory

device. In this sample memory device there are 8 I/O connections, meaning that the memory device stores 8 bits of data in each of its memory locations. An 8-bit-wide memory device is often called a byte-wide memory. Although most devices are currently 8 bits wide, some devices are 16 bits, 4 bits, or just 1 bit wide.

Catalog listings of memory devices often refer to memory locations times bits per location. For example, a memory device with 1K memory locations and 8 bits in each location is often listed as a 1K × 8 by the manufacturer. A 16K × 1 is a memory device containing 16K 1-bit memory locations. Memory devices are often classified according to total bit capacity. For example, a 1K × 8-bit memory device is sometimes listed as an 8K memory device, or a 64K × 4 memory is listed as a 256K device. These variations occur from one manufacturer to another.

election Connections. Each memory device has an input—sometimes more than one—that selects or enables the memory device. This type of input is most often called a chip select (CS), chip enable (CE), or simply select (S) input. RAM memory generally has at least one CS or S input, and ROM has at least one CE. If the CE, CS, or S input is active (a logic 0, in this case, because of the overbar), the memory device performs a read or write operation; if it is inactive (a logic 1, in this case), the memory device cannot do a read or a write because it is turned off or disabled. If more than one CS connection is present, all must be activated to read or write data.

Control Connections. All memory devices have some form of control input or inputs. A ROM usually has only one control input, while a RAM often has one or two control inputs.

The control input most often found on a ROM is the output enable (OE) or gate (G) connection, which allows data to flow out of the output data pins of the ROM. If OE and the selection input (CE) are both active, the output is enabled; if OE is inactive, the output is disabled at its high-impedance state. The OE connection enables and disables a set of three-state buffers located within the memory device and must be active to read data.

A RAM memory device has either one or two control inputs. If there is only one control input, it is often called R>W. This pin selects a read operation or a write operation only if the device is selected by the selection input (CS). If the RAM has two control inputs, they are usually labeled WE (or W), and OE (or G). Here, WE (write enable) must be active to perform a memory write, and OE must be active to perform a memory read operation. When these two controls (WE and OE) are pre- sent, they must never both be active at the same time. If both control inputs are inactive (logic 1s), data are neither written nor read, and the data connections are at their high-impedance state.

ROM Memory

The read-only memory (ROM) permanently stores programs and data that are resident to the sys- tem and must not change when power supply is disconnected. The ROM is permanently programmed so that data are always present, even when power is disconnected. This type of memory is often called nonvolatile memory, because its contents do not change even if power is disconnected.

Today, the ROM is available in many forms. A device we call a ROM is purchased in mass quantities from a manufacturer and programmed during its fabrication at the factory. The EPROM (erasable programmable read-only memory), a type of ROM, is more commonly used when software must be changed often or when too few are in demand to make the ROM economical. For a ROM to be practical, we usually must purchase at least 10,000 devices to recoup the factory programming charge. An EPROM is programmed in the field on a device called an EPROM programmer. The EPROM is also erasable if exposed to high-intensity ultra- violet light for about 20 minutes or so, depending on the type of EPROM.

PROM memory devices are also available, although they are not as common today. The PROM (programmable read-only memory) is also programmed in the field by burning open tiny NI-chrome or silicon oxide fuses; but once it is programmed, it cannot be erased.

Still another, newer type of read-mostly memory (RMM) is called the flash memory. The flash memory1 is also often called an EEPROM (electrically erasable programmable ROM), EAROM (electrically alterable ROM), or a NOVRAM (nonvolatile RAM). These memory devices are electrically erasable in the system, but they require more time to erase than a normal RAM. The flash memory device is used to store setup information for systems such as the video card in the computer. It has all but replaced the EPROM in most computer systems for the BIOS memory. Some systems contain a password stored in the flash memory device. Flash memory has its biggest impact in memory cards for digital cameras and memory in MP3 audio players.

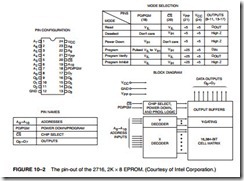

Figure 10–2 illustrates the 2716 EPROM, which is representative of most common EPROMs. This device contains 11 address inputs and eight data outputs. The 2716 is a 2K × 8 read-only memory device. The 27XXX series of the EPROMs includes the following part numbers: 2704 (512 × 8), 2708 (1K × 8), 2716 (2K × 8), 2732 (4K × 8), 2764 (8K × 8), 27128 (16K × 8), 27256 (32K × 8), 27512 (64K × 8), and 271024 (128K × 8). Each of these parts contains address pins, eight data connections, one or more chip selection inputs (CE), and an output enable pin (OE).

Figure 10–3 illustrates the timing diagram for the 2716 EPROM. Data appear on the out- put connections only after a logic 0 is placed on both CE and OE pin connections. If CE and OE are not both logic 0s, the data output connections remain at their high-impedance or off states. Note that the VPP pin must be placed at a logic 1 level for data to be read from the EPROM. In some cases, the VPP pin is in the same position as the WE pin on the SRAM. This will allow a single socket to hold either an EPROM or an SRAM. An example is the 27256 EPROM and the 62256 SRAM, both 32K × 8 devices that have the same pin-out, except for VPP on the EPROM and WE on the SRAM.

One important piece of information provided by the timing diagram and data sheet is the memory access time—the time that it takes the memory to read information. As Figure 10–3 illustrates, memory access time (TACC) is measured from the appearance of the address at the address inputs until the appearance of the data at the output connections. This is based on the assumption that the CE input goes low at the same time that the address inputs become stable. Also, OE must be a logic 0 for the output connections to become active. The basic speed of this EPROM is 450 ns. (Recall that the 8086/8088 operated with a 5 MHz clock allowed memory 460 ns to access data.) This type of memory component requires wait states to operate properly with the 8086/8088 microprocessors because of its rather long access time. If wait states are not desired, higher-speed versions of the EPROM are available at an additional cost. Today, EPROM memory is available with access times of as little as 100 ns. Obviously, wait states are required in modern microprocessors for any EPROM device.

Static RAM (SRAM) Devices

Static RAM memory devices retain data for as long as DC power is applied. Because no special action (except power) is required to retain stored data, these devices are called static memory. They are also called volatile memory because they will not retain data without power. The main

difference between a ROM and a RAM is that a RAM is written under normal operation, whereas a ROM is programmed outside the computer and normally is only read. The SRAM, which stores temporary data, is used when the size of the read/write memory is relatively small. Today, a small memory is one that is less than 1M byte.

Figure 10–4 illustrates the 4016 SRAM, which is a 2K × 8 read/write memory. This device has 11 address inputs and eight data input/output connections. This device is representative of all SRAM devices, except for the number of address and data connections.

The control inputs of this RAM are slightly different from those presented earlier. The OE pin is labeled G, the CS pin is S, and the WE pin is W. Despite the altered designations, the con- trol pins function exactly the same as those outlined previously. Other manufacturers make this popular SRAM under the part numbers 2016 and 6116.

Figure 10–5 depicts the timing diagram for the 4016 SRAM. As the read cycle timing reveals, the access time is ta(A). On the slowest version of the 4016, this time is 250 ns, which is fast enough to connect directly to an 8088 or an 8086 operated at 5 MHz without wait states.

Again, it is important to remember that the access time must be checked to determine the compatibility of memory components with the microprocessor.

Figure 10–6 on p. 336 illustrates the pin-out of the 62256, 32K × 8 static RAM. This device is packaged in a 28-pin integrated circuit and is available with access times of 120 ns or 150 ns. Other common SRAM devices are available in 8K × 8, 128K × 8, 256K × 8, 512K × 8, and 1M × 8 sizes, with access times of as little as 1.0 ns for SRAM used in computer cache memory systems.

Dynamic RAM (DRAM) Memory

About the largest static RAM available today is a 1M × 8. Dynamic RAM, on the other hand, is available in much larger sizes: up to 256M × 8 (2G bits). In all other respects, DRAM is essentially the same as SRAM, except that it retains data for only 2 or 4 ms on an integrated capacitor. After 2 or 4 ms, the contents of the DRAM must be completely rewritten (refreshed) because the capacitors, which store a logic 1 or logic 0, lose their charges.

Instead of requiring the almost impossible task of reading the contents of each memory location with a program and then rewriting them, the manufacturer has internally constructed the DRAM differently from the SRAM. In the DRAM, the entire contents of the memory are refreshed with 256 reads in a 2- or 4-ms interval. Refreshing also occurs during a write, a read, or during a special refresh cycle. Much more information about DRAM refreshing is provided in Section 10–6.

Another disadvantage of DRAM memory is that it requires so many address pins that the manufacturers have decided to multiplex the address inputs. Figure 10–7 illustrates a 64K × 4 DRAM, the TMS4464, which stores 256K bits of data. Notice that it contains only eight address inputs where it should contain 16—the number required to address 64K memory locations. The

inputs and strobed into an internal column latch by CAS as the column address (see Figure 10–8 for this timing). The 16-bit address held in these internal latches addresses the contents of one of the 4-bit memory locations. Note that CAS also performs the function of the chip selection input to the DRAM.

Figure 10–9 illustrates a set of multiplexers used to strobe the column and row addresses into the eight address pins on a pair of TMS4464 DRAMs. Here, the RAS signal not only strobes

the row address into the DRAMs, but it also selects which part of the address is applied to the address inputs. This is possible due to the long propagation-delay time of the multiplexers. When RAS is a logic 1, the B inputs are connected to the Y outputs of the multiplexers; when the RAS input goes to a logic 0, the A inputs connect to the Y outputs. Because the internal row address latch is edge-triggered, it captures the row address before the address at the inputs changes to the column address. More detail on DRAM and DRAM interfacing is provided in Section 10–6.

As with the SRAM, the R>W pin writes data to the DRAM when a logic 0, but there is no pin labeled G or enable. There also is no S (select) input to the DRAM. As mentioned, the CAS input selects the DRAM. If selected, the DRAM is written if R>W 0 and read if R>W 1.

Figure 10–10 shows the pin-out of the 41256 dynamic RAM. This device is organized as a 256K × 1 memory, requiring as little as 70 ns to access data.

More recently, larger DRAMs have become available that are organized as a 16M × 1, 256M × 1, 512M × 1, 1G × 1, and 2G × 1 memory. On the horizon is the 4G × 1 memory, which is in the planning stages. DRAM memory is often placed on small circuit boards called SIMMs (Single In-Line Memory Modules). Figure 10–11 shows the pin-outs of the two most common SIMMs. The 30-pin SIMM is organized most often as 1M × 8 or 1M × 9, and 4M × 8 or 4M × 9. (Illustrated in Figure 10–11 is a 4M × 9.) The ninth bit is the parity bit. Also shown is a newer 72 pin SIMM. The 72-pin SIMMs are often organized as 1M × 32 or 1M × 36 (with parity). Other sizes are 2M × 32, 4M × 32, 8M × 32, and 16M × 32. These are also available with parity. Figure 10–11 illustrates a 4M × 36 SIMM, which has 16M bytes of memory.

Lately, many systems are using the Pentium–Pentium 4 microprocessors. These micro- processors have a 64-bit wide data bus, which precludes the use of the 8-bit-wide SIMMs described here. Even the 72-pin SIMMs are cumbersome to use because they must be used in pairs to obtain a 64-bit-wide data connection. Today, the 64-bit-wide DIMMs (Dual In-line Memory Modules) have become the standard in most systems. The memory on these modules is organized as 64 bits wide. The common sizes available are 16M bytes (2M × 64), 32M bytes (4M × 64), 64M bytes (8M × 64), 128M bytes (16M × 64), 256M bytes (32M × 64), 512M bytes (64M × 64), and 1G bytes (128M × 64). The pin-out of the DIMM is illustrated in Figure 10–12.

The DIMM module is available in DRAM, EDO, SDRAM, and DDR (double-data rate) forms,

with or without an EPROM. The EPROM provides information to the system on the size and the speed of the memory device for plug-and-play applications.

Another addition to the memory market is the RIMM memory module from RAMBUS Corporation, although this memory type has faded from the market. Like the SDRAM, the RIMM contains 168 pins, but each pin is a two-level pin, bringing the total number of connections to 336. The fastest SDRAM currently available is the PC-4400 or 500 DDR, which operates at a rate of 4.4G bytes per second. By comparison, the 800 MHz RIMM operates at a rate of 3.2G bytes per second and is no longer supported in many systems. RDRAM had a fairly short life in the volatile computer market. The RIMM module is organized as a 32-bit-wide device. This means that to populate a Pentium 4 memory, RIMM memory is used in pairs. Intel claims that the Pentium 4 system using RIMM modules is 300% faster than a Pentium III using PC-100 memory. According to RAMBUS, the current 800 MHz RIMM has been increased to a speed of 1200 MHz, but it is still not fast enough to garner much of a market share.

Currently the latest DRAM is the DDR (double-data rate) memory device and DDR2. The DDR memory transfers data at each edge of the clock, making it operate at twice the speed of SDRAM. This does not affect the access time for the memory, so many wait states are still required to operate this type of memory, but it can be much faster than normal SDRAM memory and that includes RDRAM.