MISCELLANEOUS DATA TRANSFER INSTRUCTIONS

Don’t be fooled by the term miscellaneous; these instructions are used in programs. The data transfer instructions detailed in this section are XCHG, LAHF, SAHF, XLAT, IN, OUT, BSWAP, MOVSX, MOVZX, and CMOV. Because the miscellaneous instructions are not used as often as a MOV instruction, they have been grouped together and presented in this section.

XCHG

The XCHG (exchange) instruction exchanges the contents of a register with the contents of any other register or memory location. The XCHG instruction cannot exchange segment registers or memory-to-memory data. Exchanges are byte-, word-, or doubleword-sized (80386 and above), and they use any addressing mode discussed in Chapter 3, except immediate addressing. Table 4–17 shows some examples of the XCHG instruction. In the 64-bit mode, data sizes may also be 64 bits for the exchange instruction.

The XCHG instruction, using the 16-bit AX register with another 16-bit register, is the most efficient exchange. This instruction occupies 1 byte of memory. Other XCHG instructions require 2 or more bytes of memory, depending on the addressing mode selected.

When using a memory-addressing mode and the assembler, it doesn’t matter which operand addresses memory. The XCHG AL,[DI] instruction is identical to the XCHG [DI],AL instruction, as far as the assembler is concerned.

If the 80386 through the Core2 microprocessor is available, the XCHG instruction can exchange doubleword data. For example, the XCHG EAX,EBX instruction exchanges the con- tents of the EAX register with the EBX register.

LAHF and SAHF

The LAHF and SAHF instructions are seldom used because they were designed as bridge instructions. These instructions allowed 8085 (an early 8-bit microprocessor) software to be translated into 8086 software by a translation program. Because any software that required translation was completed many years ago, these instructions have little application today. The LAHF instruction transfers the rightmost 8 bits of the flag register into the AH register. The SAHF instruction transfers the AH register into the rightmost 8 bits of the flag register.

At times, the SAHF instruction may find some application with the numeric coprocessor. The numeric coprocessor contains a status register that is copied into the AX register with the FSTSW AX instruction. The SAHF instruction is then used to copy from AH into the flag register. The flags are then tested for some of the conditions of the numeric coprocessor. This is detailed in Chapter 14, which explains the operation and programming of the numeric coprocessor. Because LAHF and LAFH are legacy instructions, they do not function in the 64-bit mode and are invalid instructions.

XLAT

The XLAT (translate) instruction converts the contents of the AL register into a number stored in a memory table. This instruction performs the direct table lookup technique often used to convert one code to another. An XLAT instruction first adds the contents of AL to BX to form a memory address within the data segment. It then copies the contents of this address into AL. This is the only instruction that adds an 8-bit number to a l6-bit number.

Suppose that a 7-segment LED display lookup table is stored in memory at address TABLE. The XLAT instruction then uses the lookup table to translate the BCD number in AL to a 7-segment code in AL. Example 4–11 provides a sequence of instructions that converts from a BCD code to a 7-segment code. Figure 4–19 shows the operation of this example program if TABLE = 1000H, DS = 1000H, and the initial value of AL = 05H 15 BCD2. After the translation, AL = 6DH.

IN and OUT

Table 4–18 lists the forms of the IN and OUT instructions, which perform I/O operations. Notice that the contents of AL, AX, or EAX are transferred only between the I/O device and the micro- processor. An IN instruction transfers data from an external I/O device into AL, AX, or EAX; an OUT transfers data from AL, AX, or EAX to an external I/O device. (Note that only the 80386 and above contain EAX.)

Two forms of I/O device (port) addressing exist for IN and OUT: fixed port and variable port. Fixed-port addressing allows data transfer between AL, AX, or EAX using an 8-bit I/O port

address. It is called fixed-port addressing because the port number follows the instruction’s opcode, just as it did with immediate addressing. Often, instructions are stored in ROM. A fixed- port instruction stored in ROM has its port number permanently fixed because of the nature of read-only memory. A fixed-port address stored in RAM can be modified, but such a modification does not conform to good programming practices.

The port address appears on the address bus during an I/O operation. For the 8-bit fixed-port I/O instructions, the 8-bit port address is zero-extended into a 16-bit address. For example, if the IN AL,6AH instruction executes, data from I/O address 6AH are input to AL. The address appears as a 16-bit 006AH on pins A0–A15 of the address bus. Address bus bits A16–A19 (8086/8088), A16–A23 (80286/80386SX), A16–A24 (80386SL/80386SLC/ 80386EX), or A16–A31 (80386–Core2) are undefined for an IN or OUT instruction. Note that Intel reserves the last 16 I/O ports (FFF0H–FFFFH) for use with some of its peripheral components.

Variable-port addressing allows data transfers between AL, AX, or EAX and a 16-bit port address. It is called variable-port addressing because the I/O port number is stored in register DX, which can be changed (varied) during the execution of a program. The 16-bit I/O port address appears on the address bus pin connections A0–A15. The IBM PC uses a 16-bit port address to access its I/O space. The ISA bus I/O space for a PC is located at I/O port 0000H–03FFH. Note that PCI bus cards may use I/O addresses above 03FFH.

Figure 4–20 illustrates the execution of the OUT 19H,AX instruction, which transfers the contents of AX to I/O port 19H. Notice that the I/O port number appears as a 0019H on the 16-bit address bus and that the data from AX appears on the data bus of the microproces- sor. The system control signal IOWC (I/O write control) is a logic zero to enable the I/O device.

A short program that clicks the speaker in the personal computer appears in Example 4–12. The speaker (in DOS only) is controlled by accessing I/O port 61H. If the rightmost 2 bits of this port are set (11) and then cleared (00), a click is heard on the speaker. Note that this program uses a logical OR instruction to set these 2 bits and a logical AND instruction to clear them. These logic operation instructions are described in Chapter 5. The MOV CX,8000H instruction, followed by the LOOP L1 instruction, is used as a time delay. If the count is increased, the click will become longer; if shortened, the click will become shorter. To obtain a series of clicks that can be heard, the program must be modified to repeat many times.

MOVSX and MOVZX

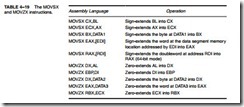

The MOVSX (move and sign-extend) and MOVZX (move and zero-extend) instructions are found in the 80386–Pentium 4 instruction sets. These instructions move data, and at the same time either sign- or zero-extend it. Table 4–19 illustrates these instructions with several examples of each.

When a number is zero-extended, the most significant part fills with zeros. For example, if an 8-bit 34H is zero-extended into a 16-bit number, it becomes 0034H. Zero-extension is often used to convert unsigned 8- or 16-bit numbers into unsigned 16- or 32-bit numbers by using the MOVZX instruction.

A number is sign-extended when its sign-bit is copied into the most significant part. For example, if an 8-bit 84H is sign-extended into a 16-bit number, it becomes FF84H. The sign-bit of an 84H is a 1, which is copied into the most significant part of the sign-extended result. Sign- extension is most often used to convert 8- or 16-bit signed numbers into 16- or 32-bit signed numbers by using the MOVSX instruction.

BSWAP

The BSWAP (byte swap) instruction is available only in the 80486–Pentium 4 microprocessors. This instruction takes the contents of any 32-bit register and swaps the first byte with the fourth, and the second with the third. For example, the BSWAP EAX instruction with

EAX = 00112233H swaps bytes in EAX, resulting in EAX = 33221100H. Notice that the order of all 4 bytes is reversed by this instruction. This instruction is used to convert data between the big and little endian forms. In 64-bit operation for the Pentium 4, all 8 bytes in the selected operand are swapped.

CMOV

The CMOV (conditional move) class of instruction is new to the Pentium Pro–Core2 instruction sets. There are many variations of the CMOV instruction. Table 4–20 lists these variations

of CMOV. These instructions move the data only if the condition is true. For example, the CMOVZ instruction moves data only if the result from some prior instruction was a zero. The destination is limited to only a 16- or 32-bit register, but the source can be a 16- or 32-bit register or memory location.

Because this is a new instruction, you cannot use it with the assembler unless the .686 switch is added to the program.