6.2 OVERVIEW: Z80 INSTRUCTION SET

The instruction set of a microprocessor determines the capability of its operations, the power of its data manipulation, and the ease of programming it. Although it is necessary to have an overall view of the instruction set, our intent here is merely to acquaint you with the overall operations and capability of the Z80 microprocessor. As you progress through the chapters of Part II, you will be exposed to various instructions in more detail along with their applications.

The Z80 microprocessor has 158 instruction types; it includes all the instructions of the Intel 8080 microprocessor and all but two of the 8085. As discussed in Chapter 1, each instruction has two parts: one is the task to be performed (such as Load, Add, and Jump), called the operation code (opcode); and the second identifies the data to be operated on, called the operand. First, we will examine various formats of these instructions in terms of number of bytes and then their classification according to their function.

6.2.1 Instruction Format

An instruction is a command to the microprocessor to perform a given task on specified data. The size of Z80 instructions ranges from one to four bytes; thus, the number of memory registers (locations) required to write (or store) them varies. For example, to write a 3-byte instruction into memory requires three memory locations. Most opcodes (operation codes) are specified in one byte; however, some specialized opcodes require two bytes. The operand (or data) can be specified in the following ways: 8-bit data, 16-bit data, registers, register pairs, I/O addresses, and memory addresses. The Z80 instruction set can be classified into four groups according to the length of an instruction: l-byte to 4-byte instructions. Because the Z80 is an 8-bit microprocessor, the terms "byte" and "word" are used synonymously.

1-BYTE INSTRUCTIONS

In a 1-byte instruction, the Opcode and the operand are included in the same byte as shown in the following examples.

In this instruction, the opcode LD is specified by the first two bits (01), and the operand registers A and B are specified by the remaining six bits. (The accumulator A is represented by 111 and register B by 000.) These bits are associated with the internal microoperations of the microprocessor and are not relevant for learning the instruction set.

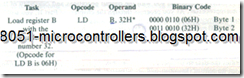

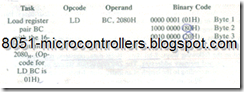

2-BYTE INSTRUCTIONS

In a 2-byte instruction, the first byte specifies the opcode and the second byte specifies the operand (with exceptions of some Z80 two-opcode instructions).

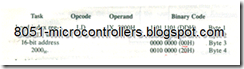

3-BYTEINSTRUCTIONS

In a 3-byte instruction, the first byte specifies the opcode, and the following two bytes specify the 16-bit address or data in a reversed order: low-order byte followed by the high-order byte. For example:

4-BYTE INSTRUCTIONS

The descriptions given above for 2- and 3-byte instructions are valid for the instructions compatible with the 8080 instructions. The Z80 instruction set, however, includes numerous special-purpose instructions that are not compatible with the 8080 instruction set. An 8-bit microprocessor can have a maximum of 256 bit combinations; thus, its instruction set is limited to 256 operation codes. The 8080 has already used 242 combinations for its 72 different instructions, leaving only 14 combinations unused. However, the Z80 microprocessor needs many more combinations to use its additional registers (two index register alternate registers, interrupt vector, and refresh). This problem was resolved by designing 2byte opcodes: unused opcodes combined with instruction opcodes.Z80 4-byte instructions are generally associated with index registers, as shown in the following example.

In this instruction, the opcode has two bytes, DD and 21. Now we can discuss various instructions according to their functional classification.

6.2.2 Z80 Instruction Set

The Z80 instruction set can be divided into six major categories as follows:

1. Data Copy (Transfer) or Load Operations

2. Arithmetic Operations

3. Logic Operations

4. Bit Manipulation

5. Branch Operations

6. Machine Control Operations

DATA COPY OR LOAD OPERATIONS

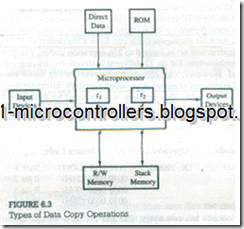

Copying data is one of the major functions the microprocessor needs to perform. The Z80 has numerous instructions that copy data from one location, called source, to another location, calIed destination, without modifying the contents of the source. In technical manuals, this function is quite often referred to as data transfer. However, since the term data transfer creates the impression that the contents of the source are destroyed, we prefer the term data copy. In this text, we have also used the terms Load, Read, and Write to describe data copy operations.

Figure 6.3 shows various categories of data copy operations. The Z80 has several instructions associated with each category, each of which, with its subdivisions, is listed below with examples of instructions.

Data Copy Operations

1. From one register into another register

Copy the contents of register B into the accumulator.

LD, A, B; LD means Load

2. (a) Specific data byte into a register or a memory location.

Load registers B with the hexadecimal number 32. LD B, 32H

(b) Specific I6-bit data into a. register pair.

Load register pair HL with hexadecimal number 2050 . LD HL, 2050H

3. From a memory location into a register or vice versa.

Copy data from memory location 2080H into the accumulator. LD A, (2080H)*

4. (a) From an input port into the accumulator.

Read data from input port 01H and copy into the accumulator. IN A, (01H)*

(b) From the accumulator into an output port.

Write (send) the contents of the accumulator into port 07H• OUT (07H), * A

5. From microprocessor registers into stack memory locations and vice versa.

Copy the contents of register pair BC into defined stack memory locations. PUSH BC

6. Exchange contents between registers. (This is a slightly different operation from data copy; this is a data exchange.)

Exchange the contents of general purpose registers (BC, DE, HL) with alternate registers. EXX

General characteristics of these data copy instructions can be listed as follows:

1. In data copy operations, the contents of the source are copied into the destination without affecting the contents of the source (except in Exchange instructions).

2. In an operand, the destination is specified first, followed by the source. For example, in the instruction LD A, B (copy the contents of B into A), the source is register B and the destination is the accumulator. This may appear backward because the flow is generally assumed to be from left to right, the way we read text.

3. The memory and I/O addresses are enclosed in parentheses.

4. In some instructions, operand is implicit (for example, EXX).

5. Data copy instructions do not affect flags.

ARITHMETIC OPERATIONS

The Z80 instruction set includes four types of arithmetic operations:addition,subtraction,increment/decrement, and I’s and 2’s complement. In 8-bit arithmetic operations, the accumulator is generally assumed to be one of the operands (with the exception of increment/decrement instructions).

· Addition. Any 8-bit number, or the contents of a register, or the contents of a memory location can be added to the contents of the accumulator. The result of the addition is stored in the accumulator, and the flags are affected by the result No two other 8-bit registers can be added directly; for example, the contents of register B cannot be added directly to the contents of register C.

· Subtraction. Any 8-bit number, or the contents of a register, or the contents of a memory location can be subtracted from the contents of accumulator, the subtraction is performed in 2’s complement, and the result is stored in the accumulator. The result modifies the flags, and if the result is negative, it. is expressed in 2’s complement. The following mnemonics indicate that the accumulator is implicitly assumed as one of the operands.

· Increment/Decrement. The 8-bit contents of a register (including the accumulator) or a memory location can be incremented or decremented by 1. Similarly, the l6-bit contents of a register pair (such as HL) can be incremented or decremented by 1. Unlike Add and Subtract, these operations can be performed in any of the registers. The instructions related to 8-bit contents affect flags (except Carry); on the other hand, instructions related to l6-bit contents do not affect any flags.

l’s and 2’s Complement. The contents of the accumulator can be complemented (I’s or 2’s complement), and the result is stored in the accumulator. Some flags are affected by the result. These instructions assume that the operand is the accumulator.