Microprocessor Based System : MPU, Memory, and 1/0

A microprocessor-based system consists primarily of three components-the microprocessor unit (MPU). memory. and I/O (input / output). The MPU is the central player; it communicates with memory and I/O devices. processes data, and controls timing of all its operations. In this chapter. we will examine what the MPU does and what its requirements are. We then design a model for a generalized MPU that expands on the bus concept discussed in the previous chapter and shows signals necessary for the MPU to communicate with other devices. The model also describes the requirements for processing data and shows registers and logic circuits the MPU needs.

Memory and 1I0s are integral parts of a microprocessor-based system. We will discuss memory in terms of its basic elements-latches and registers-and specify the requirements for a memory chip to store information and communicate with the MPU. Based on those requirements, we then develop the concepts of memory addressing and memory maps. We also discuss how the MPU addresses and communicates with I/Os.

OBJECTIVES

· List the four program-initiated operations performed by the MPU.

· Define the functions of the address bus. data bus. and control signals.

· List the externally initiated operations the MPU should respond to.

· Draw the model of a generalized MPU showing the necessary signals.

· List the types of registers the MPU needs to process data internally.

· Explain the internal organization of memory and the requirements of a memory chip to store information and communicate with the MPU.

· Explain the functions of the control signals: Chip Select (CS). Read (RD),and Write (WR).

· Explain how memory addresses are assigned to a memory chip and recognize the’ address range of a given chip in a microprocessor based system.

· List the two techniques of addressing I/O devices.

· Draw a block diagram of a microprocessor based system showing the MPU. memory. I/Os. and buses.

The Microprocessor Unit (MPU)

is a programmable logic device with a designed set of instructions. In this section. we will examine the functions and requirements of the MPU and derive a generalized model. From the previous chapter, we can recall what the MPU does. It reads or fetches each instruction, one at a time, from memory and performs data manipulation specified by the instruction; it also reads data from input devices. and writes (or sends) data to output devices.

When the MPU is executing a program. it communicates frequently with memory and 1/0 devices; the process consists of fetch, decode, and execute operations. However. the question is: Can it respond to unexpected events? For example, while printing a long program. can it stop printing temporarily and read any critical data that may arrive at the input? Can it be "interrupted"? Can it wait until a peripheral is ready? For example. when memory response is too slow, can the MPU wait until memory is ready? The answer to all these questions must be affirmative.

In addition to processing data according to the instructions written in memory, the MPU needs to respond to various situations described above. External devices should be able to interrupt and request the attention of the MPU. This communication process and related operations between the MPU and the external devices (memory, 1/Os) can be classified into two main categories:

· Program-initiated operations

· Peripheral (or externally) initiated operations.

To perform these operations, the MPU requires a group of logic circuits, a set of signals to transfer information, control signals for timing, and clock circuitry; these constitute the architecture. Early microprocessors did not have the necessary circuitry on one chip; the complete units were made up of more than one chip. Therefore, we define here the term Microprocessor Unit (MPU) as a group of device that can perform operations similar to those of the Central Processing Unit (CPU). For example, the 8080A MPU requires three chips to make it a functional unit. However, since later microprocessors include most of the necessary circuitry on a single chip, the terms MPU and microprocessor are often used synonymously.

Program-Initiated Operations and Buses

To communicate with memory and IIOs, the MPU performs four operations:

1. Memory Read: Reads instructions or data from memory.

2. Memory Write: Writes instructions or data into memory.

3. I/O Read: Accepts data from input devices.

4. I/O Write: Sends data to output devices.

Now the question is: how does the MPU identify a memory register or an I/O device? It does so the same way we identify a house: we give a number. Because it understands only the binary numbers, the MPU identifies each memory register or 1/0 by a binary number called an address. The next question is: how does’ the MPU inform the peripherals when it is ready to read or write data? It does so by sending out appropriate timing signals called control signals before it transfers data.

The steps in performing these MPU operations can be summarized as follows (not necessarily in the order listed in every operation):

1. Identify the memory location or the peripheral with its address.

2. Provide timing or synchronization signal.

3. Transfer binary data.

Therefore, the MPU requires three sets of communication lines called buses: the first group of lines, called the address bus, to identify the memory location; the second group, called the data bus, to transfer data; and the third group, called the control lines, for timing signals. In the previous chapter (Figure 1.3), all these different signal lines were grouped together and shown as the system bus. Now we. shall describe them individually.

ADDRESSBUS

As mentioned earlier, the MPU identifies each peripheral or memory location with a binary address. Now the question is: how large is this address? The answer depends upon the internal design of the microprocessor and available pins on a chip; it can be eight, 16, 20, or more bits. If the address size is 4 bits, the microprocessor can identify 16 (24) different memory locations. The addressing is simply a numbering scheme to identify memory registers. For example, a two-digit decimal numbering scheme can identify only 100 items, from 00 to 99. On the other hand, a four-digit numbering scheme can identify 10,000 items, from 0000

to 9999. Thus, the number of bits (address lines) used for addressing by the MPU clearly determines the number of memory registers it can identify.

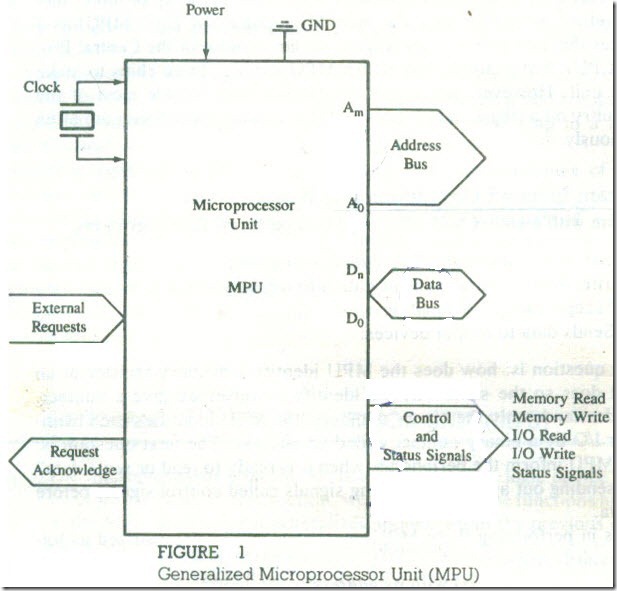

FIGURE 1 Generalized Microprocessor Unit (MPU)

Figure 1 shows one group of lines as the address bus for our generalized MPU. The arrow suggests that these lines are unidirectional-the signals flow . from the MPU to peripherals because only the MPU sends out an address. The address lines are generally identified as A0 to Am where m indicates the most significant address bit. Typically, earlier microprocessors such as the 8085. the Z80, and the 6800 have 16 address lines which are capable of addressing 65.5 ‘0 (2Ih) memory locations, commonly known as 64K memory. However, recent microprocessors such as the 8086 have 20 address lines, and the 68000 has 23 address lines.

DATA BUS

The second group of lines shown in Figure 2 is the data bus. These lines are used to transfer data and are bidirectional-data can flow either direction. These lines are identified as D0 to Dn where n signifies the most significant bit (MSB) of the data bus. Again, the size of the data bus determines how large a binary number can be transferred and processed at a time and thus influences the microprocessor architecture considerably. The 8085, the Z80, and the 6800 have eight data lines and thus are called S-bit microprocessors .On the other hand. the 8086. the 80286, the Z8oo0. and the 68000 have 16 data lines and are called 16-bit microprocessors.

CONTROL SIGNALS (MPU INITIATED)

These are individual signal lines generated by the MPU to indicate its operations. The MPU generates a specific signal for each of its four operations-Memory Read. Memory Write, 1/0 Read, and I/O Write. These are timing signals that are used to enable, or activate, peripherals. For example, to fetch (or read) an instruction from a memory location, the MPU sends a timing pulse called Memory Read to enable the memory chip.

Externally Initiated Operations

There are various occasions when ongoing MPU operations need to be interrupted. For the MPU we are designing, we can classify these types of external interruptions or delays into four categories.

· Reset: Start again from the beginning. For example, if we are using a microprocessor as a timer, we should be able to reset the timer after each operation or in the middle of an operation and start again.

· Interrupt: Stop the ongoing process temporarily; do something now that is more critical, and then go back to the original process. For example. we should be able to stop printing temporarily and read data from a keyboard; then. when the MPU finishes reading that data, it can go back to printing.

· Wait: When memory response time is too slow to respond to the speed of the MPU, this signal can be used to delay the MPU operations.

· Bus Request: When the MPU operations are too slow compared to the speed of a peripheral, the peripheral can request the use of the buses. For example. when large amounts of data are to be transferred to memory, Direct Memory Access (DMA) controllers can transfer data much faster than can the MPU.

In our generalized MPU model (Figure 2). these externally initiated signals are shown as External Requests. To indicate its response to some of these external requests, the MPU needs additional signal lines shown as Request Acknowledge.

Clock Signals and Power

The MPU can be viewed as a complex timer. The timing is very critical in all its operations. The bits of a binary instruction are associated with the micro programs inside the chip; when the MPU executes an instruction, it releases a series of micro programs at precise rime intervals. Therefore, the MPU needs circuits that generate clock signals. In addition, it needs electrical power to run all the operations.

Figure 1 shows all the signals necessary for our generalized MPU. Presently, because of LSI technology, most of the MPU requirements can be satisfied by single-chip microprocessors with slight variations. For example, the Z80 microprocessor has all the signals of the MPU except c1ock-generatlng circuitry. and some of its control signals need to be logically ANDed to generate the specific control signals shown in Figure 8 However. the present microprocessors include all the data processing and timing circuitry on one chip; therefore, they can be viewed almost as MPUs. Now we shall examine what is inside the microprocessor to understand how it processes data.