Chapter 2: Serial Interface—The COM Port

Overview

The universal peripheral serial interface—the COM port (Communications Port)—has been present in PCs since the first models. This port provides asynchronous[1] data transfer employing the RS-232C standard. COM ports are implemented using Universal Asynchronous Receiver-Transmitter (UART) ICs compatible with the i8250/16450/16550 software model. They each occupy eight adjacent 8-bit registers in the I/O addressing space and can have the standard base addresses: 3F8h (COM1), 2F8h (COM2), 3E8h (COM3), and 2E8h (COM4). Ports may generate hardware interrupts IRQ4 (usually used for COM1 and COM3) and IRQ3 (used for COM2 and COM4). On the hardware side, ports have lines for serial data transmission and receiving. They also have a set of lines for the control- and status-monitoring signals that comply with the RS-232C standard. COM ports have external connectors, DB25P or DB9P male plugs, on the computer back panel (see Section 2.1). A distinguishing feature of the interface is it uses “non-TTL” signals: all the external port signals are bipolar. There is no galvanic decoupling; the circuit ground of the attached device is connected to the computer’s circuit ground. The data transmission rate may reach 115,200 bps.

Up to four COM1-COM4 serial ports can be supported at the BIOS level on a computer. (AT-class machines usually have two ports.) BIOS Int14h service provides port initialization, character input and output (without using interrupts), and status polling. Using Int14h standard calls, data transmission rate can be programmed to fall in the 110-9,600 bps range (less than the actual port capabilities). To increase the throughput, application software interaction with the port on the register level is widely used. For this, COM port hardware must be compatible with the i8250/1645/16550 software model.

The port’s name indicates its main purpose: to connect equipment (such as a modem) that allows computer to communicate with other computers, networks, and peripheral devices. Peripheral devices with serial interfaces—printers, plotters, etc.—can be connected directly to the port. The COM port is widely used to connect a mouse and to directly link two computers. The COM port also is used to connect electronic keys to a computer.

Practically all modern motherboards (starting as far back as the PCI boards for the x486 processors) have two built-in adapters for the COM port. One of the ports also may be used for wireless infrared communications with peripheral devices (IrDA). ISA cards can have a couple of COM ports. On these, COM ports most frequently neighbor the LPT port and the disk interface controllers (FDC+IDE). If a greater number of interfaces is needed, additional special-purpose adapters, called multiplexors, may be installed. These are rather expensive cards; they usually have 4, 8, 12, or even 16 ports. Providing such a great number of connectors from the PC’s back panel is problematic. Therefore, multiplexors are usually equipped with an external connector block, which also contains electronics, connected to the adapter through a cable with multicontact connectors. Multiplexors are not supported by BIOS.

The “classic” COM port only allowed software-controlled data transfer. The processor needed to execute several instructions to transfer each byte. Modern ports have several FIFO data buffers and allow transfers via the DMA channel. This significantly decreases the CPU workload, an especially important factor at high transfer rates.

[1]Only special adapters, such as SDLC or V.35, support synchronous transfer on a PC.

2.1 The RS-232C Interface

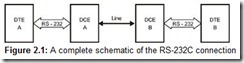

The RS-232C interface is intended to connect data transmitting or receiving equipment (DTE: Data Terminal Equipment) to the terminal data channels equipment (DCE: Data Communication Equipment). The DTE role can be played by a computer, a printer, a plotter, or other peripheral equipment. The DCE role is usually played by a modem. The final purpose of the connection is to link two data transmitting devices. A complete schematic of the connection is shown in Fig. 2.1. The interface makes it possible to exclude the remote communications channel along with a pair of DCE devices by connecting two devices directly using a null-modem cable (Fig. 2.2).

The standard specifies the control signals of the interface, data transfer, electrical interface, and connector types. The standard provides for asynchronous and synchronous transfer modes, but the COM ports only support asynchronous mode. Functionally the RS-232C is equivalent to the CCITT/ITU V.24/V.28 standards, but has different signal names.

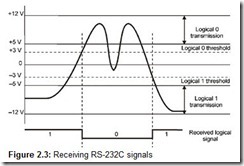

The RS-232C standard defines asymmetrical transmitters and receivers in which the signal is transmitted relative to the common wire: the circuit ground (symmetrical differential signals are used in other interfaces, such as RS-422). The interface does not provide for the galvanic decoupling of the devices. Voltages in the-12 V to −3 V range correspond to the logical one (MARK state) at the receiver data input (the RxD signal). Voltages in the +3 V to +12 V range correspond to the logical zero (SPACE state). For the control signal inputs, voltages in the +3 V to +12 V range correspond to the ON state, and in the −12 V to −3 V range, to the OFF state. The −3 V to +3 V range is the dead zone, providing receiver hysteresis: line state is considered to be changed only after crossing the threshold (Fig. 2.3). Signal levels on the transmitters’ outputs shall be in the −12 V to −5 V and in the +5 V to +12 V ranges. The potential difference between the signal grounds (SG) of the connected devices shall be less than 2 V, a greater potential difference may cause erroneous signal reception. Make note that the TTL level signals (on the inputs and outputs of the UART ICs) are sent in the straight coding for the TxD and RxD lines and in inverted for all the others.

The interface supposes the connected devices to have protective grounds if they are both powered from AC line and have line filters.

Caution Connecting and disconnecting interface cables of devices with individual power supplies must be done with their power supplies turned off. Otherwise, the difference of the devices’ unbalanced voltages at the moment of establishing connection may be applied to the output or, which is more dangerous, to the input circuits of the interface and damage the ICs.

The RS-232C standard regulates the types of connectors used.

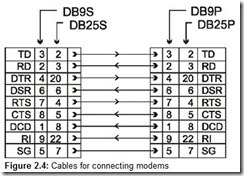

It is customary to have DTE devices (including the COM ports) equipped with DB-25P or with more compact DB-9P male plug connectors. The 9-pin connectors do not have contacts for the additional signals that are needed for the synchronous mode (in most of the 25-pin connectors, these contacts are not used).

DCE devices (modems) are equipped with female DB-25S or DB-9S connectors.

This rule assumes that the DCE connectors may be connected to the DTE connectors either directly or via “straight” adapter cables with a female plug on one end and a male on the other whose contacts are connected in the “one-to-one” fashion. There also are 9-pin connector to 25-pin connector adapter cables (Fig. 2.4).

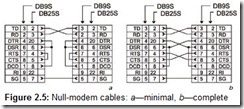

If DTE equipment is connected without using modems, then their connectors (males) are interconnected using a null-modem cable (Zero-modem, or Z-modem). Such cable has female plugs on both ends whose contacts are cross-wired as shown in one of the schematics in Fig. 2.5.

If a DTE piece of equipment has a female plug installed, it is almost 100 percent chance that it should be connected to another device by a straight cable, similar to one used to connect a modem. Female connectors are usually installed in those devices that are not intended to be connected via a modem.

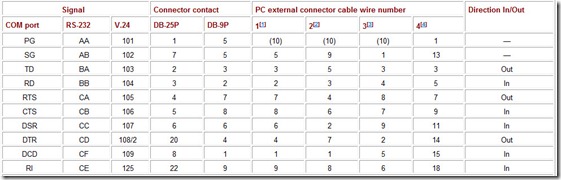

Table 2.1 shows functions of the COM port (and of any other DTE type data transfer equipment) connector contacts. DB-25S connector contacts are defined by the EIA/TIA-232-E standard and DB-9S connector contacts are defined by the EIA/TIA-574 standard. Modems (DCE) have the same circuit and contact names, but the functions of their signals (input/output) are reversed.

[1]Ribbon cable for 8-bit multicards

[2]Ribbon cable for 16-bit multicards and for the built-in ports

[3]A version of a ribbon cable for the built-in ports

[4]Wide ribbon cable for the 25-contact connector

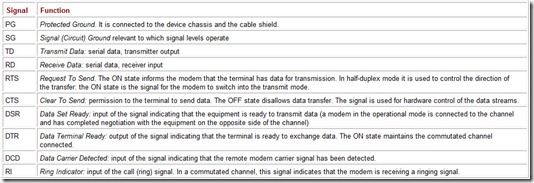

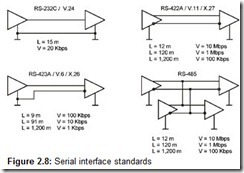

We will consider the asynchronous mode subset of the RS-232C signals from the standpoint of a PC COM port. For the sake of convenience, we will use the terminology mnemonics accepted in the descriptions of the COM ports and most of the equipment (it differs from the faceless RS-232 and V.24 cable notations). Remember that the active, ON, state of the control signals and the logical zero of the transmitted data are represented by the positive potential (above +3 V) of the interface, and the OFF state and logical one are represented by the negative potential (below −3 V). Table 2.2 shows the functions of the interface signals. Fig. 2.6 illustrates normal sequence of the control signals for the case of a modem connected to the COM port.

Table 2.2: Functions of the RS-232C Interface Signals

-

1—The PC indicates that it wants to use the modem by setting the DTR.

-

2—The modem signals that it is ready and has established connection by setting the DSR signal.

-

3—By setting the RTS signal, the computer asks a permission to transmit and informs the modem that it is ready to receive data.

-

4—By setting the CTS signal, the modem informs that it is ready to receive data from the computer and to send them onto the line.

-

5—By clearing the CTS signal, the modem indicates that it cannot continue to receive data (for example, its buffer is filled up) and that the computer has to suspend sending data.

-

6—By the CTS signal, the modem gives the computer permission to resume transmitting data (room in the buffer has become available).

-

7—Clearing of the RTS signal may mean either that the computer’s buffer has filled up (the modem has to suspend sending data to the computer) or that the computer has no data to send to the modem. In such case, the modem usually stops transferring data to the computer.

-

8—The modem acknowledges clearing of the RTS signal by clearing the CTS signal.

-

9—To resume sending data, the computer sets the RTS signal again.

-

10—The modem acknowledges its being ready.

-

11—The computer indicates that the exchange has been competed.

-

12—The modem answers by an acknowledgment.

-

13—The computer clears the DTR signal, which usually is a signal to break the connection (“to hang up”).

-

14—By clearing the DSR signal, the modem indicates that the connection has been broken.

Examining this sequence, the purpose of the DTR/DSR and RTS/CTS connections in null-modem cables becomes clear.

2.2 Related Interfaces and Level Converters

Bipolar RS-232C signals are not always used in serial interface. Their use is inconvenient, e.g., because of having to use bipolar power supplies for transceivers. The ICs themselves of the above-described UART transceivers work with the TTL/CMOS logic signals. The same kinds of signals are used in the interfaces of various devices. For example, TTL/CMOS signals are used in the service ports of hard drives, mobile phones (but of very low levels) and in various other devices. Many devices (including pocket PCs and mobile phones) have low voltage level logic external serial interfaces. Of course, regular logic signals don’t have such high noise resistance as the RS-232C, but neither is this always needed.

For interconversion between the RS-232C and CMOS logic levels, there are special buffer ICs for receivers (with hysteresis) and transmitters of bipolar signals. They are the first to become victims of the “pyrotechnical” effects when the rules for grounding and connecting equipment are not observed. Earlier they were often installed in sockets, which made their replacement easier. Fig. 2.7 shows pinouts of some popular RS-232C signal generating ICs. Often buffer circuits are included right into the interface LSI ICs. This lowers the price of the device, saves the card’s real estate, but in case of an accident turns into great financial loses. Damaging interface ICs by short-circuiting them is unlikely: short circuit current of the transmitters usually does not exceed 20 mA.

Converters manufactured by companies Maxim and Sypex are often used in special adapter cables. They are practical in that they contain both receivers and transmitters. From the wide selection of these converters, it is easy to pick one that suits the number of receivers and transmitters needed, as well as the required power supply voltage characteristics (unipolar, bipolar, low-voltage).

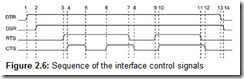

When a great noise resistance is required (for high speed or long distance transmissions), different electrical versions of serial interface are used: RS-422A (V.11, X.27), RS-423A (V.10, X.26), and RS-485. Fig. 2.8 shows some schematics for connecting receivers and transmitters along with the line length limits (L) and the maximum transfer rate (V). Asymmetrical RS-232C and RS-423A interface lines have the lowest resistibility against the common-mode interference, although the differential input of an RS-423A receiver allows alleviating the situation to some degree. The best parameters have the RS-422A and RS-485 interfaces working on symmetrical communication lines. They use differential transceivers with a separate (twisted) wire pair for each signal loop.

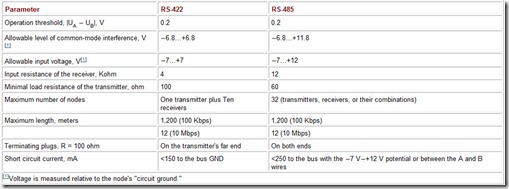

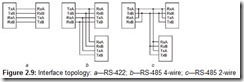

The EIA-RS-422 (ITU-T V.11, X.27) and EIA-RS-485 (ISO 8482) interfaces use symmetrical signal transmission and allow both point-to-point and bus topologies of connections. The information carrier in them is the potential difference between conductors A and B. Potential difference at the receiver’s input UA − UB > 0.2 V (A is more positive than B) corresponds to the OFF (space) state, and UA − UB < −0.2 V (A is more negative than B) corresponds to the ON (mark) state. The |UA − UB| ≤ 0.2 V range is the dead zone (hysteresis), providing protection from interferences. At the transmitter outputs, UA and UB signals usually switch between 0 V and +5 V levels (CMOS) or + 1 V and +4 V (TTL). Differential output voltage must fall within the 1.5 V to 5 V range. The output resistance of transmitter is 100 ohm. The interfaces are electrically compatible, although there are some differences in their restrictions. The principal difference of the RS-485 transmitters is their capability to switch into the high impedance state. The RS-422/485 transmitters are compatible with the RS-423 receivers. Table 2.3 gives main parameters of the interfaces. Connection topologies are shown in Fig. 2.9.

Table 2.3: RS-422 and RS-485 Interface Parameters

To increase number of nodes, input resistance of receivers may be raised, but this leads to a drop in the permissible transmission rate or a decrease of the potential maximum transmission distance. The maximum transmission rate over the short distances (up to 10 meters) is limited by the transmitter’s operating speed (frequencies of up to 25 MHz may be reached). Over the mid-distances the limitation is determined by the cable’s capacitance (at 1,200 bps—25 nF, at 9,600 bps—30 nF, at 115 Kbps—250 pF). The maximum distance is limited by the loop’s DC resistance.

There are two types of the RS-485 interface: a 2-wire and a 4-wire. The 4-wire type (Fig. 2.9, b) sets out a master node whose transmitter services receivers of the rest of the nodes. The master node transmitter is always active: it does not need to switch into the high impedance state. Transmitters of the rest (slave) nodes must have tri-state outputs, they are connected by the common bus to the receiver of the master node. In the 2-wire type (Fig. 2.9, c), all nodes are equal.

In the simplest case—point-to-point connection—the RS-485 and RS-422 interfaces are equivalent and the high impedance state is not used.

To maintain the RS-485 bus quiescent state when there are no active transmitters present, active terminator plugs that “stretch” the potential of the conductors are placed on the line. In the quiescent state, wire B must have more positive potential than wire A.

With the multipoint connection, a method to access the transmission environment must be arranged. The most frequently method used is polling: one device designated master polls slave devices their readiness to transmit. Handing over the access right from one device to another is possible pursuant to the established protocol. Random access methods (analogous to Ethernet) are also sometimes used.

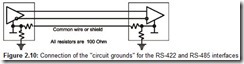

Differential input of the interfaces provides protection against interference, but here circuit grounds of the devices must be connected among themselves and to the ground bus. To interconnect the devices, a third wire of the interface is used (the cable shield may serve this purpose too). To prevent from flowing through the third wire too great a current equalizing the ground potentials, resistors are placed into its circuit (Fig. 2.10).

The RS-422 interface is often used to connect peripheral devices (such as printers). The RS-485 interface is a popular means of connecting industrial automation equipment.

To transmit a signal, the “current loop” interface instead of voltage uses current in the 2-wire line connecting receiver and transmitter. Current flow of 20 mA corresponds to logical one, and absence of current flow corresponds to logical zero. This kind of signal representation in the above-described format of asynchronous transmission allows detecting line breaks: the receiver will notice the missing stop-bit (line break acts as a constant logical zero).

The current loop usually presupposes galvanic decoupling of the receiver’s input circuits from the rest of the circuit. Here, the transmitter is the current source in the loop (this version is called active transmitter). Powering from the receiver also is possible (active receiver), here transmitter’s output key may be galvanically decoupled from the rest of the transmitter’s circuit. Simplified versions without galvanic decoupling also exist, but this is a degenerated case of the interface. Make note, the MIDI interface (see Section 7.5.3) is not compatible with the “classic” current loop.

Galvanically decoupled current loop allows transmitting signals over the distance of up to several kilometers, but at low transfer rates (rates over 19,200 bps are not used, and when the distance is measured in kilometers, the maximum speed is 9,600 bps and lower). The maximum distance is determined by the resistance of the wire pair and by the noise level. Because the interface requires one wire pair for each signal, usually only two signals of the serial interface are used (4-wire line). In the case of the bidirectional exchange, only signals to send and receive data are used; to flow control, the software XON/XOFF method is used. If there is no need for bidirectional exchange, then one wire pair is used to transmit data and the other to flow control with either the CTS signal (hardware protocol) or the reverse data line (software protocol). Using appropriate software, one current loop may be utilized to organize half-duplex bidirectional communication of two devices. Here each receiver “hears” both the opposite side transmitter’s signals and the signals of its own transmitter. The communication protocols simply consider them as echo signals. For error-free reception, transmitters must operate in turns.

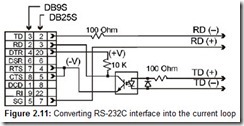

The current loop allows employment of dedicated physical (leased) lines without modems but at low transfer rates. Sometimes the current loop is used to connect RS-232C interface terminals if the design length of the interface is too short or galvanic decoupling is needed. It is not difficult to convert RS-232C signals into the current loop. Fig. 2.11 shows a very simple schematic diagram of a converter for connecting a terminal. The interface power supply is used to obtain the bipolar signal needed for the input circuits of the COM port. The schematics may be enhanced to provide overload protection for the optocouplers and to improve the shape of the voltage signals. The maximum transfer rate is determined by the operating speed of the used optocouplers (rate of 9,600 bps is achieved practically with any optocouplers).

2.3 The Asynchronous Mode

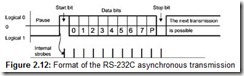

The asynchronous mode of serial transfer is byte-oriented (character-oriented): the minimal transferred unit of information is one byte (one character). Fig. 2.12 illustrates the format of the byte transmission. Transmission of each byte is set off by the start bit, which signals the start of the transmission to the receiver. It is followed by the data bits and, possibly, the parity bit. The transmission ends by the stop bit, which ensures there is a pause between transmissions. The start bit of the next byte is sent at any time after the previous byte’s stop bit, i.e., it is possible to have pauses of any length between transmissions. The start bit, which always has strictly defined value (that of a logical zero), provides a simple method to synchronize the receiver by the signal from the transmitter. It is understood that both the receiver and the transmitter are working at the same transfer rate. The internal synchronizing generator of the receiver uses a reference frequency dividing counter, which is set to zero at the moment it receives the beginning of the start bit. This counter generates internal strobes by which the receiver latches in the following bits. Ideally, the strobe pulses are located in the center of the bit intervals, which allows receiving data even when the receiver and the transmitter transfer rates are slightly unmatched. It is obvious that when transmitting eight data bits, one parity bit, and one stop bit, the permissible frequency tolerance, at which data will be detected correctly, must not exceed five percent. Taking into account phase distortions and the quantized nature of the internal synchronization counter operation, in reality even smaller frequency tolerance is allowed. The smaller is the division factor of the internal reference frequency generator (the higher the transmission frequency), the higher is the inaccuracy of the strobe placement with respect to the center of the bit interval, thus necessitating stricter requirements to the frequency matching.

The higher is the transmission frequency, the more distorted fronts affect the phase of the received signal. Combination of these factors results in heightening the requirements to the receiver and transmitter frequency matching as the transfer rate increases.

The format of the asynchronous transmission allows detecting potential transmission errors.

-

If a logic transition signaling start of transmission has been received, but at the start bit strobe logical one has been latched, the start bit is considered false and the receiver returns into the wait state. The receiver does not have to report this error.

-

If during time period allocated to the stop bit, logical zero (high) level is discovered, a stop bit error is recorded.

-

If the parity check is employed, then after sending data bits, a parity check bit is sent. This bit complements the number of data bits logical ones to even or odd, depending on the prior agreement. An error is recorded if a byte with an erroneous parity bit value is received.

-

The format check allows detecting line breaks: as a rule, the receiver “sees” logical zero if there is a line break. This logical zero is first treated as a start bit and data’s zero bits, but then the stop bit check is triggered.

A set of standard transfer rates is adopted for the asynchronous mode: 50, 75, 110, 150, 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600, and 115200 bits per second (bps). Sometimes, term “baud” is used instead of the “bps”, but when considering transmitting of binary data, this is incorrect. Bauds are used to measure the frequency of the line state changes, but when non-binary coding method is used (which is widely employed in modern modems) in the communication channel, the bit rate transfer (bps) and the frequency of the signal change (baudrate) may differ by several times.

The number of data bits can be 5, 6, 7, or 8 (5- and 6-bit formats are seldom used). The number of stop bits can be 1, 1.5, or 2 (one-and-a-half bit denotes only the length of the stop interval).

2.4 Data Flow Control

Two types of protocol may be used to control data flow: hardware and software. Sometimes, the flow control is confused with handshaking or acknowledgement. Handshaking means negotiating with the partner every elementary step of the protocol (a good example, signaling transmission protocols of the parallel port in the EPP and ECP modes). Acknowledgement is sending a notification of receiving a quantum of data (a byte, a frame, or a packet). Flow control assumes sending notifications as to whether or not the subsequent reception of data is possible. Quite often, flow control is based on the mechanism of handshaking or acknowledgement.

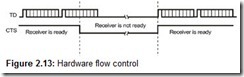

Hardware flow control protocol RTS/CTS uses the CTS signal that allows to stop sending data if the receiver is not ready to receive them (Fig. 2.13). Transmitter “lets go” the next byte only when the CTS line is set. It is impossible to stop the byte whose transmission has already been started by the CTS signal (this ensures the integrity of transmission). Hardware protocol provides the fastest transmitter reaction to the receiver state. ICs of asynchronous transceivers have at least two receiving registers: a shifting register to receive the next packet and a storage register from which the received byte is read. This makes it possible to implement hardware protocol based exchange without loosing data.

The hardware protocol is practical when connecting printers and plotters, if they support it. When two computers are connected directly (without modems), the hardware protocol requires that the RTS and CTS lines were cross-connected.

With a direct connection, the transmitting terminal must have its CTS line switched into the ON state (by having its own RTS and CTS lines interconnected), otherwise the transmitter will not “talk.”

The 8250/16450/16550 transceivers used in IBM PC do not process the CTS signal by the hardware means, but only reflect its state in the MSR register (see Section 2.5). It is left to the BIOS Int14h service to implement the RTS/CTS protocol, and it is not quite correct to call this service a hardware means. Should the program using a COM port interact with the UART on the register level (and not via BIOS), then to support this protocol, it handles the processing of the CTS signal by itself. Several communication programs allow ignoring the CTS signal (if a modem is not used), and they do not require that the CTS input should be connected with the output of even their own RTS signal. There are, however, different transceivers (such as 8251) in which the CTS signal is processed by the hardware means. For them, as well as for the “honest” programs, using the CTS signal at the connectors (and even in the cables) is mandatory.

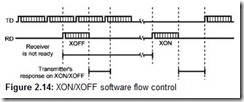

The XON/XOFF software data flow control protocol assumes that a bidirectional data transfer channel is available. The protocol works as follows: if the receiving device discovers some reasons because of which it cannot continue to receive data, it sends an XOFF (13h) byte-symbol via the reverse serial channel. Having received this signal, the opposite device suspends the transmission. When the receiving device becomes ready to receive data again, it sends an XON (11h) character, having received which the opposite device resumes transmission. Comparing to the hardware implemented protocol, the transmitter’s response time to the change in the receiver’s state increases at least for the duration of the signal transmission (XON or XOFF) plus the time it takes the transmitter’s program to react to receiving the character (Fig. 2.14). From this, it follows that only a receiver with an additional buffer for received data and which informs in advance of its inability to receive (still having room in its buffer) can work without data losses.

The advantage of the software flow control consists in not having to transmit the interface control signals: the simplest cable for bidirectional exchange can have only three wires (see Fig. 2.5, a). A shortcoming, besides the necessity to have a buffer and the long response time (lowering the overall efficiency of the channel because of waiting for the XON signal), lies in its being difficult to implement the full-duplex exchange mode. In this case, it is necessary to extract flow control signals from the stream of the received data (as well as to process them), which limits the set of characters that can be transmitted.

Besides these two commonly used standard protocols, which are supported by OS and by most peripheral devices, there are custom protocols requiring special support.

2.5 Asynchronous Transceivers’ ICs (UART)

In the COM ports, conversion of the parallel data into the serial for transmitting and the inverse conversion for receiving is done by dedicated UART (Universal Asynchronous Receiver-Transmitter) ICs. The same ICs generate and process the interface control signals. IBM PC XT/AT COM ports are based on the ICs compatible with the 18250 UART series on the register level: 8250/16450/16550A. This series is an improvement on the original model, intended for increasing the operating speed and lowering power consumption and the processor load during intensive exchange. Make a note that:

-

8250 has design flaws (appearance of false interrupts), which were taken into account in the XT BIOS.

-

8250A: The original design flaws are corrected, but the XT BIOS compatibility is lost as a result; this IC works in some AT models but it cannot be used for the 9,600 bps speeds.

-

8250B: 8250 and 8250A flaws corrected, the XT BIOS compatibility restored by restoring the original interrupt flaw; works in AT under DOS (except for the 9,600 bps speeds).

8250x ICs have low operating speeds with regard to requests from by the system bus. They do now allow their registers be referenced in the consecutive processor bus cycles and software delays must be inserted between the CPU references for these ICs to work correctly.

The following modifications of the UART ICs are used in the AT class computers:

-

16450: high-speed version of the 8250 for AT. It does not have the 8250 flaws, nor full compatibility with the XT BIOS.

-

16550: a development on the 16450. It can use the DMA channel to exchange data. It also has a FIFO buffer, which cannot be used because of the flawed operation.

-

16550A: has functional 16-byte input and output FIFO buffers and DMA capability. It is this chip that should be used in the AT class computers for the 9,600 bps and higher data exchange rates. Most of the modern chipset’s I/O port controller ICs provide compatibility with this chip.

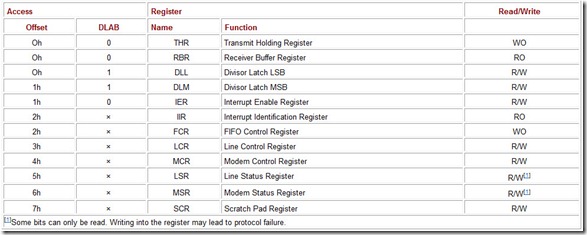

From the programming standpoint, 16550A UART ICs are sets of registers, access to which is determined by the address (offset of the address register relative to the port’s base address) and the value of the DLAB bit (bit 7 of the LCR register). In the I/O addressing space, the IC occupies eight contiguous addresses. Table 2.4 lists the 16550A UART registers and their access methods. 8250 ICs differ in that they do not have FCR register and all of the FIFO and DMA capabilities.

Table 2.4: The 16550A UART Registers

THR: Transmitter Holding Register (write only). Data written into the register are sent into the output transfer shift register (when it becomes available), from which they are placed onto the output TXD signal. Bit 0 (the lowest) is transmitted (and received) first. If a package is less than eight bits long, the high order bits are ignored.

PBR: Receiver Buffer Register (read only). Serial data (RXD) received by the receiver shift register are placed into the RBR register, from where the CPU can read them out. An overflow error occurs if the byte has not been read out of the register by the time the next byte is received. If a package is less than eight bits long, the high order bits have zero values.

DLL: frequency Divisor Low byte register

DLM: frequency Divisor high byte register. The divisor is calculated using the formula D = 115200/V, where V is the transfer rate in bps. The input synchronizing frequency of 1.8432 MHz is divided by the specified coefficient, which gives sixteen-fold data transfer frequency, used by UART.

IER: Interrupt Enable Register. A bit’s value of logical one enables interrupts from the corresponding source.

-

Bits [7:4]=0: not used

-

Bit 3—Mod_IE: upon a modem status change (any of the CTS, DSR, RI, or DCD lines)

-

Bit 2—RxL_IE: upon a line break or error

-

Bit 1—TxD_IE: upon the end-of transmission

-

Bit 0—R×D_IE: upon receiving a character (a timeout interrupt in the FIFO mode)

IIR: Interrupt Identification and FIFO status indicator Register (read only). To simplify software analysis, UART organizes internal interrupts in a four-level priority system. The order of priorities (in descending order) is: line status, receiving a character, emptying of the transmitter register, modem status. When an interrupt condition develops, UART points to the source with the highest priority until it is cleared by an appropriate operation. Only after this will it specify the next request source. Functions of the IIR register bits are described below.

-

Bits [7:6]—FIFO mode status:

-

11: 16550A FIFO mode

-

10: 16550 FIFO mode

-

00: regular mode

-

-

Bits [5:4]: not used.

-

Bit 3: reception timeout interrupt in the FIFO mode (buffer has data to read).

-

Bits [2:1]: cause of the highest priority interrupt (in regular, non-FIFO mode):

-

11: line error/break. Reset is done by reading the line status register.

-

10: a character has been received. Reset is done by reading data.

-

01: a character has been sent (THR register is empty). Reset is done by writing data.

-

00: modem status has changed. Reset is done by reading modem status register.

-

-

Bit 0: indication of a pending interrupt request (1: no interrupt pending, 0: interrupt pending).

In the FIFO mode, the interrupt cause is identified by the bits [3:1].

-

011: line error/break. Reset is done by reading line status register.

-

010: a character has been received. Reset is done by reading the receiver data register.

-

110: a timeout indicator (during time period four times the time it takes to send or receive a character no character has been transmitted or sent even though the buffer is holding at least one). Reset is done by reading the receiver data register.

-

001: the THR register is empty. Reset is done by writing data.

-

000: modem status change (CTS, DSR, RI, or DCD). Reset is done by reading the MSR register.

FCR: FIFO Control Register (read only). The function of its bits is described below.

-

Bits [7:6]—ITL (Interrupt Trigger Level): FIFO buffer saturation level interrupt threshold:

-

00: 1 byte (by default)

-

01: 4 bytes

-

10: 8 bytes

-

11: 14 bytes

-

-

Bits [5:4]: reserved.

-

Bit 3: DMA operations mode select.

-

Bit 2—RESETTF (Reset Transmitter FIFO): reset transmitter FIFO counter (by writing a logical one; shift register is not reset).

-

Bit 1—RESETTRF (Reset Receiver FIFO): reset receiver FIFO counter (by writing a logical one; shift register is not reset).

-

Bit 0—TRFIFOE (Transmit and Receive FIFO Enable). enabling (by logical one) transmitter and receiver FIFO. Buffers are automatically cleared when modes are changed.

LCR: Line Control Register (setting channel parameters). Functions of the LCR register bits are described below.

-

Bit 7—DLAB (Divisor Latch Access Bit): clock divisor access control.

-

Bit 6—BRCON (Break Control): generating line break (sending zeros) at BRCON = 1.

-

Bit 5—STICPAR (Sticky Parity): forced generation of the parity bit:

-

0: parity check bit is generated according to the output character parity.

-

1: constant parity check bit value: logical zero at EVENPAR = 1 and logical one at EVENPAR = 0.

-

-

Bit 4—EVENPAR (Even Parity select): selecting parity control type: zero for odd parity, one for even parity.

-

Bit 3—PAREN (Parity Enable), enabling parity check bit:

-

1: parity check bit (parity or constant) is enabled.

-

0: parity check bit is disabled.

-

-

Bit 2—STOPB (Stop Bits): number of stop bits:

-

Bits [1:0]—SERIALDB (Serial Data Bits): number of data bits:

-

00: 5 bits

-

01: 6 bits

-

10: 7 bits

-

11: 8 bits

-

MCR: Modem Control Register. A description of the MCR register is given below.

-

Bits [7:5]=0: reserved.

-

Bit 4—LME (Loopback Mode Enable): diagnostics mode enable:

-

0: normal mode

-

1: diagnostics mode

-

-

Bit 3—IE (Interrupt Enable): enabling interrupts (signaled by the external output out2):

-

0: interrupts disabled

-

1: interrupts enabled

-

In the diagnostics mode, it is placed onto the MSR.7 input (DCD is emulated).

-

Bit 2—OUT1C (OUT1 bit Control): control of the output signal 1 (not used); in the diagnostics mode, it is placed on the MSR. 6 input (RI is emulated).

-

Bit 1—RTSC (Request To Send Control): control of the RTS output; in the diagnostics mode, it is placed on the MSR. 4 input (CTS is emulated):

-

0: active (+V)

-

1: inactive (−V)

-

-

Bit 0—DTRC (Data Terminal Ready Control): control of the DTR output; in the diagnostics mode it is placed on the MSR. 5 input (DSR is emulated):

-

0: active (+V)

-

1: inactive (-V)

-

LSR: Line Status Register (transceiver status, to be more exact). Functions of the LSR register bits are described below.

-

Bit 7—FIFOE (FIFO Error status): FIFO mode received data error (buffer has at least one character received with a format, parity, or break error). In non-FIFO mode, it is always set to zero.

-

Bit 6—TEMPT (Transmitter Empty Status): transmitter register is empty (neither the shift register nor the THR or FIFO buffer registers has data to transmit).

-

Bit 5—THRE (Transmitter Holding Register Empty): transmitter register is ready to receive a byte to transmit. In the FIFO mode, indicates that the transmission FIFO buffer is empty. May generate interrupts.

-

Bit 4—BD (Break Detected): line break indicator (the receiver input has been in the logical zero state for no shorter period than it takes to send a character).

-

Bit 3—FE (Framing Error): frame error (incorrect stop bit).

-

Bit 2—PE (Parity Error): parity check bit error (parity or fixed bit).

-

Bit 1—OE (Overrun Error): overfilling (losing a character). If the reception of the next character begins before the previous one has been moved from the shifting register into the buffer or FIFO register, the first character is lost.

-

Bit 0—DR (Receiver Data Ready): received data are ready (in the DHR or FIFO buffer). Reset is done by reading the receiver.

Error indicators—bits [4:1]—are cleared after the LSR register has been read. In the FIFO mode, error indicators are stored in the FIFO buffer together with each character. They are placed into the register (and generate interrupts) at the moment when the character that has been received with errors is at the top of the FIFO (first in line to be read out). In the case of a line break, only the “break” character is placed into the FIFO and the UART waits for the line to be restored and for the next start bit.

MSR: Modem Status Register. Functions of the MSR register bits are described below.

-

Bit 7—DCD (Data Carrier Detect): DCD line status:

-

0: active (+V)

-

1: inactive (−V)

-

-

Bit 6—RI (Ring Indicator): RI line status:

-

0: active (+V)

-

1: inactive (−V)

-

-

Bit 5—DSR (Data Set Ready): DSR line status:

-

0: active (+V)

-

1: inactive (−V)

-

-

Bit 4—CTS (Clear To Send): CTS line status:

-

0: active (+V)

-

1: inactive (−V)

-

-

Bit 3—DDCD (Delta Data Carrier Detect): DCD status change

-

Bit 2—TERI (Trailing Edge Of Ring Indicator): RI line envelope fall-off (end of ring)

-

Bit 1—DDSR (Delta Data Set Ready): DSR state change

-

Bit 0—DCTS (Delta Clear To Send): CTS state change

State change indicators (bits [3:0] are reset by reading the register.

SCR: Scratch (work) Register (8-bit wide). Does not affect the UART operation and is intended for temporary data storage (it is absent in the 8250 IC).

In the diagnostics mode (when LME = 1), an internal loopback “plug” is created inside UART:

-

Transmitter’s output is switched into the logical one state.

-

Receiver’s input is disconnected.

-

Output of the transmitter’s shift register is logically connected to the receiver’s input.

-

DSR, CTS, RI, and DCD inputs are disconnected from the input lines and are internally controlled by the DTRC, RTSC, OUT1C, and IE bits.

-

Outputs of the modem control signals are switched into the passive state (logical zero).

Data transmitted serially are immediately received, which allows to diagnose the internal data channel of the port (including the shift registers) and interrupts servicing, and also to determine the UART’s operational speed.

2.6 System Support of the COM Ports

The COM ports are supported by the BIOS Int14h service, which provides the following functions:

-

Initialization (setting the exchange speed and the transmission format; disabling interrupt sources). It has no effect on the DTR and RTS signals (after hardware reset they are inactive).

-

Send character. DTR and RTS signals are activated, and after the THR register is released, the character being output is placed into it.

-

Receive character. Only the DTR signal is activated (the RTS signal goes into the inactive state), the driver is awaiting to receive a data character.

-

Status poll of the modem and the line (reading the MSR and LSR registers).

Hardware interrupts are not used, input and output readiness wait is limited by the timeout. Readiness can be expeditiously checked by status polling, before an attempt is made to receive or send a character.

During the initial POST testing, BIOS checks for the serial port presence (UART 8250 or compatible registers) at the standard addresses and places the base addresses of the ports it discovers in BIOS Data Area cells 0:0400h, 0:0402h, 0:0404h, and 0:0406h. These cells store the addresses of the ports that have logical names of COM 1 to COM4. Address value of zero means that no port with the given number exists. The constants setting timeouts for the ports are stored in the cells 0:47Ch, 0:47Dh, 0:473Eh, and 0:47Fh.

The discovered ports are initialized into the 2,400 bps exchange rate, seven data bits, even parity, one stop bit. The interface control signals DTR and RTS are switched into the initial state (OFF: negative line level).

2.7 Configuring COM Ports

There may be up to four serial COM1 to COM4 port on a computer; AT class machines typically have two ports. The process of controlling serial ports is split into two stages: initial configuring (Setup) of the port’s hardware and the in-the-process (operational) changes of the work modes by application or system software. Configuring a COM port depends on how the port has been implemented. Ports physically located on an expansion card are configured by jumpers on the card itself. Ports built-in into motherboards are configured by BIOS Setup.

The following port parameters can be configured:

-

Base address, which for the COM1-COM4 ports usually has the values of 3F8h, 2F8h, 3E8h, and 2E8h. During the initialization, BIOS checks the addresses for ports presence exactly in this order and assigns logical names COM1, COM2, COM3, and COM4 to the ports it detects. Ports COM3 and COM4 can have alternate addresses 3E0h, 338h and 2E0h, 238h, respectively. For PS/2, the standard COM3 to COM8 port addresses are 3220h, 3228h, 4220h, 4228h, 5220h, and 5228h, respectively.

-

Interrupt request line used: for COM1 and COM3 lines, IRQ4 or IRQ11 are normally used, for COM2 and COM4: lines IRQ3 or IRQ10. Technically, interrupt numbers may be assigned to the base address (port number) in arbitrary order, but some programs and drivers (such as serial mouse drivers) are programmed to use the standard combinations. Each port that needs a hardware interrupt is assigned a separate line that does not coincide with the interrupt request lines used by the other devices. Interrupts are needed only for those ports to which input devices, UPS, or modems are connected. Only multitasking OSs (not always though) use interrupts for printer or plotter transfer and this scarce resource may be conserved. Also, interrupts are not used when two computers are connected with a null-modem cable. Whether one interrupt request line can be separately used by several ports (or shared with other devices) depends on the hardware connection implementation and the software used. With ports installed on the ISA bus, shared interrupts usually don’t work.

-

DMA channel (for 16450/16550 UART ICs located on the motherboard): enabling DMA and the channel number. DMA is rarely used with COM ports.

-

2.8 COM Port Applications

The COM port is widely used to connect various peripheral and communications equipment, to communicate with various technological equipment, control and monitoring equipment, programmers, in-circuit emulators, and other devices using RS-232C protocol.

Most frequently, COM ports are used to connect pointer devices (mouse, trackball). In this case, the port is used in the serial input mode. A mouse with the serial interface—Serial Mouse—can be connected to any functional port. To match the port and mouse connectors, DB-9S to DB25P or DB-25S to DB-9P adapters may be used. Mouse needs interrupt IRQ4 for COM1 and IRQ3 for COM2. The fact that in order to use mouse, COM1 port must use IRQ4 interrupt is a peculiarity of its driver, but for the user the important part is the fact of the limitation itself. Every event—mouse movement or pressing/releasing a button—is binary coded and sent through the RS-232C interface. Asynchronous transmission is used; bipolar power source is supplied by the interface control lines.

To connect external modems, a DTE to DCE cable with a complete set of wires (nine) is used. Its schematic diagram is given in Fig. 2.4. The same type of cable is used to match the connectors (by the number of contacts); for this, 9-to-25 mouse adapters also can be used. Communications software normally uses interrupts, but here there is a freedom of choice in selecting the port number (address) and the interrupt line. If operations at the transfer rates of 9,600 bps or higher are planned, then the COM port must be implemented using 16550A or a compatible UART IC. The extent to which the FIFO buffers and DMA channel operational features are available depends on the communications software used.

To connect two computers located a short distance apart from each other, their COM ports also can be directly connected with a null-modem cable. (See Fig. 2.5). Programs like Norton Commander or MS-DOS Interlink allow exchanging files at the transfer rates up to 115.2 Kbps without making use of the hardware interrupts. The same connection can also be used by the Lantastic net package, which offers more advanced features, as well as by the OS Windows services.

COM port allows connecting electronic keys (Security Devices) intended for protecting software from unlicensed use. These devices can be “transparent” (allowing to use the port to connect other equipment) as well as totally taking over the port.

Provided with a proper software support, COM port allows to turn a PC into a terminal, emulating the command set of the common specialized terminals (VT-52, VT-100, etc.) The simplest terminal can be obtained by interconnecting functions of BIOS COM port services (Int14h), teletype output (Int10h), and the keyboard input (Int16h). Such terminal, however, will only work at low exchange rates (if, of course, it is not done on a Pentium), since, although BIOS functions are universal, they are not very fast.

COM port also can be used as a bidirectional interface with three software-controlled output (TD, DTR, and RTS) and four input (CTS, DSR, DCD, and RI) lines utilizing bipolar signals. They may be used, for example, to programmatically implement synchronous serial interfaces (see Section 10.5). During the AT-286 times, there existed a schematic of a one-bit broad-impulse converter allowing to record an audio signal on the PC using an input line of the COM port. Playing this record back through the PC speaker made it possible to reproduce speech.

2.9 The COM Port and PnP

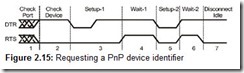

Modern peripheral devices connected to the COM port can support the PnP specification. The main task of the OS lies in identifying the device being connected. For this, a simple protocol that can be implemented on any COM port by purely software means has been developed. Fig. 2.15 illustrates this protocol.

-

Check Port: a check for the port being occupied by an application. If the port is free, it is initialized into the idle state with the line states being DTR=ON, RTS=OFF, TXD=Mark. If the port is busy, the further protocol steps are not carried out.

-

Check Device: a check for device presence. For a certain period of time (0.2 sec), the system waits for the DSR signal to appear, which would indicate that that there is device connected to the port. In the simplest case, the device will have a DTR—DSR jumper at the connector that provides the said response. If a device is detected, the subsequent protocol steps are carried out (the DTR and RTS control signals are manipulated in order to receive serial data information from the device). If there is no answer, the protocol switches into the Disconnect Idle state. In this case, operating systems that support dynamic configuring periodically execute the preceding sequence, trying to see if any new devices have been connected.

-

Setup-1. The port is programmed into the 1,200 bps, seven data bits, no parity, one stop-bit mode, and the DTR signal is held low for 0.2 sec. Then the DTR is set to logical one, and 0.2 sec later the RTS is also set to logical one.

-

Wait-1. The operating system waits 0.2 seconds for the first character to arrive from the device. When it arrives, the system begins receiving the identifier. If during this time the character does not arrive, the operating system makes a second setup attempt (see 5), which differs somewhat from the first one.

-

Setup-2. Both the DTR and RTS, signals are set to logical zero for 0.2 seconds, after which they both are set to logical one.

-

Wait-2. The operating system waits for 0.2 seconds for the first character to arrive from the device, and when it arrives begins receiving the identifier. If the character does not come during this time, then depending on the status of the DSR signal, either the Verify Disconnect (if DSR=0) is performed or Connect Idle (if DSR=1) state is entered.

-

In the Connect Idle standby state, the DTR signal is set to logical one and the RTS signal to logical zero, the port is programmed to 300 bps, seven data bits, no parity, one stop bit mode. If during this state DSR=0 is discovered, the OS should inform that the device has been disconnected.

Receiving the device identifier one character at a time has timeout limitation of 0.2 sec per character as well as the overall time limit of 2.2 sec, which allows receiving a string up to 256 characters long. The PnP identifier string must have the start and end markers (28h or 08h and 29h or 09h, respectively), between which the body of the identifier in the standardized format is placed. Up to sixteen characters not related to the PnP identifier can go before the start marker. If during the first 0.2 sec of character wait (step 4 or 6) the start marker has not arrived, or the timeout has been triggered but the end marker has not been received, or a character has been received with errors, a switch into the Connect Idle state is made. If a valid identifier string has been received, it is handed over to the OS.

To verify disconnection (Verify Disconnect), the DTR is set to logical one, the RTS to logical zero, and every five seconds the state of the DSR signal is checked. When DSR=1, a switch into the Connect Idle state is performed (see list item 7), and when DSR=0, a switch into the Disconnect Idle state is done, in which the system can periodically poll the DSR signal to check if a device has been connected.

The described mechanism has been developed by Microsoft company with considerations for compatibility with devices not belonging to the PnP type: it ensures that it will be impossible to disable them and provides for the system stability to the messages which are not PnP identifiers. For example, a conventional Microsoft Mouse upon getting powered up from the interface will respond with the ASCII character “M” (a three-button mouse—with a string “M3”).

2.10 COM Ports Malfunctions and Their Troubleshooting

COM port malfunctions occur (become apparent) during installation of new ports or unsuccessful connection of external devices.

2.10.1 Configuration Testing

Troubleshooting the serial ports (like the parallel ones) is started with checking whether the system identifies them. List of addresses of the installed ports usually appears in the table that BIOS displays before loading the OS. This list also can be viewed with the help of diagnostic programs or directly in the BIOS Data Area with the help of a debugger.

If BIOS detects fewer ports than are physically installed, it means that two ports have been assigned the same address or an incorrect address for one of the ports has been specified. Problems may turn up with the COM3 and COM4 port addresses: not all BIOS versions will look for ports at the alternative addresses 3E0h, 338h, 2E0h, and 238h; sometimes, the search is not done at the addresses 3E8h and 2E8h. The way in which the identified ports are shown in the list may be confusing: if two ports with addresses 3F8h and 3E8h are installed, in the list they will be referred to as COM1 and COM2 and these names can be used to reference them. However, the same ports may be referred to in the list as COM1 and COM3 (since 3E8h is the standard COM3 port address). But an attempt to reference COM3 port will be unsuccessful, since in this case 3E8h address will be in the BIOS Data Area memory cell 0:402h, which corresponds to the COM2 port, and in the COM3 port memory cell (0:404h) there will be a zero: indicator that no such port is present. You can “explain” to the system where what port is manually using any debugger by inserting correct values of the base addresses into the BIOS Data Area memory cells (you will have to do this every time after rebooting before using the “lost” port). There are diagnostic utilities allowing to find ports (such as PortFinder).

If two ports have been assigned the same address, a diagnostic program can discover port errors only when it is used with an external loopback plug. Software testing of the port without the plug will not show any errors, as in this case the diagnostic mode is activated (see the UART description) and the conflicting (but individually in order) ports will work in parallel, ensuring that the output information matches. In real life, normal functioning of the conflicting ports is not possible. In solving the address conflict you may find it helpful to install ports one by one while observing the addresses that appear in the list.

If only one physical port is installed and BIOS does not find it, the reasons for this are the same as in the case with the LPT port: either it was disabled during the configuration or has failed. The malfunction may be fixed by wiggling the adapter card in and out within the motherboard slot.

When using the COM port, corresponding hardware interrupts are involved: they are used when connecting a modem, a mouse, or other input devices. The reason for these devices not functioning may be incorrect interrupt request settings. Conflicts with other devices, as well as mismatches between the interrupt number and the port address, are possible here.

2.10.2 Functionality Testing

Initial testing of the COM port can be done with the help of a diagnostics program (CheckIt) without using loopback plugs. This testing mode allows checking the UART IC (internal diagnostic mode) and interrupt generation but not the input and output buffer ICs, which are more often the source of troubles. If the test fails, the cause needs to be looked for either in the address/interrupt conflict or in the UART IC itself.

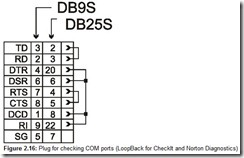

For more reliable testing, it is recommended to use an external plug that is connected to the COM port connector (Fig. 2.16). Unlike in the case with the LPT port, the COM port has more input lines than output, which allows to fully test all the circuits. The plug connects receiver’s input to the transmitter’s output. The mandatory for all plug schematics RTS-CTS jumper allows the transmitter to operate: without it, characters may not be transmitted. The output DTR signal is normally used for checking input DSR, DCD, and RI lines.

If the test using external plug fails, the cause of the problem should be looked for in the external buffers, their power supplies, or the ribbon cables going to the external connectors. Here an oscilloscope or a voltmeter may be useful. The testing sequence may be as follows:

-

Check if the transmitter output circuits have their bipolar power supplies in order (this step is logically the first, but as technically it is the most difficult, it can be put off for the worst case scenario, when you get to feel like replacing the buffer ICs).

-

Check the voltages on the TD, RTS, and DTR outputs: After a hardware reset, there should be a negative potential of about −12 V (at least lower than −5 V) at the TD output. When a character output is attempted, positive voltage must appear on the RTS and DTR outputs and a bipolar pulse series issues from the TD output. If these signals do not appear, it is possible that there has been a mistake when connecting the motherboard to the external connector using the ribbon cable. The most common possibilities are:

-

The ribbon cable is not connected.

-

The ribbon cable is connected incorrectly (the connector is reversed or inserted with a misalignment).

-

Cable layout does not correspond to the motherboard’s connector.

The first two possibilities are investigated by a careful inspection, but the third may require some extra efforts. Table 2.1 shows three known to the author versions of cable layout for 10-wire ribbon cable for COM port connectors; it is possible that for the COM ports built-in into motherboards, other versions exist. In theory, a ribbon cable fitting the connector is supposed to be supplied.

If the problem lies with the wrong cable layout, then these three output signals can be located on the other contacts of the connector (the voltage on the input contacts is very low). If there has been no success locating these signals, evidently the buffer gates have failed.

-

-

After connecting the contacts of the RTS and CTS lines (or having mounted a loopback plug), you should try to output a short file to the COM port (using COPY C:\AUTOEXEC.BAT COM1: command, for example). When the port is operative, this command is successfully executed in a few seconds with a message afterwards to that effect. At this, the voltages on the RTS and DTR outputs should change to negative and on the TD output should appear a packet of bipolar impulses with the amplitude greater than 5 V. If the voltages on the RTS and DTR lines have not changed, then there is a problem with the buffer gates. If negative voltage appears on the RTS output (and on the CTS input) and the COPY command terminates in error, most likely the CTS line receiver is faulty (or, once again, there are some problems with the ribbon cable). If the COPY command executes successfully but there are no changes on the TD output (they can be detected with an analog voltmeter, but their amplitude cannot be evaluated), then the buffer transmitter of the TD signal is at fault.

Replacing receiver and transmitter ICs is significantly easier if they are installed in sockets. Before changing an IC, you should ascertain, using an oscilloscope or voltmeter, that it is faulty.

If the buffering elements are included into the interface LSI IC (which is quite a commonplace nowadays), then such port cannot be repaired (not in the regular settings, anyway). You could try to disable a defective COM port built-in into the motherboard from the BIOS Setup, but the port may have burned out along with the circuitry controlling its disconnection: then it will be a “live corpse” in the I/O and interrupt map. Sometimes, the entire motherboard might be burnt.

Connectors and cables may be sources of malfunctions. Connectors happen to have bad contacts in them, and cables, besides possible breaks, may have inferior frequency characteristics. Cable frequency qualities usually manifest themselves at high transfer rates (56 Kbps or 115 Kbps). If it is necessary to use long cables at high transfer rates, then the data signal carrying wires should be twisted and have a separate circuit ground wire.

2.10.3 Powering Off the Interface, or Why the Mouse Does Not Work

When connecting devices with low power consumption to the COM port, one is tempted to power these devices off the output lines of the interface. If the DTR. or TRS control lines are not being used in their direct capacity, they can be used as a power supply source providing about 12 V. Short circuit current to the circuit ground is limited to the 20 mA level by the buffer IC of the transmitter. At the initialization of the port, these lines go into the OFF state, that is, they provide negative voltage. The TD line in the quiescent state has the logical one on it, so it develops negative voltage on its output. The potentials of these lines can be controlled through the COM port registers (the TD output produces positive voltage if bit BRCON is set). Power also may be taken off the signal lines through rectifying diodes used with accumulating capacitors. Here you ought to take into consideration how long the output signal remains in the needed state (so that the accumulated energy were sufficient).

All manipulators (mice) connected to the COM ports take their bipolar power supplies off the interface lines (+V off the DTR or RTS, −V off the TD). Knowing this, in case your mouse does not function when connected to the port, you should check the voltages on the corresponding contacts of the connector. It happens sometimes that only a particular mouse (model or a piece of equipment) does not work with a particular port, even though other mice work without problems with this port and the same mouse work with other ports. Here the problem may lie in the voltage levels. The standard requires that the port provide no less than 5 V output voltage (absolute value), and if the particular port provides only this minimum, this power is not sufficient to power LEDs (the main energy consumers) on some mice.

The port receives its bipolar power supply through the motherboard from the computer’s power supply. If + 12 V is missing on the power supply’s output, it usually will be manifested by the disks’ being inoperative. Only the devices connected to the COM ports will “notice” the absence of the −12 V. In theory, the power supply monitors these voltages on its output (informing of problems by the Power Good signal, which triggers hardware reset). Simplified power supplies that do not control all their voltages can be encountered. Besides, there is a possibility of bad contacts in the motherboard power supply connector.