Chapter 4: Serial Buses—USB and FireWire

Overview

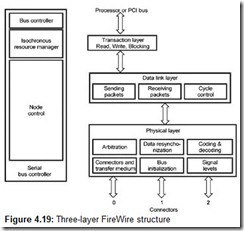

Serial buses make it possible to connect many devices using only one or two pairs of wires. The functional capabilities of these buses are much broader than traditional local network interfaces: USB and FireWire can transfer isochronous audio and video traffic. Serial buses differ fundamentally in their organization from parallel buses. Serial buses have no separate lines for address, control, and data signals: All protocol functions have to be carried out using one or two (in the case of FireWire) pairs of signal wires. This affects how the bus protocol is built, which in serial buses is based on sending packets, or chains of bits ordered in a particular way. In USB technology, the concept of packets and frames has a somewhat different interpretation than in data transfer networks.

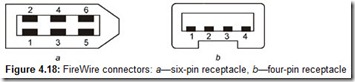

The most popular serial buses are USB and FireWire, although the latter is not yet widely used in PC-compatible computers. FireWire and USB, while having much in common, are nevertheless significantly different technologies. Both buses provide easy connection of a large number of peripheral devices (127 for USB, 63 for FireWire) and allow hot plugging and connection and disconnection. The topological structures of both buses are relatively similar, but FireWire allows greater connection structure freedom and connection lengths. Many devices are equipped with USB hubs, which users often even do not notice. Both buses have lines to supply power to the devices, but the maximum power rating of the FireWire is considerably higher. Both buses support the Plug and Play technology (automatic configuration upon power up or reset) and solve the problem of a shortage of addresses, DMA channels, and interrupt lines. Bandwidth and bus control are different in each bus.

The USB is oriented at peripheral devices connected to PCs. Isochronous USB transfers make it possible to transfer digital audio signals, while the USB 2.0 is capable of carrying video data. All transmissions are centrally controlled, and the PC is the required controlling center located at the root of the tree-like bus structure. Purchasers of modern PCs get a USB controller almost for free as it is built into the chipsets of all contemporary motherboards. Older USB 1.0 motherboards can be provided with USB 2.0 capability by installing a USB 2.0 controller into a PCI slot. The On The Go (OTG) extension allows some peripheral devices (a digital camera, for example) to function as hosts and have devices connected to them (a printer, for example). Several PCs can be directly connected by USB only with the help of auxiliary devices (sometimes, transparently to the user).

The FireWire bus is oriented at consumer electronics devices, which can be joined into a unified home network using it. One or several computers can be connected to this network. The fundamental advantage of the 1394 bus is that is does not require a special bus controller (a computer). Any transmitting device can be assigned a portion of the isochronous traffic bandwidth and begin transmitting upon a signal from an autonomous or remote controller: Receivers will hear its message. If a controller is present, appropriate software can control devices, and implement, for example, a nonlinear video editing studio or provide the necessary multimedia data to all information consumers requiring it.

4.1 Universal Serial Bus: USB

The Universal Serial Bus (USB) is an industry standard of a PC architecture extension that is oriented at integration with telephone and consumer electronics equipment. Version 1.0 was published at the beginning of 1996; most devices support Version 1.1, which came out in the fall of 1998 and fixed the problems that were discovered in the first version. In spring 2000, USB Version 2.0, which expanded the original bandwidth by a factor of 40, was published. Versions 1.0 and 1.1 of the bus provided two data transmission speeds: Full Speed (FS) of 12 Mbps and Low Speed (LS) of 1.5 Mbps. Version 2.0 defines an additional transfer rate: High Speed (HS) of 480 Mbps, which makes it possible to substantially widen the range of devices that can be connected to the bus. Devices supporting all three speeds can be connected and work simultaneously on the same high-speed bus. Employing a repeating hubs bus makes it possible to connect devices up to 25 meters away from the computer. Detailed and up-to-date information on the USB can be found on the Internet at http://www.usb.org. The USB Implementers Forum, Inc. (USB-IF) coordinates USB device development, classification, and standardization.

4.1.1 USB Architecture

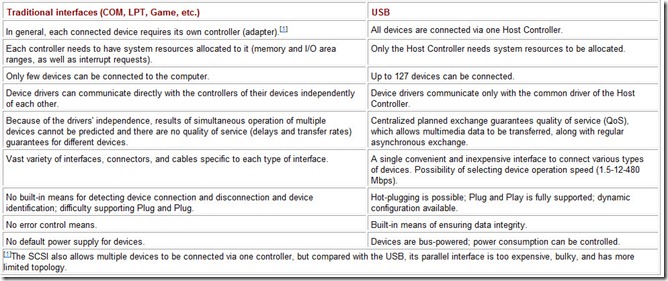

USB provides data exchange between a host-computer and multiple peripheral devices. It is a unified centralized hardware and software system for servicing of multiple devices and multiple application software processes. A host-controller with multiple-level software support links software processes with all devices. This is what makes the USB fundamentally different from traditional peripheral interfaces (LPT, COM, GAME, keyboard, and mouse ports). These interfaces are compared in Table 4.1.

Table 4.1: Comparison of USB and Traditional Interfaces

The USB architecture allows four basic data flow types between the host and peripheral devices:

-

Isochronous transfers—are real-time flow transfers conducted over a dedicated portion of the bus bandwidth and guaranteed to be delivered within a specified time period. At full speed, one 1.023 MBps channel (or two 0.5 MBps channels) can be organized, taking up 70% of the available bus bandwidth (the rest can be filled by less bulky channels). At high speed, one channel of up to 24 MBps (192 Mbps) can be obtained. Data are not guaranteed to be delivered intact: Corrupted data are not retransmitted, invalid packets are ignored. The USB interface allows establishment of synchronous connections between devices and application programs using isochronous transfers. Isochronous transfers are used for data stream devices such as video cameras, digital audio devices (USB speakers, microphone), and devices to record and playback audio and video (CD and DVD). The USB interface can transmit noncompressed video data streams only at high speed.

-

Interrupts—transfers of spontaneous messages that must be executed with no larger delay than the device allows. The time limits for servicing interrupts are set in the 10-255 msec range for low speed, 1-255 msec for full speed, while at high speed, even 125 μsec can be allowed. Delivery is guaranteed; in case of accidental exchange errors, data are retransmitted, although this increases the processing time. Interrupts are used, for example, to input data from a keyboard or to transmit information about mouse movements. Interrupts can also be used to deliver data to devices (a device signals that it requires data and the host delivers them in time). Message length can be 0-8 bytes for low speed, 0-64 bytes for full speed, and 0-1,024 bytes for high speed.

-

Bulk data transfers—carried out without any requirements in terms of delivery deadlines and speed. Bulk transfers can take up the entire bandwidth left over from other types of transfers. They have the lowest priority and can be suspended during high bus load. Delivery is guaranteed: In case of an error, data are retransmitted. Bulk transfers are suitable for exchanging data with printers, scanners, mass data storage devices, etc.

-

Control transfers—used to configure devices when they are first connected to the bus, and to control them afterward. The protocol provides guaranteed data delivery and acknowledgement by the device of successful execution of the control command. Control transfers can be used to send a command to a device (a request, possibly accompanied by data) and to receive a reply from it (an acknowledgement or rejection of the request and optional data). Only control transfers synchronize requests with responses in USB; other types of transfers do not explicitly synchronize input flow with the output flow.

The hardware portion of the USB consists of:

-

Peripheral USB devices, named USB functions, which carry out useful functions.

-

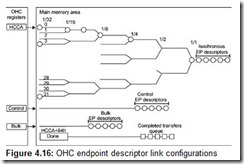

Host Controller, which links the bus with the computer’s center joined to the Root Hub, which provides connection points for USB devices. There are two types of USB 1.x Host Controllers: Universal Host Controller (UHC) and Open Host Controller (OHC) support full speed and low speed; Enhanced Host Controller (EHC) only supports the high speed of the USB 2.0.

-

USB hubs, which provide additional connection points.

-

USB cables, which connect devices to the hubs.

The software portion of the USB consists of:

-

Client software. USB device drivers that provide application software access to the devices. These drivers interact with the devices proper only via the software interface of the USB common driver (USBD). USB device drivers do not access any USB device hardware registers directly.

-

USB Driver (USBD), which is responsible for all USB devices, their enumeration, configuration, making services available, bus bandwidth and power supply distribution, etc.

-

Host Controller Driver (HCD), which converts input/output requests into data structures used by the Host Controller to execute physical transactions, accessing the host-controller’s registers and the communications area of the system memory.

The USBD and the HCD comprise the host part of the USB software. The USB specification delineates the range of their tasks, but does not describe the interface between them.

A physical USB device must be equipped with USB interface that provides complete support for the USB protocol, standard operation execution (configuration and reset), and information describing the device. Physical USB devices can be compound devices, which consist of several function devices connected to the internal hub and providing additional external connection points to its internal hub.

The Host Controller, which is a software/hardware subsystem of the host computer, manages the whole USB system. The Host Controller is either an intelligent PCI bus device or a part of the south bridge of the motherboard that actively interacts with the system memory.

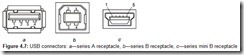

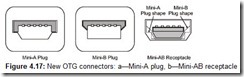

The physical USB interface is as simple as it is elegant. The USB cable and connector system make it impossible to connect devices incorrectly (Fig. 4.1, a and b). The device’s USB connector is labeled by a standard symbol (Fig. 4.1, c) to make it easily identifiable. Type A sockets are installed only on the downstream hub ports; type A plugs are installed on the peripheral device cables or upstream hub port cables. Type B sockets and plugs are used only on cable ends connected to peripheral devices or upstream hub ports (small devices usually have cables permanently wired into them). Compact devices use mini B connectors, while for the OTG (see Section 4.1.9) mini A plugs and mini AB sockets are used. Hubs and devices provide dynamic connecting and disconnecting, and inform the host of these events.

How the devices are to be powered must be taken into consideration when planning connections: As a rule, bus-powered devices are connected to the self-powered hubs. Only low power devices are connected to the bus-powered hubs: Thus, only devices like a USB mouse and other position indicators (a trackball, a touch pad) can be connected to a USB keyboard with an internal USB hub.

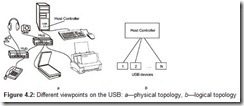

The physical topology of the USB is a multi-tiered star (Fig. 4.2, a). At its apex is the Host Controller connected to the root hub. The hub is a device that provides additional connection points and can also be used to power devices connected to it. A peripheral device or an intermediate hub can be directly connected to each hub’s port; the bus allows up to five levels (not counting the root) of hub chaining. Because compound devices already have an internal hub, they cannot be connected to the fifth level hub. Each intermediate hub has several downstream ports for connecting peripheral devices or lower level hubs, and one upstream port for connecting to the root hub or to a downstream port of a higher-level hub.

The logical USB topology is a simple star: Hubs (including the root hub) create an illusion of each logical device being connected directly to the Host Controller (Fig. 4.2, b). Device interactions in the star are solely subordinate, based on the polling/response system: the Host Controller sends to or receives data from the device it selects. A device cannot send data at its own initiative; direct transfers between devices are not possible. At its own initiative, a device can only send a signal of its wakeup, which is done by means of special physical signaling system (not by transmitting data).

A logical USB device is a set of independent endpoints (EP) with which the Host Controller (and the client software) exchanges information. Each logical USB device (function as well as hub) is assigned a unique address on the particular USB bus (1-127) by the host’s software configuration facility. Each endpoint of a logical device is identified by its number (0-15) and the direction of transmission (IN—transmission towards the host, OUT—transmission away from the host). Points IN4 and OUT4, for example, are two different endpoints, with which even different modules of the client software can communicate. The particular set of the endpoints depends on the device, but every USB device necessarily has a bidirectional endpoint 0 (EP0), through which general control over the device is exercised. Endpoints with numbers 1 through 15 (1 to 2 for low-speed devices) are used for application purposes. Device address and number and direction of the endpoint uniquely identify the information sink or source during information exchange between the Host Controller and USB devices. Each endpoint has a set of characteristics that describe the type of data transmission supported (isochronous, bulk, interrupts, control), packet size, and requirements to how often it requires to be serviced.

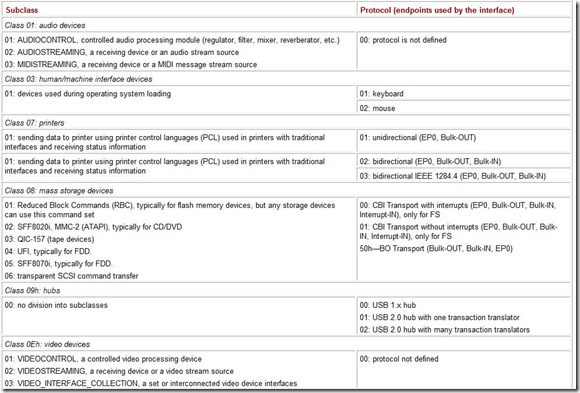

A device can perform several different functional tasks: For example, a CD-ROM drive can play audio disks and function as a mass data storage device. To perform each task, an interface is defined in a device: a set of endpoints designed to carry out the preset task and the rules for their use. In this way, each device must provide one or more interfaces. Having several interfaces allows several drivers to work with one device, each of the drivers accessing only its interface (which is a part of the USB device). Each interface can have one or more alternate settings, of which only one can be active at any one time. The alternate interfaces have different sets of endpoints (and possibly different characteristics).

A set of interfaces that can be supported simultaneously makes up the device configuration. A device can have one or more possible configurations, out of which the host selects one as active during the configuration process. The available functionality of the device and quite often the power it consumes depend on the configuration selected. Until a device has been assigned a configuration number, it cannot function as an application and its current consumption must not exceed 100 mA. The host selects the configuration on the basis of which of the total resources requested by the current configuration are available, including the current drawn off the bus.

4.1.2 Data Transfer Model

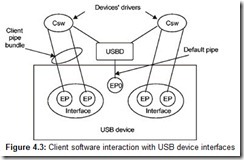

Each unit of the client software (usually, represented by the driver) communicates exclusively and independently with one interface of its device (function) (Fig. 4.3). In this figure, links represent communications pipes that are established between device drivers and their endpoints. Pipes are established only with the sets of the device endpoints of the selected alternative interfaces from the active configuration. The other endpoints are not available.

Requests, Packets, and Transactions

To transmit and receive data, client software sends an Input-Output Request (IRP) packet and awaits an acknowledgement that it has been processed. The IRP format is determined by how the USB driver is implemented in the particular operating system. The IRP only carries information about the request: Where the buffer of the transferred data is located in the main memory and the length of the transmission. The device driver is disengaged from the parameters of the specific current connection (speed, permissible packet size). The USB driver handles the request as USB transactions: If necessary, it can break long requests into packets that can be sent in one transaction. A USB transaction is a sequence of packet exchanges between the host and peripheral device, in the process of which one data packet can be sent or received (transactions, in which data are not transferred, are also possible). A request is considered to have been processed when all its associated transactions have been successfully completed. The client driver is not informed of the temporary difficulties that may be encountered during transaction execution: It must wait until all the exchanges have been completed (or until a time-out termination). However, the device can signal of fatal errors by a stall reply, which causes the request to be terminated abnormally; the client’s driver is informed of this event. In this case, all subsequent requests over this channel are cancelled. Operations over the given channel can only be resumed after explicit notification that the device driver has handled the error condition with the special request (also a USB driver call).

Long requests are split into transactions in such a way that maximum packet length can be used. The last packet with the final piece of the request can be shorter than the maximum packet length. When data are input, the Host Controller can interpret receiving a packet shorter than expected (the maximum packet size for the given endpoint) in one of two ways:

-

As the end of data block indicator. In this case, the IRP terminates normally and the following requests to the given channel are executed.

-

As an error indicator, upon which the given request is terminated, an error message is issued, and the channel is deactivated (all its awaiting requests are cleared).

An indicator by which the Host Controller determines how it is to process the given request must be sent in every IRP. When bulk transfers are performed, the most standard practice is to use short packets as end of block indicators. In this way, for example, in one version of the data storage device protocols, short packets of a known length are used for controlling purposes.

Pipes

There are two types of USB communications pipes:

-

Stream pipes deliver data from one end of the pipe to another; they are always one way. The same endpoint number can be used for two different stream pipes: input and output. Data transmissions in different stream pipes are not synchronized with each other. This means that client drivers’ requests for different pipes submitted in a certain order relative to each other may be executed in a different order. Requests for one pipe are executed strictly in the order of their arrival. If a major error is encountered (such that causes a Stall signal to be generated), the stream will be stopped. Bulk, isochronous, and interrupt data can be transferred in streams. Streams carry data of arbitrary format, which is determined by the developer of the device (but not by the USB specification).

-

Message pipes are bidirectional. Message transfers in opposite directions are synchronized with each other and are strictly ordered. The opposite side must acknowledge having received and processed each message. Normally, the next message cannot be sent until the previous message has been processed; however, during error handling, unprocessed messages may be cleared. Message formats are defined by a USB specification: There is a set of standard messages (requests and replies) and reserved message indicators; the format of the latter is determined by the device or interface manufacturer.

Pipe characteristics are associated with the characteristics of the endpoint (bandwidth, service type, buffer size, etc.). Pipes are organized when the USB devices are configured. The bus bandwidth is divided among all established channels. The allocated portion of the bandwidth is reserved for the pipe, and if establishing a new pipe requires a portion that does not correspond to the already existing allocation, the pipe allocation request is denied.

Pipes also differ in their purpose:

-

The Default Pipe, or Control Pipe 0, whose owner is the USB driver, is used to access configuration information of all devices. This pipe is established with Endpoint Zero, which always only supports control transfers in all devices.

-

Client Pipes belong to device drivers. Streams, as well as messages, can be sent over these pipes, which support any type of USB transfers (isochronous, interrupts, bulk, and control).

The device interface, with which the client driver works, is a pipe bundle. For these pipes, the device driver is the only source and sink of all transferred data.

The owner of all devices’ default pipes is the USB driver; it uses them to transfer configuration, control, and status information. The default message pipe may be used by a client driver to perform current device control tasks and to read its status, but it can do this only via the USB driver. For example, a USB printer driver sends messages over the default pipe to poll the printer’s current status (three indicators in the format of the LPT port status register are sent: I/O error, printer selected, end of paper).

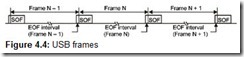

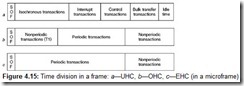

Frames and Microframes

The host organizes exchanges with devices according to its resource allocation plan. For this, every 1 μsec, the host controller generates frames, into which all the planned transactions are packed. Each frame begins with a Start-of-Frame (SOF) packet, which serves as a synchronizing signal for isochronous devices, as well as for hubs. Frames are sequentially numbered; the 11 lowest bits of the frame number are sent in the SOF marker. In the High Speed mode, each frame is divided into eight microframes, and SOF packets are sent at the start of each microframe (every 125 μsec). The SOF packet carries the same frame number in all eight microframes; the new value of the frame number is sent in microframe zero. Several transactions can be carried out in each frame (microframe); their maximum number depends on the speed, length of the data field of each of them, and the delays introduced by the cables, hubs, and devices. All frame transactions must be completed before the End-Of-(micro)Frame interval. The period (frequency), with which (micro)frames are generated, can be varied somewhat with the help of the special host controller register, which allows the frequency to be adjusted for isochronous transfers (see Section 4.1.5).

Framing is also used to provide bus robustness. At the end of each (micro)frame an End-Of-Frame (EOF) time interval is allocated, during which hubs are prohibited from transferring data toward the controller. If a hub detects that a data transfer is being conducted from a port toward the controller during this time, the port is disconnected, thus isolating the talkative device, and the USB driver is informed of this.

The Host Controller’s (micro)frame counter is used as the index source when accessing the frame descriptor table. Usually, the USB driver builds a descriptor table for 1,024 sequential frames (see details on planning for UHC, OHC, and EHC in Section 4.1.9) that it periodically accesses. Using these descriptors, the host plans frame loading in such a way that, in addition to the scheduled isochronous transactions and interrupts, there is always a room in them for control transactions. Any free frame time can be filled by bulk data transfers. The USB specification allows up to 90% of the bus bandwidth (i.e., (micro)frame time) to be taken by periodic transactions (isochronous and interrupt).

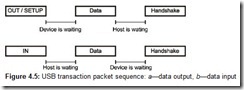

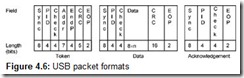

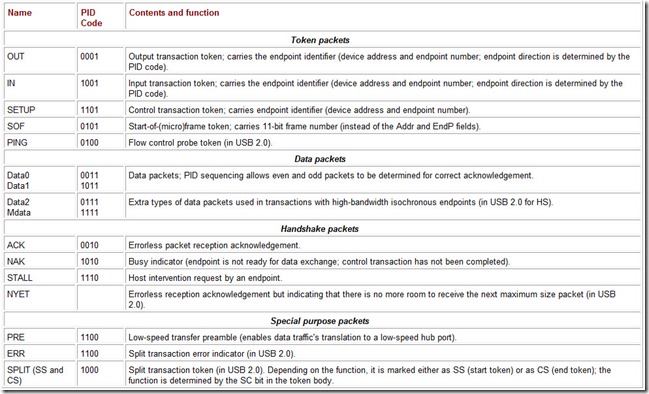

4.1.3 Bus Transactions

Traffic—a flow of packets with transmitted information—is conducted via USB using transactions. Each transaction only allows data exchange between the host and the addressed device (its endpoint). All transactions (exchanges) with USB devices consist of two or three packets; a typical transaction packet sequence is shown in Fig. 4.5. Each transaction is scheduled and is started at the initiative of the Host Controller by sending a token packet. A transaction token describes the transaction type and direction, the address of the selected USB device, and the endpoint number. The device addressed by the token recognizes its address and prepares for the exchange. The data source defined by the marker sends a data packet. Isochronous transfer transactions terminate at this stage: Packet reception is not acknowledged here. The acknowledgement mechanism is employed for other types of transactions, which guarantees data delivery. Fig. 4.6 shows packet formats; Table 4.2 lists the packet types. Data are sent with the least significant bit (depicted on the left in the timing diagrams) first in all packet fields, with the exception of the CRC field. The Sync and EOP field lengths are shown for fast-speed and low-speed transfers; for high-speed transfers, the Sync field is increased to 32 bit intervals and the EOP field is increased to 8 (in SOF packets, the EOP field is 40 bits long; see Section 4.1.6).

Table 4.2: Packet Types and Their PIDs

Transfer-Error-Handling Mechanisms

All received packets are checked for errors. This is made possible by the formats of the received packets and some conventions:

-

A packet starts with a synchronization sequence followed by its Packet Identifier (PID). The identifier is followed by its inverted copy—Check. The two copies not matching is an indication of an error.

-

The body of the packet (all packet fields, excluding the PID and EOP) are protected by a CRC code: 5 bit for token packets and 16 bit for data packets. The CRC’s value being different from the expected value is indication of an error.

-

A packet is completed with a special EOP signal; if there is incomplete byte in the packet, the packet is considered invalid. A false EOP, even on the byte boundary, will not allow the packet to be received because of the CRC control error, practically unavoidable in the given situation.

-

Packet data are relayed to the physical level by using bit stuffing (after six logical one bits, a logical zero bit is inserted), which prevents losing bit synchronization when a monotonous signal is sent. Reception of more than six logical one bits is considered an error (in the high-speed mode, this serves as the end of frame indicator).

Detecting any of the errors listed above makes the receiver consider that packet invalid. Neither the device nor the Host Controller responds to the packets that have been received with errors. In isochronous transfers, data in invalid packets are simply ignored (lost); means to reliable packet delivery are used in other types of transfers.

To detect that its partner does not acknowledge a packet, each device has a timeout counter, which breaks off waiting for the answer after a certain amount of time has elapsed. The USB has a set packet roundtrip time: the interval from when the transmitter completes sending a packet (marked by EOP) until it begins receiving response. The response time for end devices (and the Host Controller) is the interval from when a device senses EOP to the moment it begins sending a response packet. For hubs, a packet-delay time is specified, and for cables a signal-propagation delay time is also specified. The timeout counter must take into consideration the maximum delay allowable for the permissible bus configuration: up to 5 intermediate hubs, each cable up to 5 meters long. The permissible time-out value, expressed in bit intervals, depends on the speed:

-

For full speed and low speed, the delay inserted by one cable segment is small in comparison with one bit time (bt). Based on this, the following model for calculating the maximum allowable delays is employed in USB 1.0. For each cable segment, the maximum allowable delay is set at 30 nanoseconds (nsec); for each hub, it is 40 nsec. Consequently, five intermediate hubs together with their cables introduce a delay of 700 nsec for a double turnaround, which in the full-speed mode corresponds to approximately 8.5 bt. For a full-speed device, the response delay must not exceed 6.5 bt (7.5 bt, taking its cable into consideration). Based on this, the specification directs that a high-speed transmitter’s timeout counter be set to 16-18 bt.

-

For high speed, the cable segment delay is much larger than a bit time, and the calculations are somewhat different in USB 2.0. Here, each cable segment is allotted 26 nsec, while each hub gets 4 nsec plus 36 bit times. Consequently, double passage through six cable segments (2 × 6 × 26 = 312 nsec or 150 bit times) and five hubs (2 × 5 × 4 = 40 nsec or 19 bit times plus 2 × 5 × 36 = 360 bit times) takes up to 529 bit times. A device response delay of up to 192 bit times is allowed, and the overall delay due to cables and hubs is up to 721 bit times. Based on these calculations, the specification directs that at high speed the timeout counter be set to 736-816 bit times.

The Host Controller has an error counter for each endpoint of every device, which is zeroed out when each transaction with this endpoint is scheduled. This counter records all protocol errors (including timeout errors), and if the number of errors exceeds the threshold of three, then the channel with the given endpoint is stopped and its owner (the device driver of the USB driver) is informed of this. Until the threshold is reached, the host handles non-isochronous transfer errors by attempting to repeat the transactions without notifying the client software. Isochronous transfer errors are not retransmitted and the host informs the client about the errors right away.

Acknowledgements, Flow Control, and Device Error Reporting

Handshake packets are used to acknowledge reception, flow control, and report errors. The Host Controller can send only the ACK packet to a device, confirming by this that a data packet has been received without errors. A device sends the host the following handshake packets:

-

ACK: positive acknowledgment of a successful output or control transaction execution.

-

NAK: negative acknowledgement. It is sign that a device is not ready to execute the given transaction (no data to send to the host, no room in the buffer, or a control operation has not been completed). This is a normal response, of which only the Host Controller—which will have to repeat this transaction later—is informed. In input transactions, a device sends a NAK response instead of the data packet if the data are not ready.

-

STALL: a severe error message that means that the work with the given endpoint cannot continue without some sort of software intervention. This response is relayed both to the USB driver, which cancels further transactions with the given endpoint, and to the client drive, which is supposed to provide the said software intervention.

Output data flow control based only on the NAK answer in case the device is not ready makes very inefficient use of the bus bandwidth: In order to find out that a device is not ready, a large data packet is sent over the bus for nothing. In the Bulk-OUT and Control transactions in USB 2.0, this wastefulness is avoided by using the Ping Protocol. The host can query device readiness to receive a maximum size packet by sending it a Ping probe token. The device can answer this token with either ACK (if it is ready) or NAK (if it is not ready to receive a maximum size packet). A negative response will make the host repeat the attempt later; a positive response will allow it to execute a data output transaction. The device’s reaction to the output transaction following a positive reply to the probe token is more diverse:

-

ACK means a successful reception and readiness to receive the next full-size packet.

-

NYET means a successful reception but not being ready to receive the next packet.

-

NAK is an unexpected answer as it contradicts the positive reply to the probe, but it is possible if the device suddenly became not ready.

A high-speed device indicates the potential intensity of the NAK messages in the endpoint descriptors: For the endpoints of the Bulk and Control types, the bInterval field indicates the number of microframes per each NAK (0 means that the device will never give an NAK response to an output transaction).

Providing Reliable Delivery

Bulk, interrupt, and control transfers are performed with reliable data delivery. After a receiver successfully receives a packet, it confirms it by sending an ACK acknowledgement packet. If a receiver detects an error, it ignores the packet and sends no confirmation of its reception. The data source considers the next packet to have been successfully transmitted if it receives an ACK confirmation from the receiver. If no confirmation comes, then the source tries to retransmit the same packet in the next transaction. However, the confirmation packet can be lost because of some interference; in such case, data packets are numbered so that the receiver does not consider the repeated packet as a new portion of data. The numbering is done modulo 2 (1-bit number): Packets are divided into odd (with the DATA1 identifier) and even (with the DATA0 identifier). For each endpoint (except isochronous), the host and the devices have Toggle Bits whose initial states are synchronized. In IN and OUT transactions, data packets are sent and expected with DATA0 or DATA1 identifiers that correspond to the current state of these bits. The data receiver switches its bit when it successfully receives a data packet with the expected identifier; the data source switches its bit when it receives a confirmation of successful reception from the receiver. If the receiver gets an errorless packet with an unexpected identifier, it confirms it with an ACK but ignores its data because this packet is a repeated transmission of already received data.

Transaction Protocols for Different Types of Transfers

Transactions for different types of transfers have protocol differences due to several factors: whether or not the bandwidth, response time, reliable delivery, and input/output synchronization are guaranteed. Depending on these characteristics, one or other of the above-described protocol mechanisms are used in transactions. Error detection is employed in all types of transactions, so the corrupted data are ignored. Exactly what type of protocol mechanism is being used in the current transaction is known to both the Host Controller (by the previously received endpoint descriptor) and the USB device, to which this end point pertains.

Isochronous Transfer Transactions

Isochronous transactions provide guaranteed exchange speed but not reliable delivery. Because of this, their protocol does not include acknowledgements, as resending a packet will cause a breakdown in the data delivery schedule. Flow control based on acknowledgements is absent: A device must keep up with the exchange rate declared in the descriptor of the isochronous endpoint. Isochronous data transmitters and receiver synchronization are considered in more detail in Section 4.1.5.

Isochronous output transactions are made up of two packets sent by the Host Controller: an OUT token and a DATA packet. In the input transactions, the host sends an IN token, to which the device answers with a data packet (whose data field may be of zero length if the device has no ready data). Any other response is considered by the host as an error, and it stops the given channel.

In isochronous transfers, data are checked for validity (detecting and discarding packets with errors) and integrity (detecting missing packets). The integrity check is based on the exchange rate being strictly determinate: In compliance with its descriptor, the endpoint awaits a transactions with a period of 2bInterval−1 (micro)frames. Only one transaction in a (micro) frame is possible for a regular isochronous endpoint, and a packet reception error is expressed by the absence of data in the (micro)frame in which they are expected. Consequently, packet numbering (Toggle Bit) is not needed. Full-speed devices and Host Controllers must send packets only of the DATA0[1] type. Up to three data packets can be sent in each (micro)frame for high-bandwidth isochronous endpoints (USB 2.0). Any of these packets can get lost, and in order to detect such a situation packet enumeration inside a microframe is needed. For this purpose, two new data packet types—DATA2 and MDATA—have been introduced. In addition to enumeration, the diversity of packet types allows the communication partner to be informed of the plans for the given microframe. In IN transactions, the device indicates by the packet identifier how many more packets it intends to send in the same microframe, which allows the host not to attempt unnecessary input operations. Thus, if only one packet is sent in the microframe, it will be of the DATA0 type; if two packets are sent, their sequence will be DATA1, DATA0; if three packets are sent, they will follow in the order DATA2, DATA1, DATA0. In OUT transactions, for outputting a packet that is not the last one, the MDATA (More Data) packet type is used in the microframe, and the last packet identifier indicates how many packets preceded it. Thus, the DATA0 packet is used for one output transaction; the sequence MDATA, DATA1 is used for two; and the sequence MDATA, MDATA, DATA2 for three. Other types of transactions can wedge in between the high-bandwidth transactions in a microframe. Maximum size packets must be used in all microframe transactions apart from the last one.

Interrupt and Bulk Transfer Transactions

Interrupt and bulk transfer transactions look the same on the bus. Here, all the flow control, reliable delivery, and error-reporting mechanisms described above are employed. The toggle bits in the device and the endpoint of the packet sequence control are initialized as follows:

-

For the endpoints of the bulk transfers, any event associated with the transfer configuration (configuration or interface setting, error handling) sets the bits into the DATA0 state. Sending a new transfer request packet (IRP) does not initialize the bits.

-

Only DATA0 packets are used for the regular endpoints in interrupt transactions, because only one packet per transaction can be sent here and the query period is unknown.

-

For high-bandwidth endpoint interrupt transactions, the DATA0 packet goes first in a microframe; the following packets in the same microframe follow in the alternation sequence DATA1—DATA0.

Pursuant to the USB specifications, interrupt transactions can be used both to input data and to output them upon a request. However, interrupt outputs are not considered in such detail as the more conventional input transactions. Using the interrupt transaction for input/output operations is attractive because of the possibility of obtaining both almost guaranteed speed (without taking transmission errors into consideration), as well as guaranteed delivery.

Control Transfer Transactions

The function of the control transfers is to issue a command (Write Control) or a request (Read Control) to a device, and indicate the execution results. Transfers consist of two or three stages, and are executed with the help of several transactions:

-

The Setup Stage is intended for sending a control message from the host to a device. This message describes the command (request) that the device has to execute. The command may be used to transmit or receive data.

-

The Data Stage is intended for sending additional control information (Write Control) or receiving information from a device (Read Control). This stage may be skipped if no information needs to be input and the information being output fits into the Setup Stage message.

-

The Status Stage is intended for notifying the host of the fact and results (success or failure) of a command execution completion.

The setup stage is performed as one transaction beginning with a Setup token. Further, the host sends an 8-byte data packet (DATA0) with a standard structure request message (see Section 4.1.10). The device confirms successful receipt of this packet with an ACK response and begins to service the command request. If the host does not receive the acknowledgement, it has to repeat the request.

The host executes the data transfer stage (only for the three-stage transfers) using one or several IN (Read Control transfer) or OUT (Write Control) transactions, providing flow control and reliable delivery with the help of repeated transactions and number alternation. The first transaction of the data phase begins with a DATA1 packet.

The host signals the transition to the Status Stage by a transaction, in which the direction of the data transfer is opposite to the previous phase (Setup or Data). If there was no data phase, or a Write Control transfer was executed, the host executes an IN transaction. If the previously executed transfer was a Read Control, the host performs an OUT transaction (outputs a zero length DATA1 packet) or sends a PING probe token (in USB 2.0). At this stage only the response from the peripheral device is of any interest:

-

If the device has not completed executing the command, it answers with an NAK packet. The host must repeat the transaction until it receives a different answer.

-

If the device has successfully executed the command, it answers an IN transaction with a zero length DATA1 packet, and an OUT (or PING) transaction with an ACK confirmation.

-

If the device has completed command execution but did so with an error, then it will respond with a STALL packet.

Until the host receives a response indicating successful command execution, it has no right to access the given endpoint with another command. In this way, command execution serialization is provided: A device will not drown in a stream of commands that it cannot handle; the data being input will correspond to the state the device was in at the moment the request command—which might be preceded by control writes—was issued. This synchronization of USB device input and output streams is not directly supported by any other transfer type. Control transfers for all USB devices are supported by zero endpoints (EP0); client endpoint control transfers are supported in far from all cases.

4.1.4 Bus and Device Bandwidth

The serial transfer speed (1.5, 12, and 480 Mbps for LS, FS, and HS, respectively) is only a starting point for determining the real exchange throughput of a specific device on the bus and of all devices on the bus together. The bus bandwidth as a whole is also determined by the ratio of overheads to the transmitted useful data. Overhead expenditure sources, the ratio of overheads to overall traffic, and bus loading by different types of transactions with different data block sizes are considered in the following pages. To evaluate the possible data exchange speed with a specific device connected to the USB, a few aspects need to be mentioned:

-

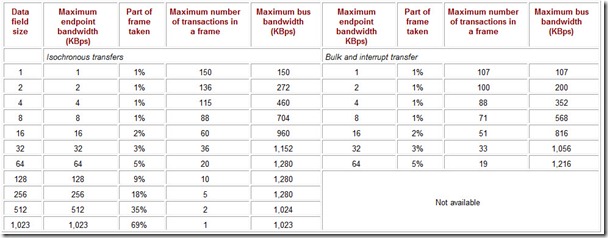

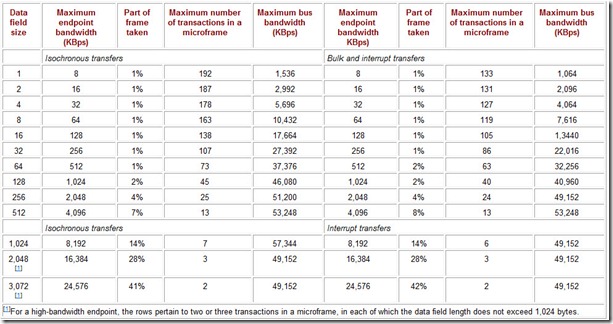

Only one transaction, defined by the bInterval descriptor of the endpoint, is conducted with a regular endpoint of periodic transfers (isochronous and interrupts) in each nth (micro)frame. Up to three transactions can be conducted in a microframe with a high-bandwidth endpoint. In Table 4.6, high-bandwidth endpoints are represented by a data field size of 1,024-3,072 bytes, and the bus load they produce pertains to all of their transactions in the microframe (from 1 to 3). The bandwidth Vmax of a periodic transfer endpoint is determined by dividing the size of a maximum length data packet Dmax by the length of the service period T: Vmax = Dmax/T. The service period T is determined the following way:

-

For isochronous endpoints, T= Tk × 2bInterval−1, where Tk is the period the SOF markers are sent with (1 msec for full speed and 125 μsec for high speed); bInterval lies in the 1-16 range. Consequently, the service period for FS can be from 1-32,768 msec; for HS, the service period is 0.125-4,096 msec.

-

For FS/LS interrupt endpoints, T= 1 × bInterval (msec); bInterval lies in the range 1-255; the service period can be between 1-255 msec.

-

For HS interrupt endpoints, T = 0.125 × 2bInterval−1, (msec); bInterval lies in the range 1-16; the service period can be between 0.125-4,096 msec.

-

-

When conducting bulk transfers, the number of transactions with one endpoint in one microframe is not defined, but its maximum does not exceed the value indicated in the tables. The USB driver can also use the simple policy of queue servicing, under which no more than one transaction is done for each endpoint in the microframe. Each microframe has room for one or two bulk transfer transactions, no matter how heavy the isochronous traffic may be; but when multiple devices request such transactions, the average transmission speed for each of them will obviously not be high.

Bus Overhead and Load

The following pertain to the overhead expenses of serial bus transfer:

-

Service information expenses (token and acknowledge packet, service fields of the data packets).

-

Bit stuffing expenses: Six consecutive logical ones in any field of the frame cause one additional bit to be transmitted over the bus. The share of these overhead expenses can be from 0% to 15% of the volume of the useful data. Because of this share being indeterminate, the given expenses are not taken into account in the tables given below.

-

Signal propagation delays in cables and hubs expenses.

-

Expenses of the internal device response to transaction delay.

-

Expenses for repeating transactions in case of reception errors or the device not being ready.

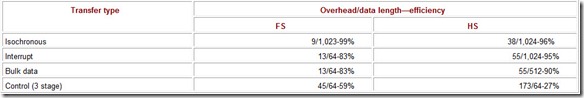

Overhead expenses for each transaction depend on the transaction type: The most efficient are isochronous transactions (no acknowledgements); the most resource-intensive are three-stage control transactions. The number of overhead expenditure bytes for each full- and high-speed transaction is given in Table 4.3 (low speed is not considered). High overhead at high speed is explained by the strong effect of the propagation delays: At full speed, the turnaround time (see Section 4.1.3) takes up to two bytes, while at high speed, up to 90 bytes are devoured (because the bit time of about 2 nsec is much smaller than the permissible propagation delay).

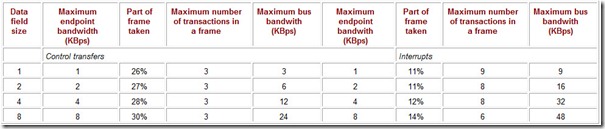

It is obvious that, with the view toward decreasing the portion of the bus overhead, it is practical to use maximum length packets. However, this type of transaction takes up too much time in the (micro)frame, leaving little time for other transactions. Theoretically, 12,000 bits (including the stuffed bits), or 1.5 KB, can be transferred over the bus in each frame (1 msec) at full speed (12 Mbps), although in reality this number is smaller due to the propagation and response delays. At high speed (480 Mbps), 60,000 bits, or 7.5 KB, are sent in each microframe (125 μsec). Tables 4.4, 4.5, and 4.6 list the throughput capacity parameters for different type of transactions depending on the data field length. Whether different types of transactions can be combined in one (micro)frame can be evaluated by adding up the portions of the frame they take (the result may not exceed 100%). The tables show that low-speed devices at low bandwidth use up a significant part of the bus time. This is tolerated in USB 1.x for the sake of simplicity, while in USB 2.0 the high bandwidth is saved by using split transactions (which require substantially more complex hubs).

Table 4.4: Low-Speed Transaction Bandwidth

Table 4.5: Full-Speed Transaction Bandwidth

Table 4.6: High-Speed Transaction Bandwidth

Bus Sharing by Different-Speed Devices

The USB specification allows devices with significantly different transfer speeds to be connected to one bus. For them to share the bus without conflicts in terms of (micro)frame time allocations, corresponding limitations on the maximum data field length have been adopted for each speed mode.

-

Low speed (LS, 1.5 Mbps): up to 8 bytes; moreover, a two-stage control transaction takes up 30% of a frame, while an interrupt transaction takes up 14%.

-

Full speed (FS, 12 Mbps): up to 1,023 bytes for isochronous exchanges (69% of a frame) and 64 bytes for the other exchange types (5% of a frame).

-

High speed (HS, 480 Mbps): up to 1,024 bytes for the interrupt and isochronous transfers (14% of a microframe); up to 512 bytres for bulk and control transfers (7-8% of a microframe).

Transceivers (as well as the connecting cables) of low-speed devices are not capable of working with full-speed signals, with which all SOF tokens and all exchange packets of full-speed devices are transferred. Because of this, a USB hub does not relay traffic to its downstream ports to which low-speed devices are connected unless the Host Controller transmits a special packet: a low-speed transfer preamble (PRE). All devices except the hubs ignore this packet. By issuing a preamble packet, the Host Controller guarantees that it will send the next packet at low speed. This packet will be a token that defines the type of transaction to be conducted with a LS device, while in output transactions this will be a data packet (which requires a separate preamble). A hub allows only one packet following the preamble to be sent to its downstream port with an LS device; when the hub detects the packet end (an EOP at low speed), it disables relaying again. In order for the hub to have sufficient time to switch the operating modes of its transceiver, a gap of four FS bit times is inserted between the preamble and the following packet. For a LS device to reply, no preambles are needed: Hubs can transparently relay the upstream traffic at both speeds (LS and FS). Naturally, the Host Controller must be able to receive both FS and LS packets. It is obvious that low-speed transactions make very inefficient use of the frame time, but this circumstance is tolerated in USB 1.x for the sake of being able to use inexpensive devices and unsophisticated hubs, which are simple repeaters. SOF tokens are not relayed to the low-speed ports, so LS devices cannot and do not support isochronous traffic, for which use of this token is necessary.

The effective coexistence of three speeds in USB 2.0 is more complex to implement and costs more. First of all, practically, a USB 2.0 Host Controller has two controllers: an EHC operating only at high speed and a USB 1.x companion controller (perhaps more than one) for the full and low speeds (UHC or OHC). The ports of the root hub have equal rights, but each port is connected to the corresponding controller during the autoconfiguration process, depending on the characteristics of the device (or hub) connected to it.

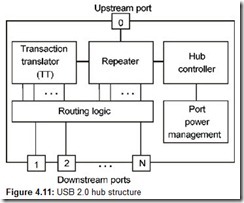

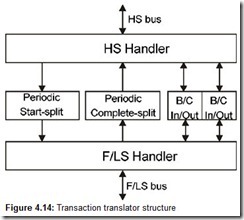

Second, USB 2.0 hubs are more complex: In addition to a repeater, they also have a transaction translator. When both the upstream and downstream ports of a hub are working at the same speed (FS or HS), the hub works in the repeater mode. In this case, a transaction with a device connected to the hub takes the entire channel from the Host Controller to the device for the entire duration of its execution. But when a USB 1.1 device or hub are connected to a port of a USB 2.0 hub working in the HS mode, then split transactions are used. In this type of transaction, the transfer is conducted at HS over the segment of the channel between the host and the hub (its transaction translator), while between the transaction translator and the USB 1.x device (or a hub), the exchange is conducted in the device’s FS or LS mode. These exchanges are separated in time; any high-speed transactions, including split ones, can intrude in between them. Consequently, split transactions allow the high bandwidth capacity not to be wasted: Transactions with a hub at high speed take 1/40th (for FS) and even 1/320th (for LS) of the bus time of transactions with the target device itself[1]. All the intricacies of the split transactions are hidden from old (USB 1.x) devices and hubs, which provides backward compatibility.

Hub ports can determine by hardware the speed that the connected device supports. All HS devices work in FS mode when first connected, and only after mutual negotiation with the hub’s port will they switch to the HS mode. If an HS device is connected to a USB 1.x hub, which does not support such negotiation, the device will remain in the FS mode, perhaps with reduced functionality. In the USB 2.0 system, a device can be asked (by requesting its descriptors, see Section 4.1.10) what will change in its functionality if it is connected at a different speed (by changing the connection topology).

It is quite understood that a USB 2.0 device can make use of the high-speed mode if there are only USB 2.0 hubs on the way to the Host Controller (also a USB 2.0). If this rule is violated and there happens to be an old hub between them, then the communications can only be established in the FS mode. If this speed suits the device and the client software (for example, for a printer or a scanner, this will only result in the user having to wait longer), then the connected device will work, but the user will be informed of the configuration being non-optimal. As far as possible, the configuration should be corrected, since USB cables can be connected and disconnected on the fly. Devices and software critical to the bus bandwidth will refuse to operate in incorrect configurations, and request to be reconfigured. In the case of an old Host Controller, none of the advantages of the USB 2.0 will be available to the user. In this event, the Host Controller will have to be replaced (either the motherboard should be replaced or a PCI card USB 2.0 controller should be installed).

A USB 2.0 Host Controller and hubs allow the total bus bandwidth to be also increased for old devices. If FS devices are connected to different ports of USB 2.0 hubs (including the root hub), their total USB bus bandwidth can be increased in comparison with 12 Mbps by as many times as there are HS hub ports used. Of course, the total bandwidth of all devices, including HS devices, cannot be higher than the total bandwidth of the HS bus (overhead expenses also need to be taken into account). Moreover, the architectural singularities of the Host Controller and hubs need to be taken into account. The Host Controller can multiply the FS/LS bus bandwidth by the number of its built-in USB 1.x controllers. The effect of the hub’s bus bandwidth multiplication depends on how its transaction translator is implemented (see Section 4.1.8).

4.1.5 Synchronization During Isochronous Transfers

In isochronous data transfers, devices that are interconnected into one system need to be synchronized. Let’s consider an example of USB use. A USB microphone (data source) and USB speakers (data sink) are connected to a computer and interconnected via the software mixer (client software). Each of these components may have its own understanding of time and synchronization: Let’s say the microphone has a sampling frequency of 8 KHz and data width of 1 byte (producing a 64 Kbps stream), the speakers have a sampling frequency of 44.1 KHz and data width of 2 × 2 bytes (176.4 Kbps), while the mixer works at a sampling frequency of 32 KHz. In this system, the mixer is the connecting unit, and its clock is considered to be the master clock. The software mixer services data in packets, the service sessions are carried out at certain regular time intervals (let’s say every 20 msec, or at a frequency of 50 Hz). The mixer must have sample rate converters, which convert n input samples into m output samples using the interpolation method (i.e., making up intermediate samples). These converters allow the mixer to receive data from the microphone at its frequency (8,000 samples per second, in our case) and send them to the speakers at another frequency (44,100 samples per second). The natural solution to the task of providing interaction among these components would be to establish synchronous interconnection among them, taking care of the data stream transfer as well as of the synchronization signal. USB, which provides concurrent connection of multiple devices, does not provide synchronous interface to devices. Synchronous links in USB are based on isochronous transfers. In this case, the following frequencies are involved:

-

Fs (sample rate): data source and sink clocks.

-

Fb (bus clock): the USB clock frequency—FS frame frequency (1 KHz) and HS microframe frequency (8 KHz). All USB devices can see SOF tokens at this frequency.

-

Service frequency: frequency with which client software accesses the USB drivers to send and receive isochronous data.

In a system without a common synchronization source, the following deviations are possible between pairs of sync signals:

-

Drift: deviation of formally identical frequencies from the nominal values (there are no absolutely identical clock generators).

-

Jitter: frequency fluctuation relative to the nominal.

-

Phase shift if the signals are not tied together by the Phase Locked Loop (PLL) system.

In a digital data transfer system, these deviations result in potential data excess or shortage at the source or sink, fluctuating or progressing in time. Speed negotiation is performed using the feed-forward or feedback mechanisms. Which of these two mechanisms is used depends on the type of synchronization supported by the isochronous endpoint of a given device.

In terms of the type of data source or data sinks synchronization with the system, there are asynchronous, synchronous, and adaptive types of endpoints in USB, each of which has its corresponding USB channel type. The synchronization type is set by bits [3:2] of the attribute byte (see Section 4.1.10) in the isochronous endpoint’s descriptor.

-

00—no synchronization.

-

01—asynchronous endpoint of a device that has no capabilities to synchronize its sampling rate with SOF tokens or with other USB system frequencies. Data transfer frequency is either fixed or programmed. The number of data bytes received during each (micro)frame is not constant. An example of an asynchronous source device is a CD player clocked by a quartz generator or a satellite TV receiver. An example of a sink device would be cheap speakers clocked by an internal clock generator.

-

An asynchronous data source declares its transmission speed implicitly by the number of samples it sends in one (micro)frame: The client software will process as much data as have actually come in.

-

An asynchronous data sink must provide explicit feedback to the adaptive driver of the client’s software in order to synchronize the stream delivery rate.

-

-

11—synchronous endpoint of a device with an internal clock generator synchronized with the SOF (micro)frame markers (1 or 8 KHz). During one (micro)frame, sources and sinks generate (use up) the same number of data bytes set at the channel programming stage. An example of a synchronous data source would be a digital microphone with its sample rate synthesized by SOF tokens. While maintaining a constant frequency, the frequency synthesizer must take into account the possibility of one or two tokens going missing (because of possible transmission errors). These endpoints use implicit feedback to adjust to the bus frequency. In software terms, organizing channels with this type of device is the simplest.

-

10—adaptive endpoint of a device capable of adjusting its internal frequency to the necessary data stream (within reasonable limits). An example of an adaptive data source would be a CD player with a built-in sample rate converter; an example of a data sink is high-fidelity USB speakers or headphones.

-

An adaptive source allows the speed to be changed under control of the sink that provides explicit feedback.

-

An adaptive sink determines the instantaneous frequency value by the amount of data received over a certain averaging interval. In this way, implicit feedforward frequency declaration is performed.

-

The feedback, which allows the device frequency to be synchronized with the bus frequency, can be explicit or implicit. The feedback mechanism will be considered using an asynchronous sink as an example; it works similarly for an adaptive source. An asynchronous sink must explicitly inform the Host Controller of the frequency, at which the data are to be sent relative to the (micro)frame frequency: Fs/Fb. It is assumed that one sample is represented by one data byte; for a different sample size, a corresponding recalculation needs to be done (for the device and its client software) so that the Fs/Fb ratio is the number of bytes transferred during one (micro)frame. The Fs/Fb ratio may turn out not to be an integer number; in this case, its entier determines the constant volume of transfer (data field size) with the given endpoint in each (micro)frame, while the fractional part is the accumulating remainder that will cause periodic transfer increase in some (micro)frames. In the given case, the sink must calculate the Fs/Fb ratio with an averaging interval of no less than 1 sec. This ratio can change over time (even if only because of the rounding error), so the host must periodically request the Fs/Fb ratio from the device, which is what is called explicit feedback data.

The Fs frequency is set precisely to 1 Hz. Taking into account the maximum transfer size in a frame (1,023 bytes) and the frame frequency (1 KHz), 10 bits is enough at full speed for both the integer and the fractional parts of the Fs/Fb ratio. At high speed, up to 3,072 bytes can be transferred in a microframe, so 12 bits are needed for the integer part. A microframe frequency of 8 KHz requires a 13-bit fractional part. Based on this, the feedback data are represented as follows:

-

By a three-byte number in FS; bits [23:14] are the integer part, bits [13:4] are the fractional part, the rest of the bits are reserved (zeroes).

-

By a four-byte number in HS; bits [28:17] are the integer part, bits [14:4] are the fractional part, the rest of the bits are reserved (zeroes).

The feedback information stream is always one way, opposing the data flow it controls (hence being called feedback). The explicit feedback data of the device are taken off the endpoint with the same number as the endpoint used for the main data transfer operation. This endpoint also is isochronous: Bits [5:4] = 01 in its attribute byte indicate that this endpoint is used for feedback (in an endpoint used for transferring data, these bits will be zeroed out). The value of the polling interval (bInterval), with which the Host Controller must request the feedback data, is also set in the descriptor. This will allow the Host Controller constantly to adjust the number of bytes sent during each (micro)frame without data buffer overflow or underflow. If there have been no changes since the last poll, the endpoint can reply to the poll with a zero length data packet.

An adaptive source must analogously receive the feedback information from the host so that it can generate exactly the amount of data per each frame as is needed for the Host Controller. Here, the data stream and the feedback stream go in opposite directions, so the endpoint with the same number as the data source is also used for the explicit feedback.

In some cases, allocating a special feedback endpoint in a device for endpoints requiring feedback can be avoided by using implicit feedback. This can be done if the device has a group of functionally linked isochronous endpoints working off a common clock and if there is an endpoint among them with a direction opposite to the endpoint that requires feedback. If feedback is needed for an asynchronous sink, then the implicit feedback information is taken from the data transfer speed of the source synchronized with it. For an adaptive source, the implicit feedback information is analogously taken from the speed of the sink synchronized with it. Bits [5:4] of the attribute byte of the data endpoint, which can be used as a source of the implicit feedback, have value 10. Links by synchronization are created in the group based on the endpoint numbers. To find a source of implicit feedback for a point, an isochronous point of the opposite direction with the same or lower number and whose attribute byte bits [5:4] = 10 must be used.

USB allows both the device and the host to place time markers in the continuous isochronous transfer stream for any endpoint. To do this, the host sends a special control request, Synch Frame, to the device in which it indicates the number of the frame expected to come in the near future and the number of the endpoint to which the given time marker pertains. The device and the host have the same time reference point, based on the frame number sent in the SOF token. Synchronization by the zero microframe of the given frame is presupposed for HS devices. The time marker can be used, for example, to indicate the starting moment for an isochronous transfer (for an Open Host Controller, the number of the starting frame is shown in the isochronous transfer descriptor; for a Universal Host Controller, the driver itself places the isochronous transaction descriptors in the frame list). Consequently, the device can get ready for the start of an isochronous exchange in advance.

A USB Host Controller can adjust frame frequency. For example, the Universal Host Controller has an SOF_Modify register, using which software can change the division factor used to divide 12 MHz frequency to obtain 1 KHz frame frequency within ±0,5%. Naturally, the Host Controller can adjust its clock to the internal clock of only one device.

4.1.6 Physical Interface

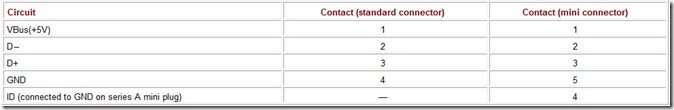

The USB physical interface is defined by the mechanical and physical specifications of the bus. The information signals and 5 V voltage supply are sent over four-wire cable. To make hot swapping possible, the connectors are constructed in such a way that the supply circuits connect earlier and disconnect later than the signal circuits; moreover, a protocol for signaling device connection and disconnection is provided. In addition to the standard connectors shown in Fig. 4.1, miniature connectors are also used. The functions of the USB connector contacts are listed in Table 4.7; Fig. 4.7 shows contact numbering. All USB cables are straight: they connect like contacts (except the ID circuit; see Section 4.1.9).

Table 4.7: USB Connector Contact Functions

A USB cable comprises a shielded twisted pair with 90 ohm impedance for the signal circuit and one non-shielded pair of wires for the voltage supply (+5 V); the maximum segment length (cable length from a device to the hub) is up to 5 meters. For low-speed mode, non-shielded non-twisted pair up to 3 meters long can be used for the signal circuit (it is cheaper). Limitations on the segment length are dictated by the signal decay and the introduced delays. The signal propagation delay in one cable segment must not exceed 26 nsec, so at large linear delay, the maximum cable length can get shorter. The maximum device distance from the Host Controller is determined by the delay introduced by the cables, intermediate hubs, and the devices themselves (see Section 4.1.3).

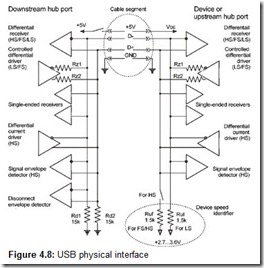

Two wires—D+ and D-—are used to transmit signals. There are the following devices on each side of the interface (hub port side and the connected device side; Fig. 4.8):

-

Differential receiver, whose output is used when receiving data.

-

Controlled (switchable) differential FS/LS driver: A voltage source that in addition to a differential signal can also generate a single-ended 0 (SE0) signal, as well as disconnect itself from the line to provide half-duplex exchange.

-

Single-ended receivers, indicating the current state of each signal wire.

-

Resistors that pull signal levels for detecting device connection:

-

Rd1, Rd2 (15 K) on the hub side

-

Ruf (for an FS/HS device) or Rul (for an LS device)

-

-

Additional components for high-speed operations (for HS devices only):

-

A switch that disconnects the Ruf resistor when the high-speed mode is selected

-

Series resistors Rz1 and Rz2 on the outputs of the differential driver that provide line matching and load

-

Controllable differential current driver

-

Signal envelope detector

-

Disconnect envelope detector (only on the downstream hub ports)

-

The static output signal levels of FS/LS drivers must be no lower than 0.3 V (low level) or higher than 2.8 V (high level). Receivers must withstand input voltages between −0.5 V and +3.8 V. The sensitivity of differential receivers must be 200 mV with common mode range 0.8 V—2.5 V. Linear receivers must have hysteresis: they must be able to sense as the low level signal anything up to a threshold of 0.8 V, and as the high level signal anything down to a threshold of 2 V.

HS Mode Signal Specifics

The high-speed mode (480 Mbps, or half as fast as Gigabit Ethernet) requires that the transceivers be meticulously matched with the communications line. Only cables with a shielded twisted pair for the signal lines can work at this speed. USB equipment must have additional special transceivers for high-speed operation. Stringent demands regarding maximum trace length, signal trace lengths being equal, proximity of other signal lines, copper pour, and other factors, are placed on the conductor layout from the USB interface microchip to the connector (or to the place where the cable is soldered in).

Unlike the potential drivers for the FS and LS modes, the HS transmitters are current drivers, requiring terminating resistors on both signal lines. Resistors Rzl and Rz2 serve as terminators (shown in Fig. 4.8): When working in the HS mode, the differential driver FS/LS generates an SE0 signal (i.e., both of its outputs are grounded and these resistors become loads for the D+ and D− lines). Their resistance (taking into account the driver’s output impedance) is 2 × 45 ohm, which provides the required matching with the line’s impedance. The device and the hub turn on their HS terminators (and disconnect Ruf) after both have successfully confirmed the HS mode in the process of resetting the device.

The differential current drivers generate current impulses with a nominal value of 17.78 milliamperes that flow through a load of 22.5 ohms (two load resistors at both ends of each signal line are connected in parallel). When the J signal is being transmitted, current is passed to the D+ line; when the K signal is transmitted, the current flows through the D− line. In this way, a differential transmission signal of about ±400 mV is obtained[1].

The signal arrives weakened to the input of the differential receiver; in order to eliminate the noise influence on the signal, a signal envelope detector with a 100-150 mV threshold is introduced into the device schematics. The signal from the differential receiver is squelched until the signal envelope detector is triggered. The delay from the moment the envelope detector is triggered to when the differential receiver turns on may be up four bit times, but it will only result in a shorter Sync pattern received at the beginning of the packet.

Stringent requirements are made to the static (levels) and dynamic (duration and the raise and fall times) signal characteristics in the HS mode, and there are special templates called Eye Patterns that the signals must match. Wideband (no lower than 1 GHz) differential oscilloscopes and signal generators can be used for testing; specialized testers for USB 2.0 equipment are also produced. For testing HS devices (hubs included), the USB 2.0 specification defines special control requests that switch the selected port into the test mode.

Data Transfer

Transfers over two USB wires are not limited to differential signals. Receivers and transmitters use many line states and commands to organize the hardware interface. Moreover, not only electrical signal levels, but also their duration in one or another state, are taken into consideration. In terms of signal levels at the receiver input, the following signals are distinguished:

-

Diff0: (D+)−(D−) > 200 mV at (D+) > 2 V

-

Diff1: (D−)−(D+) > 200 mV at (D−) > 2 V

-

SE0 (single-ended zero): (D+) < 0.8 V and (D−) < 0.8 V.

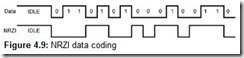

For transmitting data, the Diff0 and Diff1 signals are used; they encode the J (Data J State) and K (Data K State) states. At full and high speeds, the J state corresponds to the Diff1 signal, and the K state corresponds to the Diff0 signal. At low speed, the situation is reversed: J corresponds to Diff0, and K corresponds to Diff1. The information is transmitted serially using the NRZI encoding (Fig. 4.9): When a zero bit is sent, the signal state (J or K) at the beginning of the bit time is changed to the opposite; when a one bit is sent, the signal state does not change. The duration of the bit time is determined by the nominal transfer speed: 0.666 μsec for the low-speed mode (LS, 1.5 Mbps); 83.3… nsec for the full-speed mode (FS, 12 MBps); and 2.0833… nsec for the high-speed mode (HS, 480, Mbps).

The Bus Idle state in the FS/LS corresponds to the long J state; in the HS mode, it corresponds to the SE0 state.

The start of the packet indicator is a transition from the idle state into the K state, which is the first bit of the Sync pattern: a sequence of zeroes that in the NRZI is coded by switching the states (J and K) in the beginning of each bit time. The Sync pattern allows the receiver to adjust to the necessary synchronization frequency and phase. The Sync pattern is concluded with a value one bit (no state change); the bits that follow it pertain to the identifier and the packet body. In the HS mode, the beginning part of the Sync pattern can be lost by the hub (because of the signal envelope detector delay). Taking this into account, the Sync pattern for the HS is increased to 32 bits (including the last value one bit). Going through five hubs, each of which can lose up to 4 sync bits, the arriving Sync pattern may be reduced to 12 bits.

To prevent losing synchronization when sending a long sequence of ones, the bitstuffing technique is used: After each six consecutive ones, the transmitter inserts a zero into the data stream; the receiver deletes these ones. Receiving more than six value one bits in a row is considered a bit-stuffing error.

The end of packet (EOP) is marked by an SE0 signal that lasts 2 bit times and is followed by a switch into the bus idle state. In the HS mode, a violation of the bitstuffing rule is used for the EOP marker: sending the sequence 01111111 without bitstuffing serves as the EOP. Receiving the seventh value one bit will produce a bitstuffing error that in the HS mode is the end of packet indicator. A correct packet is distinguished from a bad one by an integer number of received bytes and the correct CRC value. The starting zero (causing the state switch) in the EOP makes it easier to determine the boundaries of the packet body precisely. In SOF packets, the EOP field is lengthened to 40 bits for detecting device disconnection.

Special Signaling: Dynamic Attach and Detach Detection, Device Reset, Suspend, and Resume

A hub detects device attach by the voltage levels of the D+ and D− lines in the following ways:

-

When there is no device connected, the signal levels in the D+ and D− lines are low (in the SE0 state), which is caused by the hub’s Rd1 and Rd2 resistors.

-

When an LS device is connected, the signal level of the D− line goes up pulled by the device’s Rul resistor (switch into the LS-Idle state).

-

When an FS/HS device is connected, the signal level in the D+ line goes up pulled by the device’s Rul (switch into the LS-Idle state).

The connection detection and reset sequence for an FS/LS device is depicted in Fig. 4.10. The hub monitors the signals from the downstream port and signals when they change. After it detects a state change, the system software waits about 100 msec (signal settle time) and then checks the port’s status. Having detected the fact of connection and the device type (LS or FS/HS), the software issues a bus reset command to this port.

To execute the Bus Reset command, the hub drops the level of the signal that was set high by the device (D+ or D−) for 10-20 msec (i.e., sends an SE0 signal for 10-20 msec). It is assumed that after this the device should be ready for configuration (i.e., respond only to the accesses to EP0 at the zero device’s address).

Bus reset for HS devices starts up the speed negotiation protocol. Upon connection, as well as at the reset signal, an HS device places its circuitry into the FS state (disconnects the terminators and connects the Ruf resistor). Thus, at first, an HS device looks to the hub like an FS device. The so-called chirp sequence is used to negotiate the speed: In response to the SE0 issued by the hub to perform the reset (grounding the D+ line), an HS device places its transmitters into a chirp K state (i.e., sends a current pulse into the D− line). An HS hub will respond to this pulse with a pulse into the D+ line, which results in a chirp J state. This pulse exchange is performed twice more; after the negotiation has been successfully completed, both the device and the hub switch into the HS operation mode (and the Ruf resistor disconnects). All this chirping lasts 10-20 msec, after which the bus switches into the HS-Idle state (a prolonged SE0 signal). Now the host needs to query the hub’s status again to ascertain the mode of the connected device. If an HS device is connected to an FS port, the hub will not respond the device’s chirps.