logic gate

Only basic logic gates are included in this entry—that is, components that perform a Boolean logic operation on two to eight inputs (or one input, in the case of an inverter) to create a single high or low logical output.

What It Does

A logic gate is a circuit that delivers an output, either high or low, depending on the states of its two inputs, either or both of which can be high or low.

Some gates may have more than two inputs, and an inverter only has one input, but the basic gates all conform with the two-input, one-output model. The components that constitute a logic gate are almost always etched into a wafer inside a silicon chip.

In a digital computer, a high logic state is tradibinations of two logical states that could be interpreted as “true” and “false.” This concept had few practical applications until the 1930s, when Claude Shannon saw that because a basic switch has two states, Boolean algebra could enable analysis of complex networks of switches that were being used in telephone systems.

A small network of logic gates can perform bi- nary addition, and all other operations in a digital computer are built upon this foundation.

Origins

The concept of digital logic originated in 1894, when English mathematician George Boole an- nounced his invention of a form of algebra (now referred to as Boolean algebra) to analyze combinations of two logical states that could be interpreted as “true” and “false.” This concept had few practical applications until the 1930s, when Claude Shannon saw that because a basic switch has two states, Boolean algebra could enable analysis of complex networks of switches that were being used in telephone systems.

Because the state of a switch could also be used to represent the values 0 or 1 in binary arithmetic, and because a transistor could function as a switch, Boolean algebra was implemented in solid-state digital computing equipment.

How It Works

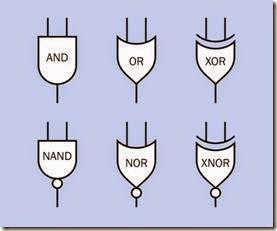

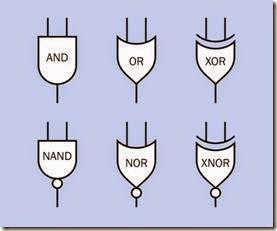

While conventional arithmetic uses arithmetical operators to represent procedures such as addition or multiplication, Boolean algebra uses Boolean operators. The operators of special interest in digital electronics are named AND, NAND, OR, NOR, XOR, and XNOR.

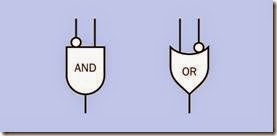

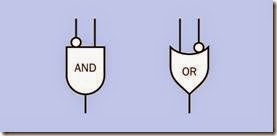

Although each gate actually contains multiple transistors, it is represented by a single logic sym- bol, as shown in Figure 10-1. The names of the Boolean operators are customarily printed all in caps. A gate requires a power supply and a connection with negative ground, separate from its inputs, but these connections are omitted from

gate schematics because they are assumed to exist.

Figure 10-1. Six types of two-input logic gates are used in digital electronics, although the XNOR gate is rare, as it has few applications. The names are customarily printed in uppercase letters.

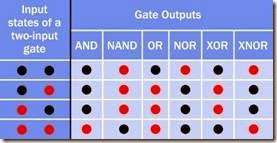

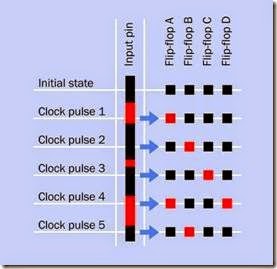

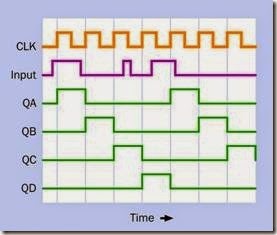

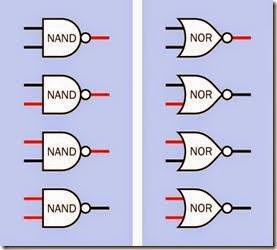

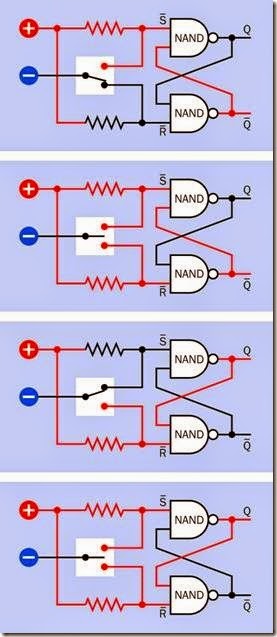

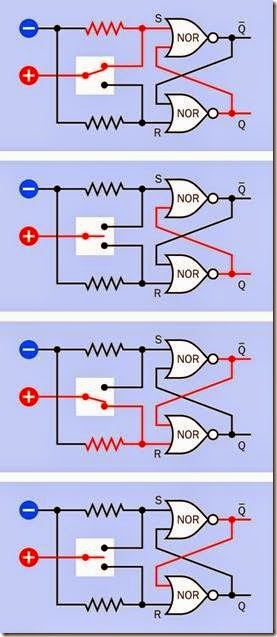

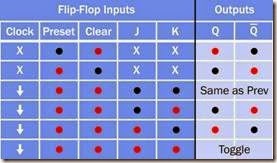

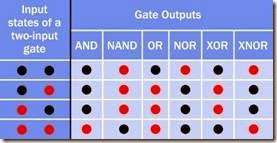

The functions of the gates with two inputs can be defined in electrical terms. In Figure 10-2, the four possible combinations of inputs are tabula- ted in the left column, with red indicating a high input and black indicating a low input. The corresponding output from each gate is shown beneath its name. This kind of tabulation is known as a truth table, as it is derived from Boolean algebra which originally concerned itself with “true” and “false” states.

Figure 10-2. The four possible combinations of input states in a 2-input logic gate are shown at left. The corresponding output from each gate is shown beneath its name. Red indicates a high state, while black indicates a low state.

The truth table assumes that positive logic is being used. Negative logic is very uncommon, but if it were used, the red dots in the truth table would correspond with low inputs and outputs, while the black dots would correspond with high inputs and outputs.

Inversion

The small circles appended to the outputs of NAND, NOR, and XNOR gates mean that the out- put of each gate is inverted compared with the AND, OR, and XOR gates. This can be seen by in- spection of the output states shown in Figure 10-2. The circles are known as bubbles.

Sometimes logic symbols are shown with a bub- ble applied to one input, as in Figure 10-3. In these cases, the circle indicates that an input must be inverted. More than one gate may be needed to achieve this logic function in an actual circuit. The style is often used to show the inner workings of an IC, using a minimum number of logic symbols.

Figure 10-3. The circle in a logic gate symbol indicates that a signal is being inverted. Circles can be inserted at gate inputs, but in a real circuit a separate inverter is likely to be needed to create this effect.

Single-Input Gates

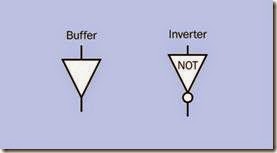

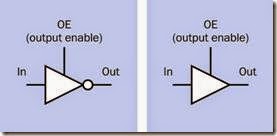

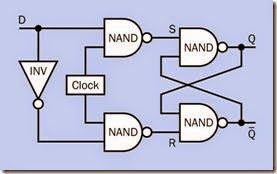

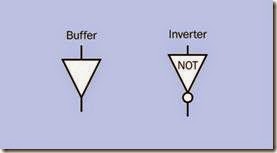

Two gates exist that have a single input and a single output, shown in Figure 10-4. The buffer should not be confused with the symbol for an op-amp or a comparator. (Those components always have two inputs.) The output state of a buffer is the same as its input state, but the component may be useful to deliver more current or to isolate one section of a circuit from another.

When a bubble is appended to a buffer, it be- comes a NOT gate, more commonly known as an inverter. Its function is to create an output state that is opposite to its input state.

Figure 10-4. The two logic gates that have only one input and one output. Note that in some schematics showing internal logic of ICs, the bubble on an inverter may be found on the input side instead of the output side.

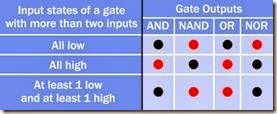

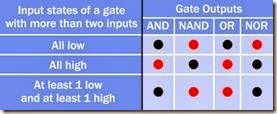

Gates with More than Two Inputs AND, NAND, OR, and NOR gates can have any number of inputs, as suggested in Figure 10-5, although practical factors usually limit the inputs

to a maximum of eight.

Figure 10-5. The previous table has been modified to show the outputs from logic gates that have more than two inputs. XOR and XNOR gates are not included in the table, because a strict interpretation of their logic requires that a unique output state exists if one input is high while the other is low.

The rules can be summarized like this:

• Output from an AND gate: Low if any of its inputs is low, high if all of its inputs are high.

• Output from a NAND gate: High if any of its inputs is low, low if all of its inputs are high.

• Output from an OR gate: High if any of its inputs is high, low if all of its inputs are low.

• Output from a NOR gate: Low if any of its in- puts is high, high if all of its inputs are low.

In the case of XOR and XNOR gates, their logic requires that a unique output state must exist if one input is high while the other input is low.

In fact, so-called three-input XOR gates do exist, an example being the 74LVC1G386 chip, in which the output is high if all three inputs are high, or if one input is high, but not if two inputs are high or no inputs are high. Further discussion of more- than-two-input XORs is outside the scope of this encyclopedia.

Boolean Notation

For reference, the original written notation for Boolean operators is shown in Figure 10-6. Un- fortunately, the notation for these operators was never properly standardized, and in more than one instance, multiple symbols acquired the same meaning. The letters P and Q are often, but not always, used to represent two input states that can be true or false.

• The use of a horizontal line above a symbol, to indicate that its state has been reversed, has carried over to datasheets where this notation can show that an output state from any digital chip is inverted. The line is known as a bar.

Arithmetical Operations

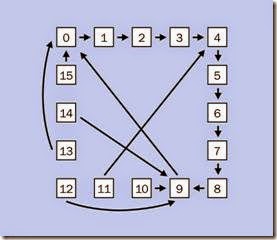

Suppose we wish to sum two binary numbers, each containing two digits. There are four digits altogether, and depending on their values, there are 16 different possible addition sums, as shown in Figure 10-7.

If A0 and B0 represent the rightmost digits of the two numbers being added, and S0 is the sum of those two digits, inspection of the figure shows that the sum can be derived using just three rules:

1. If A0 = 0 and B0 = 0, then S = 0.

2. If A0 and B0 have opposite states, then S0 = 1.

3. If A0 = 1 and B0 = 1, then S0 = 0, and carry 1 to the next place left.

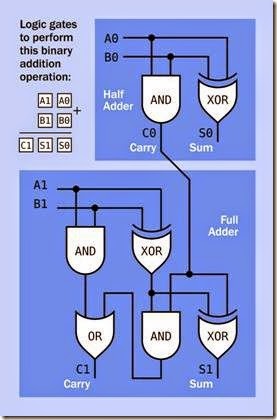

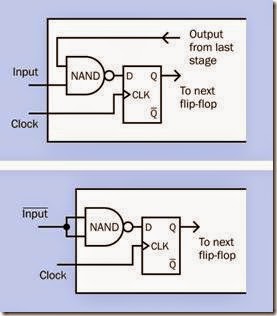

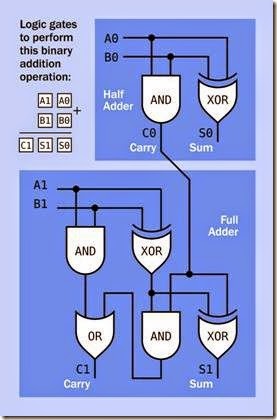

If A0 and B0 are the two inputs to an XOR logic gate, the output of the gate satisfies all three rules, except the need to carry 1 to the next place left. This last function can be satisfied with an AND gate. The function of two gates is known as a half adder, and is shown in the top section of Figure 10-8.

Figure 10-6. Boolean operators as they have been ex- pressed in written notation. Lack of standardization has resulted in more than one symbol representing some of the operators.

When we consider the next pair of binary digits to the left, the situation now becomes more complicated, because we may be carrying 1 into this addition sum from the previous stage, and we still need to be able to to carry 1 out (if necessary) to the next stage. An assembly of five logic gates can deal with this, and their combination is known as a full adder. This is shown in the bottom section of Figure 10-8.

Figure 10-7. Sixteen different addition sums are possible, when summing two binary numbers of two digits each.

The combination of XOR and AND gates shown in Figure 10-8 is not the only one that works to add binary numbers. However, it may be the most intuitively obvious.

Other Operations

Binary arithmetic remains the most important application of logic gates, but individually pack- aged gates are seldom used for that purpose anymore. They were long since subsumed into large multifunction computing chips.

Single gates still have application in small systems, or to modify the inputs and outputs of microcontrollers, or to convert the output from one complex digital chip to make it compatible with the input of another. This last application is often referred to as glue logic.

Applications for single gates are discussed in “How to Use It” on page 103.

Figure 10-8. Logic gates can be used to add binary numbers, using a high input or output to represent a binary 1 and a low input or output to represent a binary 0. This schematic shows one possible way for gates to add two two-digit binary numbers.

Variants

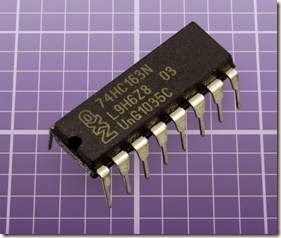

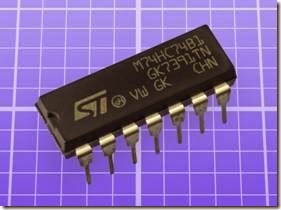

Chips containing logic gates were introduced in the 1960s. The 7400 NAND chip, from Texas In- struments, was the first of a series that became so influential, the same basic part numbers (with letters added before, after, and among the digits) are still used today. An example of a currently available through-hole 7400 chip is shown in Figure 10-9.

Figure 10-9. A modern version of a 7400 chip containing four NAND gates.

Initially, these chips conformed with a transistor- transistor logic (TTL) standard that had been invented at TRW in 1961 and introduced in commercial products by Sylvania in 1963. It established the now-familiar standard of 5VDC for the power supply. Many logic chips now use other voltages, but the term “high” still means an input or output that is near to the supply voltage, while “low” means an input or output that is near to negative ground. The exact definition of “near” will be found in datasheets for the chips.

The 7400 series was successful partly because it was engineered for compatibility. The output from one gate could be connected directly to the input of another gate, with a few bypass capacitors added on a circuit board to suppress voltage spikes caused by rapid switching. Earlier components had not been so easy to interface with each other. The new standard dominated the industry to the point where dozens of manufacturers started making chips that conformed with it, and a single board could mix-and-match chips from multiple vendors.

Because many logic chips acquired part numbers that began with 74, they are often referred to as the 74xx series, where other digits (sometimes more than two) can be substituted for xx. This avoids ambiguity, as the very first chip in this for- mat was a NAND gate that had 7400 as its actual part number. In the text below, 7400 will refer to that specific chip, whereas 74xx will refer to the whole series of chips.

RCA introduced a competing family of logic gates in 1968, using CMOS transistors. As each part number began with a 4 and contained four digits, this was referred to as the 4000 series. The CMOS chips were slower and more expensive, but tolerated a wider range of power supply voltages (3V to 12V, initially). Their biggest advantage was that they used much less current. This was important, as TTL chips created a lot of waste heat. The lower power consumption of CMOS al- so enabled one chip to control the inputs of many others, which simplified circuit design. This one- to-many relationship is known as fanout.

Ultimately, CMOS chips transcended their early limitations. While they were reserved initially for battery-powered devices in which very low power consumption was more important than speed, CMOS is now used almost everywhere, still maintaining its advantage of low current (almost zero, in fact, while a chip is quiescent) while equalling the speed of TTL. However, CMOS logic chips are very often pin-compatible with the old TTL components, and modern CMOS part numbers are often derived from the old 74xx series.

Most CMOS logic chips in the old 4000 series are still available, and may be used in situations where a power supply greater than 5VDC is convenient.

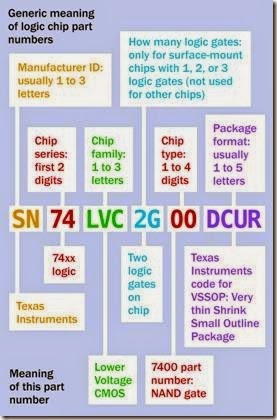

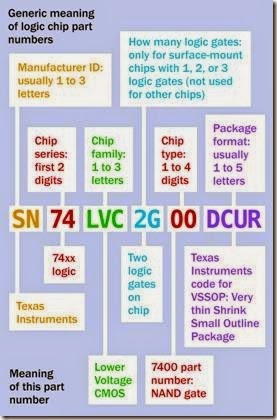

Part Numbers

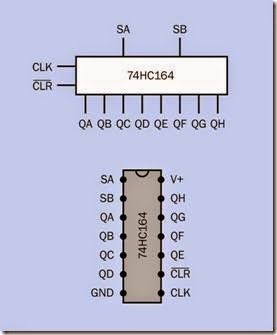

As the performance of semiconductors gradually improved, successive families of logic chips were introduced, identified by one-letter, two-letter, or three-letter acronyms. The acronym was inserted into the part number, so that a 7400 NAND gate in the HC (high-speed CMOS) family be- came a 74HC00 NAND gate.

Because these chips were available from multiple sources, the part number was also preceded with one or more letters indicating the manufacturer. And because each chip was manufactured in different versions (for example, some complied

with military specifications, while others didn’t), letters were also appended to the end of the part number. Today, the appended letters may indicate whether the chip is of the old through-hole format, or conforms with a more recent surface- mount format.

Summing up:

• Prefix: manufacturer ID.

• Numerals, omitting any letters in the middle: Chip functionality.

• Middle letters: Chip family.

• Suffix letters: Package format.

Thus, for example, the actual part number for a 74HC00 NAND chip could be SN74HC00N, where the SN prefix indicates that it is manufactured by Texas Instruments and the N suffix means that it is in plastic dual-inline-pin (DIP) format. (The SN prefix was introduced by Texas Instruments in the earliest days of integrated circuits as an acronym for “semiconductor network,” meaning that multiple transistors were “networked” on a wafer of silicon. Other manufacturers used their own schemes for part numbering, and so SN be- came exclusively identified with Texas Instru- ments.)

The system of augmenting part numbers has been further extended by inserting 1G, 2G, or 3G immediately after the family identifier, to indicate surface-mount chips that contain one, two, or three logic gates. If the “G” identifier is missing, the chip usually has four logic gates, which was the standard used in the original 74xx series. This rule applies even in surface-mount formats, where the surface-mount pads of four-gate chips have the same functions as the pinouts of the original TTL versions (except in the case of square-format surface-mount chips, which are not discussed here).

When searching a catalog to find a chip by its part number, it helps to remember that searching for a 7400 chip may not find any hits, but searching for a 74HC00 (or any other valid number containing a family identifier) is much more likely to be understood.

A key to understanding part numbers is shown in Figure 10-10. The upper part of the figure is a guide to interpreting numbers on a generic basis, while the lower part interprets the specific part number shown.

Families

As of 2013, the HC family in the 74xx series has become so widely used, it can be considered the default in the traditional DIP 14-pin format. In- cremental improvements are still being made, and new families are being introduced, primarily in surface-mount formats which use lower power-supply voltages (down to around 1VDC).

Figure 10-10. How to interpret the segments of a logic chip part number in the 74xx family (in this case, a 7400 NAND gate).

Here is an historical summary of the most important chip families.

• 74xx: Original series of bipolar TTL chips.

• 74Hxx: Bipolar TTL, high speed, about twice as fast as the original 74xx chips, but twice the power consumption.

• 74Lxx: Bipolar TTL, lower power consumption than the original TTL, but also much lower speed.

• 74LSxx: Bipolar TTL, lower power with Schottky input stages, faster than original TTL. Some LS chips are still being manufactured.

• 74ASxx: Bipolar TTL, Advanced Schottky, in- tended to supercede the 74Lxx.

• 74ALSxx: Bipolar TTL, Advanced Low Power Schottky, intended to supercede the 74LSxx.

• 74Fxx: Bipolar TTL, Faster.

• 74HCxx: CMOS high-speed emulation of 74LSxx.

• 74HCTxx: CMOS but with similar high-state input voltage threshold to bipolar TTL chips, for compatibility.

• 74ACxx: Advanced CMOS.

• 74ACTxx: Advanced CMOS emulation of TTL with similar high-state input voltage thresh- old to TTL, for compatibility.

• 74AHCxx: Advanced Higher-Speed CMOS, three times as fast as HC.

• 74VHCxx: Very High Speed CMOS.

• 74AUCxx, 74FCxx, 74LCXxx, 74LVCxx,

74ALVCxx, 74LVQxx, 74LVXxx: Various specifications, many using power supply voltag- es of 3.3V or below.

In the 4000 series, an early significant improvement was the 4000B family, which allowed a higher power supply limit (18V instead of 12V) and was much less susceptible to damage by static discharge. The 4000B family almost totally replaced the old 4000 family, and most 4000B

chips are still available, as they are useful in situations where a power supply delivers more than 5VDC.

• When it is referenced casually, the B at the end of a chip number in the 4000 series may be omitted. When the number is listed in a catalog, the B is included.

Chips with 45 as their first two digits were introduced as a new generation, but were not widely adopted. After that, the 4000 series ceased to evolve, and CMOS chips adopted 74xx part numbers, distinguishing themselves by the insertion of letter groups in the center of the number.

To add to the confusion, some 4000 series part numbers were appended to 74xx part numbers, so that, for example, the 74HCT4060 is designed to be compatible with the old 4060B chip.

Family Interoperability

One of the most important issues relating to chip families is their differing specifications for a low- state voltage and a high-state voltage in inputs and outputs.

The original 74xx TTL series, using a 5VDC power supply, used these approximate specifications:

• Output: 74xx voltage representing a low state (at most 0.4V to 0.5V)

• Input: 74xx input voltage interpreted as a low state (maximum 0.8V)

• Output: 74xx voltage representing a high state (at least 2.4V to 2.7V)

• Input: 74xx input voltage interpreted as a high state (minimum 2V)

This provided a safe margin of error of at least 0.4V when chips were communicating with each other.

In the CMOS 4000 family, however, logic chips required a minimum input of 3V to 3.5V to be interpreted as a high state. The minimum acceptable output from a TTL chip was below this level, creating problems if anyone should try to use the output from a TTL chip to communicate with an input on a CMOS chip.

One solution is to add a 4.7K pullup resistor to the TTL output, guaranteeing that it won’t fall too low. But this wastes power, and the need for the resistor is easily forgotten. Another option is to use the HCT or ACT family of CMOS logic. The “T” in these family names indicates that they have been engineered to share the input standards of the old TTL chips. They still deliver the same high output as other types of CMOS, making them seem to be the best possible solution. Unfortunately, it does entail a compromise: the “T” chips are more sensitive to noise, among other factors.

• Ideally, chip families should not be intermingled.

Gates per Chip

Each of the original 74xx chips contained multiple gates within the limits of a uniform 14-pin through-hole format. The gates that were most commonly used had two inputs, and there were four of these gates per chip.

However, the desire for miniaturization, and the use of automatic chip-placement and soldering equipment, made one-gate and two-gate logic chips desirable and practical in surface-mount format. (Three-gate surface-mount chips exist, but are sufficiently unusual that they are not de- scribed in this encyclopedia.)

Two Inputs, Single Gate

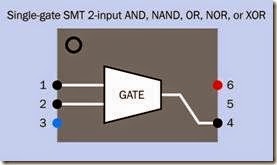

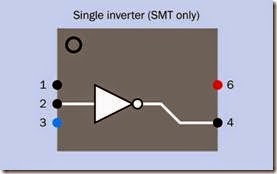

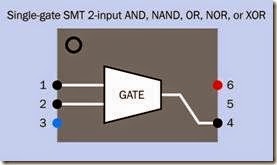

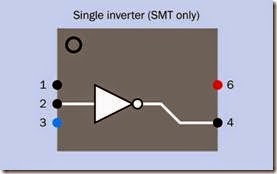

Where a chip contains just one logic gate, it is almost always a surface-mount component, and the part number has 1G in the middle to indicate “one gate.” Pad functions are shown in Figure 10-11. The layout is standardized for all logic gates, with the exception of XNOR gates, which are not manufactured in surface-mount format.

Figure 10-11. Internal configuration and solder-pad functions for a two-input surface-mount single-gate logic chip that can contain an AND, NAND, OR, NOR, or XOR gate. XNOR gates are not manufactured in this format.

In the figure, a gate is shown in generic form, indicating that it may be an AND, NAND, OR, NOR, or XOR gate, depending on the part number of the chip. Inputs are on the left of the gate, while its output is on the right. The chip does not have a solder pad in position 5, but the pad at top right is identified as pin 6 for consistency with the numbering pattern in other surface-mount components where six pads are common.

The generic part numbers for single-gate surface-mount two-input logic chips are shown here, with letter x indicating that letter sequences are likely to be inserted to indicate manufac- turer, logic family, and chip format:

• AND gate: x74x1G08x

• OR gate: x74x1G32x

• NAND gate: x74x1G00x

• NOR gate: x74x1G02x

• XOR gate: x74x1G86x

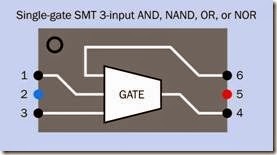

Three Inputs, Single Gate

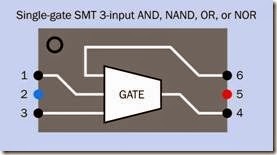

AND, NAND, OR, and NOR single gates are avail- able with more than two inputs. Their output is determined by rules shown in Figure 10-5. XOR and XNOR gates are not included in the table, because a strict interpretation of their logic re- quires that a unique output state exists if one in- put is high while the other is low.

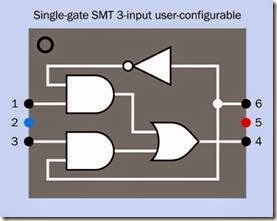

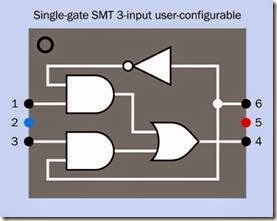

The pad functions for a surface-mount single- gate logic chip with three inputs are shown in Figure 10-12. The generic part numbers for these chips are shown below. Again, each x indicates that letter sequences are likely to be inserted to indicate manufacturer, logic family, and chip format.

Figure 10-12. Internal configuration and solder-pad func- tions for a three-input surface-mount single-gate logic chip that can contain an AND, NAND, OR, or NOR gate.

The generic part numbers for single-gate surface-mount three-input logic chips are shown here, with each x indicating that letter se- quences are likely to be inserted to indicate man- ufacturer, logic family, and chip format:

• AND: x74x1G11x

• NAND: x74x1G10x

• OR: x74x1G32x

• NOR: x74x1G27x

Single Gate, Selectable Function

A few surface-mount chips can emulate a variety of two-input gates, by using appropriate external connections. The internal logic of one example, with generic part number x74x1G97x (an actual example would be Texas Instruments SN74LVC1G97), is shown in Figure 10-13. De- pending which pin is grounded and which other pins are used as inputs, the chip can emulate all five of the most commonly used gates. To achieve this, however, some inputs have to be inverted.

Figure 10-13. Internal configuration for a configurable surface-mount chip that can emulate various two-input logic gates, depending which inputs are used and which are grounded. Some inputs have to be inverted to emulate some gates.

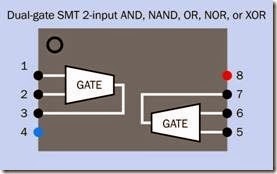

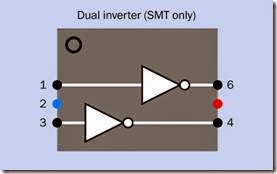

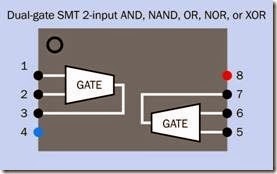

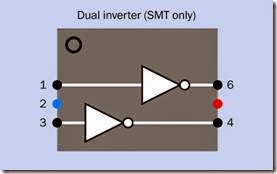

Two Inputs, Dual Gate

Two-input surface-mount AND, NAND, OR, NOR, and XOR gates are available in dual layout (two gates per chip). The internal logic and pad functions are shown in Figure 10-14. The generic part numbers for these chips are shown here. Again, each x indicates that letter sequences are likely to be inserted to indicate manufacturer, logic family, and chip format.

Figure 10-14. Internal configuration and solder-pad functions for a two-input surface-mount dual-gate logic chip that can contain two AND, NAND, OR, NOR, or XOR gates. XNOR chips are not manufactured in this format.

The generic part numbers for dual-gate surface- mount two-input logic chips are shown below, with each x indicating that letter sequences are likely to be inserted to indicate manufacturer, logic family, and chip format:

• AND: x74x2G08x

• NAND: x74x2G00x

• OR: x74x2G32x

• NOR: x74x2G02x

• XOR: x74x2G86x

Original 74xx 14-Pin Format

Each of the original 74xx TTL chips contained multiple gates within the limits of a uniform 14- pin chip format. The available options were, and still are:

• Quad 2-input: Four gates with two inputs each

• Triple 3-input: Three gates with three inputs each

• Dual 4-input: Two gates with four inputs each

• Dual 5-input: Two gates with five inputs each

• Single 8-input: One gate with eight inputs

The five-input chips have become so uncommon that they are not described in this encyclopedia.

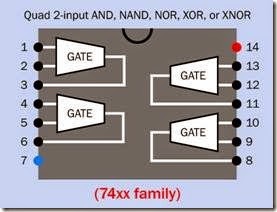

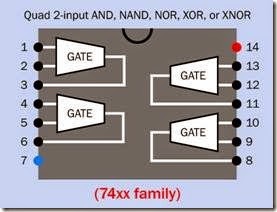

Quad Two-Input 74xx Pinouts

14- pin DIP 74xx quad two-input logic chips are available in AND, NAND, NOR, XOR, or XNOR ver- sions, all of which have an internal layout shown in Figure 10-15. The layout is unchanged in surface-mount format. The gates are shown in generic form, as the layout remains the same re- gardless of which type of gate is in the chip. All the gates in any one chip are of the same type. The four connections leading to a gate are its in- puts, while the single connection from a gate is its output.

Figure 10-15. In a 14-pin quad two-input 74xx logic chip, the AND, NAND, NOR, XOR, and XNOR versions all share this generic layout.

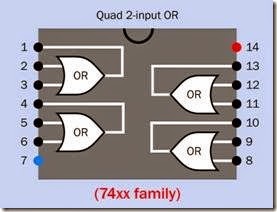

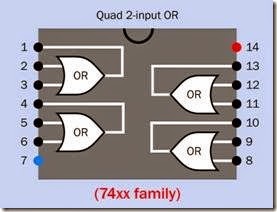

• The 14-pin quad two-input OR chip has different pinouts from all the other 74xx logic chips. It is shown in Figure 10-16.

Figure 10-16. In a quad two-input 74xx OR chip, this lay- out is used, which is different from that used in all the other quad two-input logic gates.

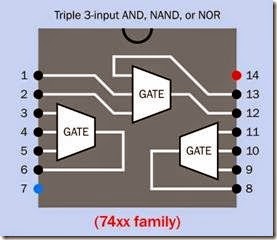

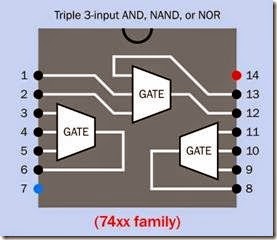

Triple Three-Input 74xx Pinouts

The AND, NAND, and NOR versions of a 14-pin DIP 74xx triple three-input logic chip all have an internal layout shown in Figure 10-17. The layout is unchanged in surface-mount format. The gates are shown in generic form, as the layout remains the same regardless of which type of gate is in the chip. All the gates in any one chip are of the same type. Three connections leading to a gate are its inputs, while a single connection from a gate is its output.

Figure 10-17. In a 14-pin triple three-input 74xx logic chip, the AND, NAND, and NOR versions all share this generic layout.

– The 14-pin triple three-input OR chip has different pinouts from all the other 74xx logic chips. It is shown in Figure 10-18.

Figure 10-18. In a triple three-input 74xx OR chip, this lay- out is used, which is different from that used for all the other triple three-input logic gates.

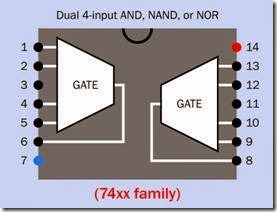

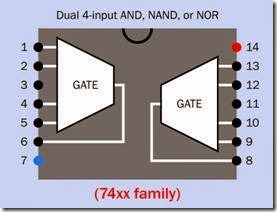

Dual Four-Input 74xx Pinouts

A 14-pin DIP 74xx dual four-input logic chip con- tains two four-input gates. The AND, NAND, and NOR versions all have an internal layout shown in Figure 10-19. The layout is unchanged in surface-mount format. The gates are shown in generic form, as the layout remains the same regardless of which type of gate is in the chip. All the gates in any one chip are of the same type.

• There is no OR chip of the 14-pin dual four- input type.

Figure 10-19. In a 14-pin dual four-input 74xx logic chip, the AND, NAND, and NOR versions all share this generic layout. There is no 74xx OR chip with four inputs per gate.

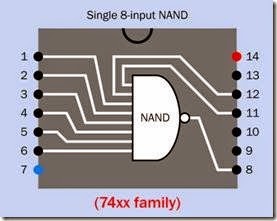

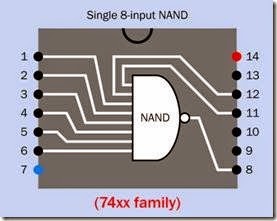

Single Eight-Input 74xx Pinouts

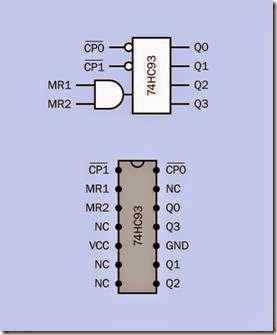

A 14-pin DIP 74xx single eight-input NAND chip contains one eight-input gate, as shown in Figure 10-20. The layout is unchanged in surface- mount format.

• There is no AND chip of the 14-pin single eight-input type.

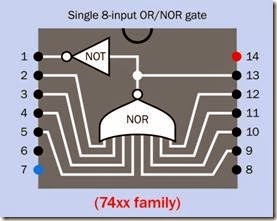

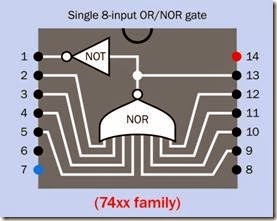

A 14-pin eight-input logic chip in the 74xx series, able to function as both an OR and a NOR, is shown in Figure 10-21. The output from the NOR gate is connected with pin 13, but also passes through an inverter to create an OR output at pin

1. (Because a NOR gate is equivalent to an

inverted-OR, when its output is inverted again, it returns to being an OR.)

Figure 10-20. The internal layout of single eight-input NAND chip in the 14-pin 74xx series. There is no 74xx AND chip with eight inputs per gate.

Figure 10-21. The internal layout of single eight-input OR/NOR chip in the 14-pin 74xx series. Pin 13 has the NOR output, while pin 1 has the OR output.

The following list shows the generic part numbers for DIP and surface-mount versions of 14- pin logic chips in the 74xx series that have two or more inputs per gate. As before, an x indicates that letter sequences are likely to be inserted to indicate manufacturer, logic family, and chip format.

• Quad 2-input AND: x74x08x

• Quad 2-input NAND: x74x00x

• Quad 2-input OR: x74x32x

• Quad 2-input NOR: x74x02x

• Quad 2-input XOR: x74x86x

• Quad 2-input XNOR: x74x266x

• Triple 3-input AND: x74x11x

• Triple 3-input NAND: x74x10x

• Triple 3-input OR: x74x4075x

• Triple 3-input NOR: x74x27x

• Dual 4-input AND: x74x21x

• Dual 4-input NAND: x74x20x

• Dual 4-input NOR: x74x4002x

• Single 8-input NAND: x74x30x

• Single 8-input OR/NOR: x74x4078x

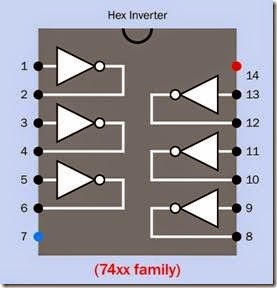

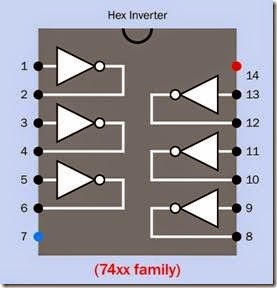

74xx Inverters

Single, dual, and triple inverter packages in the 74xx series are available in surface-mount format only. Their internal arrangement is shown in Fig- ures 10-22, 10-23, and 10-24.

Figure 10-22. The internal layout of a 74xx series logic chip containing one inverter. This is available in surface- mount format only. Pin 5 is absent. Pin 1 is not connected.

Figure 10-23. The internal layout of a 74xx series logic chip containing two inverters. This is available in surface- mount format only.

Figure 10-24. The internal layout of a 74xx series logic chip containing three inverters. This is available in surface-mount format only.

In the 14-pin format, a hex inverter chip (con- taining six inverters) is available, as shown in Figure 10-25. The layout is the same for DIP and surface-mount formats.

Generic part numbers for inverter chips are as follows:

• Single inverter: x74x1G04x

• Dual inverter: x74x2G04x

• Triple inverter: x74x3G14x

• Hex inverter: x74x04x

Figure 10-25. The internal layout of a 14-pin 74xx hex in- verter logic chip, containing six inverters. This layout is the same for DIP and surface-mount versions.

Additional Variations

Some chips in the 74xx series (both DIP and sur- face mount versions) have variants with open drain or open collector outputs, while others have inputs that are configured as Schmitt triggers. These variants will be found as hits when searching supplier websites for logic chips by gate name and number of inputs.

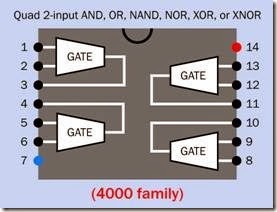

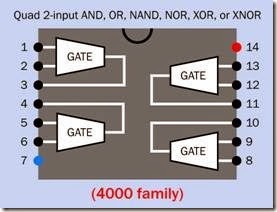

Pinouts in the Original 4000 Series

Each of the original 4000 CMOS chips contained multiple gates within the limits of a uniform 14- pin chip format. The available options were, and still are:

• Quad 2-input: Four gates of two inputs each

• Triple 3-input: Three gates of three inputs each

• Dual 4-input: Two gates of four inputs each

• Single 8-input: One gate of eight inputs

In the 4000 family, 14-pin quad two-input logic chips are available in AND, OR, NAND, NOR, XOR, or XNOR versions, all of which have an internal layout shown in Figure 10-26. The gates are shown in generic form, as the layout remains the same regardless of which type of gate is in the chip. All the gates in any one chip are of the same type. The four connections leading to a gate are its inputs, while the single connection from a gate is its output.

Unlike the 74xx family, the quad two-input OR chip in the 4000 family has the same pinouts as the other types of quad two-input logic chips.

Figure 10-26. In the 4000 family, the AND, OR, NAND, NOR, XOR, and XNOR versions of a quad two-input logic chip all share this generic layout.

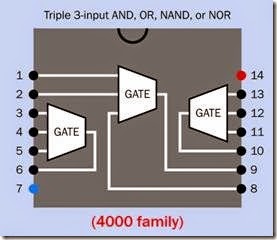

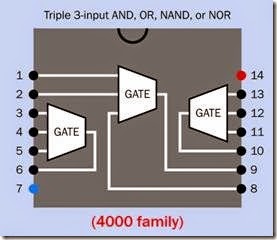

In the 4000 family, a 14-pin triple three-input logic chip contains three three-input gates. The AND, OR, NAND, and NOR versions all have an internal layout shown in Figure 10-27. The gates are shown in generic form, as the layout remains the same regardless of which type of gate is in the chip. All the gates in any one chip are of the same type. The three connections leading to a gate are its inputs, while a single connection from a gate is its output.

Unlike the 74xx family, the triple three-input OR chip in the 4000 family has the same pinouts as the other types of triple three-input logic chips.

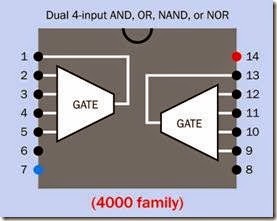

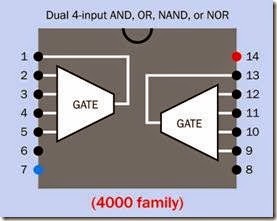

In the 4000 family, a 14-pin dual four-input logic chip contains two four-input gates. The AND, NAND, OR, and NOR versions all have an internal

layout shown in Figure 10-28. The gates are shown in generic form, as the layout remains the same regardless of which type of gate is in the chip. All the gates in any one chip are of the same type. Each pair of connections leading to a gate are its inputs, while the single connection from a gate is its output.

Figure 10-27. In the 4000 family, the AND, OR, NAND, and NOR versions of a triple three-input logic chip all share this generic layout.

Note that the 4000 family does have a dual four- input OR chip, whereas the 74xx family does not.

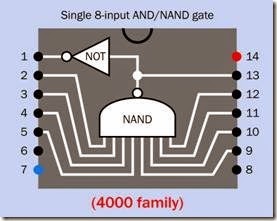

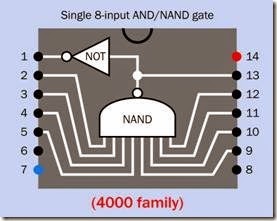

In the 4000 family, a 14-pin eight-input logic chip with AND and NAND outputs is available, as shown in Figure 10-29.

The following list shows the generic part num- bers for 14-pin logic chips in the 4000 family that have two or more inputs per gate (in actual part numbers, letters will be substituted where an x appears):

• Quad 2-input AND: x4081x

• Quad 2-input NAND: x4011x

• Quad 2-input OR: x4071x

• Quad 2-input NOR: x4001x

• Quad 2-input XOR: x4070x

• Quad 2-input XNOR: x4077x

• Triple 3-input AND: x4073x

• Triple 3-input NAND: x4023x

• Triple 3-input OR: x4075x

• Triple 3-input NOR: x4025x

• Dual 4-input AND: x4082x

• Dual 4-input NAND: x4012x

• Dual 4-input OR: x4072x

• Dual 4-input NOR: x4002x

• Single 8-input AND/NAND: x4068x

Figure 10-28. In the 4000 family, the AND, OR, NAND, and NOR versions of a dual four-input logic chip all share this generic layout.

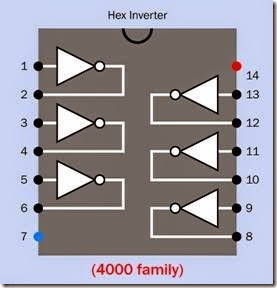

4000 Series Inverters

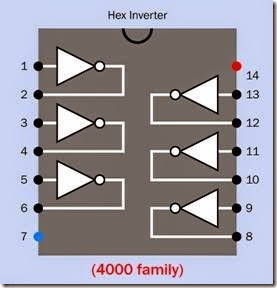

In the 4000 family, the 4069B is a 14-pin hex inverter chip (containing six inverters), as shown in Figure 10-30. This has the same pinouts as the x74x04x chip.

How to Use It

Which Family

In DIP format, the HC family has existed for more than 30 years, and has become established as a widely used default choice.

In surface-mount formats, the choice of family will largely be determined by the choice of sup- ply voltage.

Figure 10-29. In the 4000 family, a single eight-input AND/NAND chip has this internal layout. The inverted output from the NAND gate becomes an AND output from pin 1 of the chip.

Figure 10-30. The internal layout of a 14-pin 4069B hex inverter logic chip, containing six inverters. This layout is the same as for the x74x04x chip.

Although the 4000 series is now more than 40 years old, it may still be useful where a 5VDC power supply is not required for other reasons in a circuit and would be added purely to power a 74xx series logic gate or other digital chip. If a circuit contains a 9VDC or 12VDC relay, for in- stance, a Darlington pair may be used with that voltage to drive the relay, and an old-school 4000 series logic chip could share the same supply. The relay coil would need a clamping diode to pro- tect the logic chip from transients.

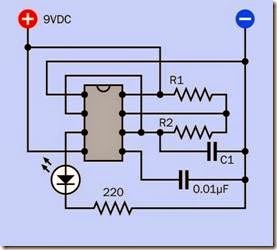

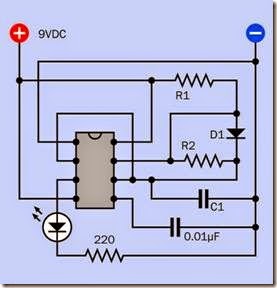

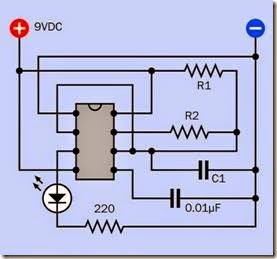

Applications

The output from a logic chip may be used as an input for a microcontroller, to enable multiple inputs to share one pin. An eight-input NAND gate, for instance, could combine the inputs from eight normally on motion sensors. If just one sensor responds to an intrusion, the gate output would change from high to low.

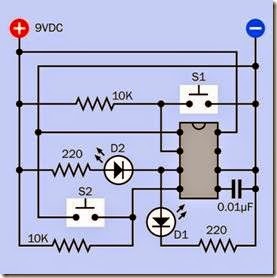

Logic gates may be useful in any simple device that has to respond to a single, specific combination of inputs. A digital combination lock is one example; games of chance are another. Most simple dice simulations use logic gates to convert the output from a counter to drive a dice- pattern of LEDs.

A logic gate may be used as an interface between an electromechanical switch and a circuit containing digital chips. A 10K pullup or pulldown resistor prevents the gate input from floating when the switch is open. A buffer can be used for this purpose, or an inverter, or any “spare” gate on a logic chip that is already in the circuit. One input of the chip can be tied to the positive power supply or negative ground, to create an appropriate input from the chip when the switch, attached to the other input, is opened or losed.

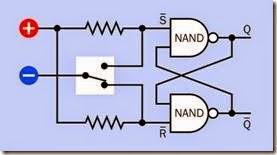

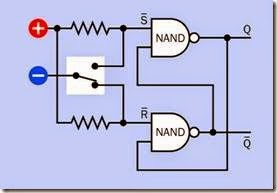

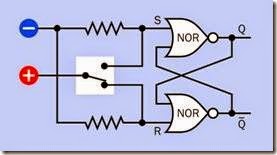

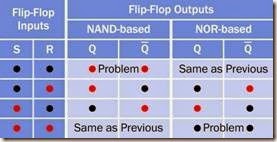

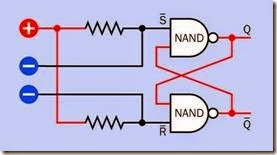

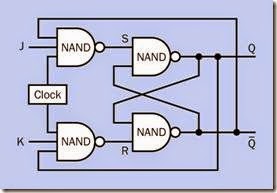

A jam-type flip-flop can be used to debounce a switch input. See Chapter 11 for details. If two NOR or two NAND gates are unused in a circuit, they can form a flip-flop.

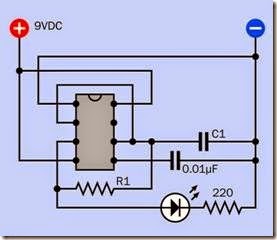

In the original CMOS 4000 family, a positive out- put may be capable of driving an LED if the cur- rent does not exceed 5mA with a power supply of 5VDC or 10mA with a power supply of 10VDC. Note that the output voltage will be pulled down significantly by these loads. In the 74HCxx family, chips can source or sink as much as 20mA, but here again the output voltage will be pulled down. Note that the total limit for all outputs from a 74HCxx chip is around 70mA.

The output from a logic chip can be passed through a buffer such as the 7407, which has an open-collector output capable of sinking as much as 200mA. This enables direct drive of modest loads, so long as they are not inductive.

Solid-state relays and optocouplers can be driven directly from logic chips, as they draw very little current. A solid-state relay can switch 50A or more.

What Can Go Wrong

Two problems are common when using CMOS digital chips: damage from static electricity, and erratic behavior caused by floating pins.

Static

The early 4000 series CMOS chips were especially vulnerable, but more recent CMOS designs generally include diodes at the inputs, which reduces the risk. Still, logic chips should be protected by inserting them into anti-static foam or enclosing them in conductive wrappers until they are in- stalled in a board. While handling chips, it is good practice to be grounded, ideally using a wrist- mounted ground wire.

Floating Pins

Any pin which is unconnected in a logic chip is considered to be “floating,” and can pick up signals by capacitive coupling, possibly disrupting the behavior of the chip and also causing power consumption, as the ambiguous pin state will tend to prevent that gate in the chip from enter- ing quiescent mode.

Generally speaking, input pins in a TTL logic chip that are not being used for any purpose should be tied to the positive voltage supply, while un- used CMOS pins should be tied to negative ground.

Family Incompatibilities

As previously noted, older TTL logic chips may deliver a “high” output voltage that is lower than the minimum expected by newer CMOS logic chips. The best option is not to mix families, but if chips are stored carelessly, some intermingling can occur. Part numbers should be checked if one chip appears to be ignoring output from another.

Overloaded Outputs

If a circuit calls for a logic chip with an open- collector output, and a regular chip is used by mistake, it will almost certainly be damaged.

Output Pulled Down

If the output from one logic chip is connected with the input of another logic chip, and if the output from the first chip is also connected to an LED, the LED may pull down the output voltage so that the second chip will not recognize it as a high state. As a general rule, a logic output can drive an LED, or can drive another logic chip, but not both. Very-low-current LEDs, which draw as little as 2mA, may be acceptable.

Incorrect Polarity and Voltages Logic chips can be knocked out by applying in- correct polarity, or voltage to the wrong pin, or the wrong voltage. Modern logic chips tolerate a very limited voltage range, and a 74xx series chip will be irrevocably damaged if it is used where a 4000 series chip was specified for a power supply higher than 6VDC.

If a chip is inserted upside-down, it will probably be damaged when voltage is applied.

Bent Pins

Like all through-hole chips, DIP logic chips can be inserted accidentally with one or more pins bent underneath the chip. This error is very easy to miss. The bent pins will not make contact with any socket that is used, and the chip will behave unpredictably. Check for proper pin insertion with a magnifying glass if necessary.

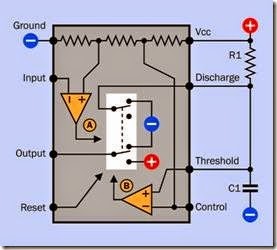

Unclean Input

Logic chips expect a clean input without voltage spikes. A 555 timer of TTL type generates spikes in its output which can be misinterpreted as multiple pulses by the input of a logic chip. A CMOS- type 555 timer is more suitable for connection with logic chips.

If a pushbutton, rotational encoder, or electro- mechanical switch provides a high or low input, the input must be debounced. In hardware, this is traditionally done with a flip-flop. It can also be done with code in a microcontroller.

Analog Input

The input of a logic chip can be connected directly with a thermistor, phototransistor, or similar analog component, but only if there is some certainty that the voltage at the input pin will remain within the range that is acceptable to the chip. In the case of a phototransistor, for example, it should be exposed to a limited, known range of light intensity.

In general, it is best to avoid applying intermediate-voltage signals to a digital logic input, as they can create unpredictable output, or output of an intermediate voltage. A comparator can be placed between the analog source and the digital logic chip, or a logic chip with a Schmitt-trigger input can be used.