FET Bias

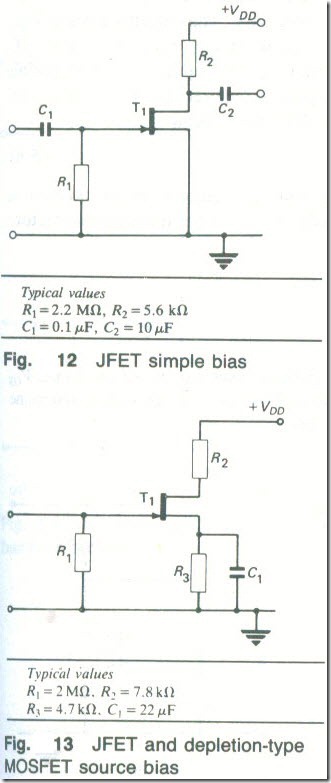

The drain characteristics shown in Fig. 13 show that a JFET is conducting when the gate-source voltage VGS is zero. The simplest method of biasing an n-channel JFET is therefore that given in Fig. 12. The disadvantages are (a) the maximum input signal amplitude must be very small if excessive distortion is to be avoided, and (b) no stabilization against changes in the d.c. drain current is provided.

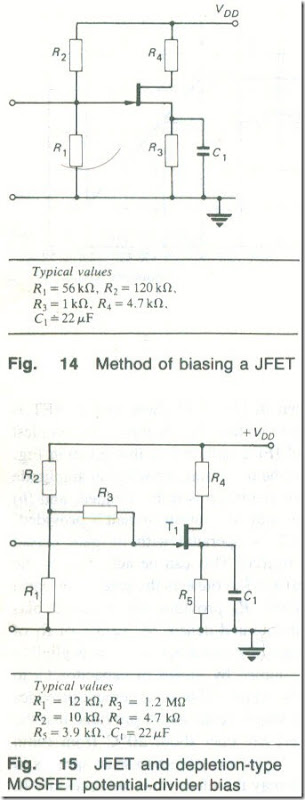

Normally an n-channel JFET is operated with its gate biased negatively with respect to its source. This can be achieved by the circuit shown in Fig. 13 Resistor R1 connects the gate to the earth line and the voltage drop across R3 provides the required bias voltage. The gate current is minute and hence, for values of R1 of a megohm or so, the d.c. voltage developed across R1 is negligibly small. Resistor R3 is often decoupled by means of capacitor C1 to prevent negative feedback of the signal. This arrangement provides adequate doc. stability for most small-signal stages provided that the temperature variation is not greater than about 200C from room temperature. JFETs of the same type are subject to wide spreads in some of their parameters and it may therefore often be necessary to use the more effective bias circuit of Fig. 14, which operates in similar fashion to the circuit shown in Fig. 9.

Improved stabilization of the drain current can be achieved if another resistor R2 is connected between the drain supply voltage and the gate terminal (Fig. 14). RI and R2 form a potential divider across the drain supply voltage to keep the gate potential constant. The gate source voltage VGS is the difference between the potentials of the gate and the source. If the drain current should increase for some reason, the voltage across R3 will increase and this will make the gate potential more negative relative to the source potential. VGS will then be more negative and the drain current will fall, tending to compensate for the original increase in its value.

If the junction of the bias resistors R1 and R2 is directly connected to the gate terminal of the FET then, at all signal frequencies, the bias resistors will effectively appear in parallel with the input terminals of the device. The high input resistance of the FET will then be reduced to a considerably smaller value. To minimize this shunting effect, a resistor R3 can be used to connect the bias resistors to the gate terminal as shown in Fig. 6.15. The input resistance of the amplifier is then equal to

R3 + R1R2/(R1 + R2) (6.5)

R3 is chosen to be 1 MΩ or more and hence the input resistance is approximately R3.

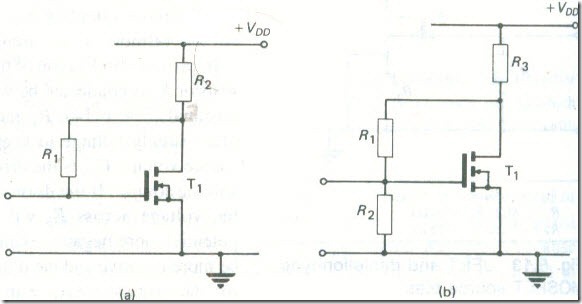

An a-channel depletion-mode MOSFET must be biased so that its gate is held at a negative potential relative to its source and hence either of the bias circuits shown in Figs. 14 and .15 can be employed. An n-channel enhancement-mode MOSFET must be operated with its gate at a positive potential with respect to its source and so a different bias circuit is necessary. The circuit shown in Fig. 16(a) can be used if the operating point VGS = VDS is suitable. If, for reason of obtaining maximum output voltage or minimizing distortion, some other operating point is required then the circuit given in Fig. 16(b) must be used. With this circuit

VGS = VDSR2/(R1 + R2) (6.6)

Both circuits provide d.c. stabilization of the operating point in a similar manner to that previously described for transistor collector base bias.

Example 6

In the circuit of Fig. 16(b) the operating point is to be at ID = 2 mA, VGS = 2.5 V, and VDS = 4 V. If the drain supply voltage is 9 V determine suitable values for the three resistors.

Solution

I DR3 = 9 – 4 = 5 V

R3 = 5/(2 X 10-3) = 2.5 kΩ. Nearest preferred value

= 2.4 kΩ (Ans.)

2.5 = 4R2/(RI + R2), 1 + RI/R2 = 4/2.5 = 1.6

R1 = 0.6R2

The chosen values should be fairly large to keep a high input resistance.

If R2 = 200 kG then R1 = 120 kΩ (Ans.)