Synchronous Counters

Each of the counter circuits described so far has been a non-synchronous or ripple counter. Each flip-flop, other than FFA, cannot change state until the preceding flip-flop has changed state from 1 to 0, An input pulse appears to ‘ripple’ through the circuit and there is a cumulative delay in operation. Faster operation can be obtained if all the flip-flops can be made to change state simultaneously. A synchronous counter has all the flip-flop clock terminals connected together and to the input terminal so that all stages change state at the same instant.

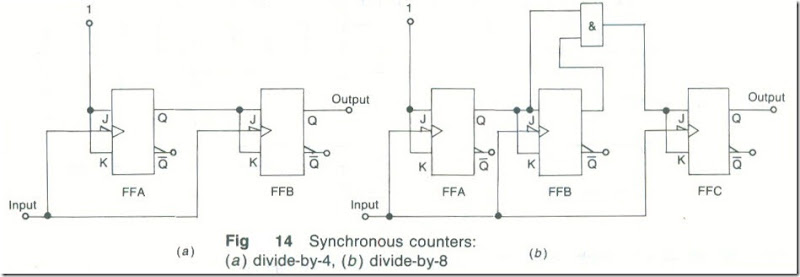

Figs. 14(a) and (b) respectively show synchronous divide-by-4 and divide-by-8 counters.

The operation of the divide-by-8 counter is as follows. Assuming dial all three flip-flops are initially reset the trailing edge of the first input pulse toggles FFA so that QA = JB = KB = 1. The next input pulse toggles both FFA and FFB to give QA = JB = KB = 0, QB = 1. Since QA = 0 the output of the AND gate is 0 and so are Jc and Kc. A third input pulse only makes FFA toggle. Now QA = JB = kb = qb = 1 and since both inputs to the AND gate are now 1 its output is also 1. Therefore, Jc = Kc = 1. The fourth input pulse makes all three stages toggle and produces the counter state QA = qb = 0, Qc = 1, This means that JB = KB = Jc = Kc = 0 and so a fifth input pulse will toggle FFA only. The operation of the counter follows this sequence until an eighth input pulse is received; this will reset all the flip-flops and clear the circuit.

Reducing the Count

The maximum number of states which an «-stage counter can take up is equal to 2n. The count can be reduced to less than 2n in a number of different ways that are beyond the scope of this book.

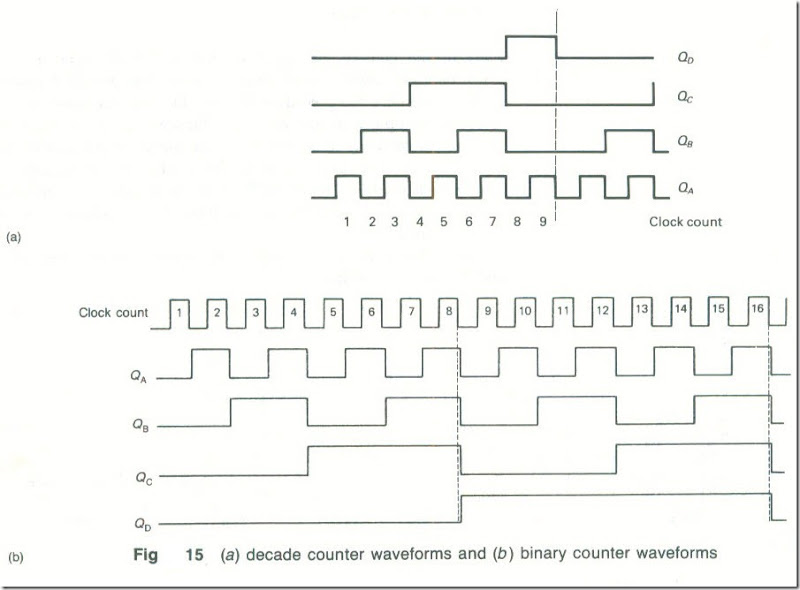

A decade counter counts a sequence often numbers from 0 through to 9. When the count is 9 the counter resets to return its count to 0. The waveforms at the four outputs of a decade counter are shown in Fig. 15(a). A binary counter counts a sequence of binary numbers ranging from 0 to 2n where n is the number of stages in the counter. For a 4-bit counter n = 4 and the count is 0 to 15. Figure 15(b) shows the output waveforms of a 4-bit binary counter.

Example 1

(a) Determine the time taken for the decade counter to generate the count sequence if the clock period is 0.1 ms. (b) Determine the period and the frequency of each of the outputs QA, QB, Qc and QD in Fig.15(b) if the clock period is 0,1 ms.

solution

(a) There are 10 pulses so time taken is 1 ms (Ans.)

(b) QA: period = 0.2 ms, frequency = 5 kHz (Ans.)

QA: period = 0.4 ms, frequency = 2.5 kHz (Ans.)

Qc: period = 0.8 ms, frequency = 1.25 kHz (Ans.)

QD: period = 1.6 ms, frequency = 625 Hz (Ans.)

Table.5 |

||||||

|

Non-synchronous counters |

||||||

|

7490 |

Decade |

Up |

||||

|

7492 |

Modulus 12 |

Up |

||||

|

7493 |

Binary |

Up |

||||

|

Synchronous counters |

||||||

|

74160 |

Decade |

Up |

non-synchronous clear |

|||

|

74161 |

Binary |

Up |

synchronous clear |

|||

|

74162 |

Decade |

Up |

synchronous clear |

|||

|

74163 |

Binary |

Up |

synchronous clear |

|||

|

74190 |

Decade |

Up/down |

non-synchronous load |

|||

|

74191 |

Binary |

Up/down |

non- synchronous load |

|||

|

74192 |

Decade |

Up/down |

load/clear |

|||

|

74193 |

Binary |

Up/down |

load/clear |

|||

Integrated Circuit Counters

A number of IC counters are available in the various logic families. As an example, some of the more commonly employed TTL counters are listed in Table .5. The counters can be cascaded for applications that require more than four stages. An IC counter is provided with non-synchronous inputs that allow it to be preset to an initial value other than zero, or allow the counter to be reset back to zero at any time.